Nmos and cmos fabrication

-

Upload

bheemsain-chhimpa -

Category

Business

-

view

8.680 -

download

1

Transcript of Nmos and cmos fabrication

1

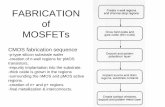

FABRICATION

22SCHEMATIC CROSS SECTION OF

MOSFET

3

Create N-well (for PMOS devices) & Channel Stop Regions

Grow Field & Gate Oxide

Deposit & Pattern Poly Layer

Implant S, D & Substrate Contacts

Create Contact Windows

Deposit & Pattern Metal Layer

Impurity Implant Into The Substrate.

Thick Around The nMOS And pMOS Active Regions And Thin Respectively Through Thermal Oxidation.

Creation Of n+ And p+ Regions.

Metallization

4

PHOTOLITHOGRAPHY

• IC Is Set Of Patterned Layers Of Doped Silicon, Polysilicon, Metal And SiO2.

• All Areas Are To Be Defined By Proper Masks.

• A Layer Must Be Patterned Before Another Is Applied On The Chip.

• Every Layer Will Undergo Lithography With Different Mask.

Si Substrate

SiO2 layer by thermal oxidation

Unpatterned Structure

Si Substrate

SiO2SiO2

Patterned StructurePhotolithography

5

Si Substrate

Si Substrate5-200 nm SiO2 layer by thermal oxidation

Si Substrate

Light Sensitive, Acid Resistant compound

= Photoresist

Si Substrate

UV Light

Insoluble Photoresist

Soluble Photoresistv

Glass Mask

Si Substrate

Hardened Photoresist

Chemical or Dry Etch

Si Substrate

Hardened PhotoresistSiO2 Window

reaching down to Si substrate

Si Substrate

Hardened photoresist removed by stripping solvents.

Obtained Patterned SiO2 feature on the Si Substrate

For High Density Patterns Required In Sub Micron Devices, E-beam Lithography Is Used Instead Of Optical Lithography.

6

Fabrication of nMOS: Basic steps

Si Substrate

Si SubstrateThick Oxide

layer

(field oxide)

Si Substrate

Si Substrate

Thin high quality Oxide

Layer

(gate oxide)

OXIDATION

SELECTIVE ETCHING FOR DEFINING ACTIVE AREA ON WHICH

MOSFET WILL BE FABRICATED

Si Substrate

Deposition of polysilicon

(gate + interconnect medium)

Si Substrate

Patterned and etched

polysilicongate oxideoxide

7

8

Si Substrate

Patterned and etched

polysilicongate oxideoxide

Fabrication of nMOS: Basic steps

Bare Si surface to form S & D

polysilicongate oxideoxide

n+ n+

n+ n+

Doping : Diffusion or ion implantation

(high concentration of impurity atoms)

Insulating oxide

n+ n+

Patterned and etched

Contact windows for D & S

9

Fabrication of nMOS: Basic steps

n+ n+

n+ n+

Evaporated Aluminum

Patterned and etched

Metal contacts

By creating another insulating oxide layer, cutting contact holes (via), depositing and patterning metal, two more layers of metallic interconnects can also be added on the top of this structure.

10

• Electrical isolation on a single chip containing many devices is necessary

• To prevent undesired conducting paths;• To avoid creation of inversion layers outside the

channels;• To reduce leakage currents.

CHALLENGES:

11

I) ETCHED FIELD OXIDE ISOLATION:

Devices are created in dedicated regions called active areas.

Each active area is surrounded by thick oxide barrier called field oxide.

Thick oxide is grown on complete surface of the chip and then selectively etched to define active areas.

Straight forward method.

Thickness of oxide leads to large oxide steps at the boundaries of active areas and isolation regions.

May lead to chip failure due to cracking of deposited layers due to large height difference at the boundaries.

DEVICE ISOLATION TECHNIQUES:

12

DEVICE ISOLATION TECHNIQUES:II Local oxidation of silicon

13

LOCOS technique is based on the principle of selectively growing the field oxide in certain regions , instead of selectively etching away active areas after oxide growth.

For selective growth of oxide, active areas are covered with Silicon nitride.

14

DEVICE ISOLATION TECHNIQUES:LOCOS

Si Substrate

Si3N4

Thin PAD OXIDE

(stress relief oxide)

Protects Si surface from stress caused by nitride during subsequent process steps.

(Patterned and etched)

(Doping of exposed Si surface with p type impurity)

Si Substrate

p+ p+p+

Si3N4Si3N4

Isolation Regions

(Channel stop implants)

Si Substrate

15

Si Substrate

p+p+ p+

Lateral extension under nitride layer

Si3N4 Si3N4 Thick Field Oxide which partially

recesses into Si substrate

Bird’s beak

** Reduces active area

Si Substrate

p+p+ p+

THE ACTIVE AREAS

(Patterned and etched)LOCOS is popular :

More planar surface topology

Bird’s beak encroachment can be reduced up to some limit

by device scaling

16

III) MULTILEVEL INTERCONNECTS & METALLIZATION:

• 4 to 8 metal layers are used to create interconnections between the transistors and for routing the power supply, signal lines and clock lines on the chip surface.

• Allows higher integration densities.

• Adds to the third dimension.

• Electrical connections between the layers are made by vias.

• Each via is formed by creating an opening in isolation oxide before every metallization step and filling it with a special metal plug (Tungsten).

• After creation of via, new metal layer is deposited and subsequent patterning is done.

DEVICE ISOLATION TECHNIQUES:

17

18

19

20

21

SOME FACTS:• Due to various process steps chip surface is highly

nonplanar.• . It may inhibit local thinning and discontinuities at uneven

surface edges• Deposition of multiple metal interconnect lines is not

desirable on such irregular topography.• They will lead to hills and valleys on the chip surface.• Hence surface is usually planarised before every new

metal deposition step.• For this, a fairly thick SiO2 layer is grown on the wafer

surface to cover all existing surface nonuniformities.• Its surface is then planarised by any one of:Glass reflow (heat treatment),Etch back,Chemical mechanical polishing (CMP).CMP: Actual polishing of wafer surface using abrasive silica

slurry.Adopted in recent years.

22

EXERCISE:*Epitaxial layer

** Difference between ion implantation and diffusion processes of doping.

*** Design masks for all patterning and etching steps in the fabrication of nMOS transistor for positive and negative photoresist material.

![CMOS Fabrication [Compatibility Mode]](https://static.fdocuments.in/doc/165x107/577cdf861a28ab9e78b17027/cmos-fabrication-compatibility-mode.jpg)