EDN Design Ideas 2005

description

Transcript of EDN Design Ideas 2005

-

www.edn.com January 6, 2005 | edn 63

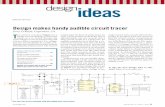

ideasdesignEdited by Brad Thompson

Laser diodes can destroy themselvesin a few nanoseconds, so testing theresponse and stability of a feedback-stabilized laser-diode driver can be ex-pensive. The simulator circuit in Figure1 shows a typical laser-diode package,which contains not only the diode, whichis driven by current I

L, but also a

photodiode. The laser diodes frontfacet emits a main beam that goes towork in the outside world, and the rearfacet emits a reference beam that falls onthe photodiode.

Although much weaker than the mainbeam, the reference beams power is di-rectly proportional to the main beam, asis the current, I

P, that produces the pho-

todiode. Connecting the photodiodeback to the laser-diode driver via a care-fully designed amplifier completes afeedback loop that should hold themain beam power stable and con-stant. Ensuring that the laser diode nev-er sustains a destructive overload underany conditions is the tricky part.

A laser diode exhibits a current thresh-old, or knee, below which its emissionis weak and incoherent, as is photocur-rent I

P. Above the knee, laser action oc-

curs, and the optical output and pho-tocurrent rise linearly with increasingdrive current.

A simulator must reflect these charac-teristics, and the circuit in Figure 2 com-

prises a basic voltage-controlled currentsource that presents a threshold. Based ona TO-92 or E-line-packaged PNP transis-tor and two resistors and packaged in ablob of epoxy, the simulator takes the placeof the laser diode until circuit operationis stable. Its easy to build several modulesto emulate laser diodes of various ratings.

In operation, the laser driver sinks cur-rent I

Land develops a voltage, V

S, across

R1. When V

Sexceeds Q

1s V

BE, Q

1con-

ducts and sources a simulated photocur-rent, I

P, into the feedback-control cir-

cuitry. As IL increases, I

Pincreases linearly

in proportion.As a design example, consider an av-

erage laser diode with a threshold current(I

TH) of 10 mA, an operating current at

full optical output (ILMAX

) of 30 mA, anda photocurrent of 100 A at full power.R

1must then equal V

BE/I

TH,or 560 mV/10

mA and thus yields a value of 56 for R1.

Then, R2

equals ((ILMAX

R1)V

BE)/I

PMAX,

or approximately 11 k. Using a value of

560 mV for VBE

produces the best practi-cal relationship between I

L and I

P.

Inverting the transistorthat is, swap-ping Q

1s collector and emitter connec-

tions produces a more abrupt conduc-tion-threshold voltage of approximately500 mV but decreases the slope of I

P ver-

susIL. In this example, inverting the tran-

sistor requires lowering the value of R2

to approximately 7.5 k.The inverted-transistor circuit provides

a sharper threshold and thus more real-istic simulation, even though it may re-quire some experimentation with resistorvalues for optimal performance. You canuse almost any PNP bipolar-junctiontransistor for Q

1, such as a ZTX502, and

decreasing R2

by 30% renders IP

within5% of the desired nominal value of I

P.

Note that laser diodes characteristicsvary widely, even within a batch, so us-ing preferred-value resistors for R

1and R

2

makes little practical difference in per-formance. Laser diodes exhibit a typicalforward-voltage drop of about 2V, andthe simulator circuit should thus drop nomore voltage at full current. Also, thesimulator circuit responds more slowlythan a laser diode, but, if the feedback cir-cuitry operates even more slowly, as itusually does, the simulators slow re-sponse presents no problem.

A simulator for an N-type laser dioderequires an NPN transistor and reversalof connections. More complex laserdiodes may require more elaborate cir-cuitry that includes current mirrors andadditional connections. If adequate pow-er-supply voltage is available for current-source compliance, you can connect anLED in series with the I

Llead to provide

a visual indication of circuit operation.Connecting an oscilloscope across R

1 al-

lows monitoring laser-drive and modu-lation currents. (In this context,N-andP-type refer not to laser-diode-devicediffusions but to the polarity of the com-mon terminal.)

MAINBEAM

LASERDIODE

REFERENCEBEAM

PHOTODIODE

IL IP

COMMON V

F igure 1

Laser simulator helps avoid destroyed diodesNick Cornford, Berkhamsted, Hertfordshire, UK

A P-type-laser diode assembly includes thephotodiode power sensor.

R1

IL IP

COMMON V

R2

Q1

ALTERNATIVEORIENTATION

FOR Q1

A laser-diode simulatorrequires only one transistor.

F igure 2

Laser simulator helps avoid destroyed diodes ................................63

Differential driver doubles as versatile RF-switch driver ........................64

Pseudologarithmic thermistor signal conditioning spans wide temperature range ..............................66

RF telemetry transmitter features minimal parts count ......................................68

Publish your Design Idea in EDN. See theWhats Up section at www.edn.com.

The best ofdesign ideas Check it out at:www.edn.com

-

64 edn | January 6, 2005 www.edn.com

ideasdesign

Designed as a high-speed driver for12-bit ADCs, the AD8137 controlsSPDT GaAs (gallium-arsenide)FET-MMIC (microwave-monolithic-IC)and PIN-diode RF switches and thus pro-vides a low-cost and versatile alternativeto conventional switch drivers. This cir-cuit achieves typical switching speeds ofapproximately 7 to 11 nsec, including thepropagation delays of the driver and RFload.

The GaAsFET-driver circuit(Figure 1) converts a single-end-ed, 0 to 3.5V TTL signal into a comple-mentary, 0 to 4V differential-outputsignal. The divider formed by the 50source impedance, R

S, and the input ter-

mination, RT, imposes a 50% signal re-

duction. To compensate, the circuit am-plifies its input by approximately 2.3times to yield the proper output ampli-tude of 4V p-p. The circuit also shifts theoutput level by 2V to provide the prop-er GaAsFET bias. Equation 1 determinesthe output voltage:

For a symmetrical output swing, gain-setting resistors R

1and R

4must present

the same Thevenin-equivalent resistance.In Figure 1, R

4increases by 20 over R

1.

This increase compensates for the factthat source resistor R

S and termination

resistor RT

combine in parallel to intro-duce additional resistance of 25. SettingR

4to 1.02 k (the closest standard value

to 1.025 k) ensures that the circuit willprovide approximately equal gains at thedifferential outputs.

The AD8137s VOCM

input (Pin 2) of-fers a convenient method of shifting theoutputs dc common-mode level. In Fig-ure 1, R

2and R

3form a voltage divider,

which sets the dc output level to 2V.Connecting the AD8137s inverting inputto a reference voltage of 1.75V establish-es the midpoint of the input signal andallows for proper switching of theAD8137s input stage.

Figure 2 shows the GaAs FET driversturn-on switching speed of approximate-ly 5 nsec for isolation to insertion lossthat is, 50% of the TTL input to 90% de-tected RF. Figure 3 shows turn-offswitching speed of approximately 11 nsecfor insertion loss to isolationthat is,50% of the TTL input to 10% detected RF.

As Figure 4 shows, with only minormodifications, the GaAs switch-drivercircuit can drive PIN-diode loads that re-quire both positive and negative bias cur-rents. IC

1s V

OCMinput connects to

ground to provide symmetrical outputsof 63.5V about ground and sinks andsources 10 mA of bias current. Altering

A1/B2

A2/B1

C510 pF

C610 pF

C915 pF

C815 pF

C715 pF

MASW20000IC2

RF

RF2

RF1

RF SECTION

_

+ 5

PULSE GENERATOR

RS50

R11k

R23k

R32k

RT50

C30.1 F

5VC12.2 F

82

1

3

46

R52.32k

C22.2 F

5V

5V

R62.32kR4

1.02k

C40.1 F

IC1

VREF

AD8137

F igure 1

Differential driver doubles as versatile RF-switch driver John Ardizzoni, Analog Devices, Wilmington, MA

ADC IC1 converts TTL levels todifferential-control signals forGaAs RF switch IC2.

Vertical cursors denote GaAs switch turn-ontime of approximately 5 nsec.

F igure 2 Turn-off time is approximately 11 nsec.F igure 3

(1)

-

66 edn | January 6, 2005 www.edn.com

ideasdesign

feedback resistors R3

and R4

to 2 kV pro-vides an output swing of 63.5V. ResistorsR

5and R

6set the steady-state PIN-diode

current, ISS

, as Equation 2 shows:

Capacitors C5

and C6

set the spikingcurrent I

S, which removes stored charge

in the PIN diodes. You can optimize agiven diode switchs responsetime by using the AD8137s out-put slew rate for dV/dt and Equation 3,

to calculate spiking current.

_

+ 5

PULSE GENERATOR

RS50

R11k

RT50

C30.1 F

5VC12.2 F

82

1

3

46

R32k

C22.2 F

VO

VO

5V

R42kR2

1.02k

C522 pF

R6280

VD

VD

R5280

C622 pF

C40.1 F

IC1

VREF1.75V

TO PINDIODESAD8137

F igure 4

A few modifications convertthe circuit in Figure 1 into aPIN-diode switch driver.

Given its low cost, small size, ro-bust construction, accuracy, versa-tility and sensitivity, its no wonderthat the thermistor rates as one of themost popular temperature sensors avail-able. However, in some applications, athermistor can exhibit too much sensi-tivity for wide-range temperature meas-urements. For example, when you com-bine a thermistors radically nonlinearexponential resistance-versus-tempera-ture-response curve with a linear signalconditioner (Reference 1), the resultantgraph resembles a difficult-to-character-ize response, as Trace A shows (Figure 1).

Note that most of the thermistors re-

sistance range crowdsinto a small spanof temperatures atthe lower limit of therange. As Curve B in Fig-ure 1 shows, the changeof resistance per degreeof temperature changelooks exaggerated at lowtemperatures.As temper-ature increases, the reso-lution diminishes andmay become inadequateat the upper end of thetemperature scale.

In contrast, the signal-conditioning circuit inFigure 2 mitigates thethermistors inherent nonlinearity bygenerating a compensating, pseudologa-rithmic response function thats Curve Cin Figure 1 represents. The followingequation relates the circuits 10V out-put span for an ADC 10V input span tothermistor resistance: Thermistor resist-anceR

4(V

O10)/(102V

O).

Curve D in Figure 1 shows the result-ant resolution curve. Maximum resolu-tion occurs at a temperature that corre-sponds to a thermistor resistance equal toR

4and an output voltage of 0V. Although

selection of this value optimizes resolu-tion in the middle of the measurementrange, the thermistors nominal resist-ance is relatively noncritical.You can alsoselect a different value of reference volt-age, V

REF, to shift the 10V output span

to meet other requirements. For best per-formance, you can share the same refer-ence source for V

REFand for the meas-

urement systems ADC, which makesmeasurements ratiometric and thus in-sensitive to reference-voltage drift.

In addition to resolution, span, and

TEMPERATURE

BLINEAR-RESOLUTION CURVE

ARUST

CUR

VES

A AN

D C

RES

ISTA

NCE

CPSUEDOLOGARITHMIC

RESPONSE

DPSUEDOLOGARITHMIC

RESOLUTION

Pseudologarithmic thermistor signal conditioningspans wide temperature rangeStephen Woodward, University of North Carolina, Chapel Hill, NC

These resistance-versus-tem-perature curves highlight the improved resolu-tion available in a pseudologarithmic circuit.

+

IC1

R333.2k1%

R424.9k1%

R124.9k1%

C10.1 F

C20.1 F

VREF2.5V

R2100k1%

THERMISTOR

F igure 2

This pseudologarithmic thermistor signal conditioner uses a sin-gle operational amplifier and a few passive components.

F igure 1

(2)

(3),

-

68 edn | January 6, 2005 www.edn.com

ideasdesign

reference-drift considerations, thermis-torsand, for that matter, all tempera-ture sensorsexperience self-heating ef-fects. The excitation current producesohmic power that causes these effects.The limited thermal mass of miniaturethermistors provides limited heat dissi-pationoften only a few microwatts per

degreeand that dissipation can pro-duce especially severe temperature shifts.

In the circuit in Figure 2, the powerdissipated due to thermistors self-heat-ing reaches a maximum at midspanthat is, when output voltage is 0V andequals: V

REF2/(4R

4)63 W for the

component values illustrated. For all but

the smallest thermistors, this level of self-heating produces acceptably low frac-tional-degree errors.

Reference1. Woodward, Steve,Optimize linear-

sensor resolution, EDN, March 7, 2002,pg 131.

Requirements for portable, short-range telemetry systems frequentlyinclude low power consumption,small size, and low cost. The circuit in Fig-ure 1 meets these criteria and uses onlythree off-the-shelf ICs and a few passivecomponents. Although dedicated to con-ditioning the low-level signal a strain-gauge bridge produces, the circuit can op-erate with almost any resistive transducerbased on a Wheatstone bridge. The circuitcomprises a VFC (voltage-to-frequencyconverter) that produces a PPM (pulse-position-modulation) output, and anOOK (on/off-keyed) RF transmitter.Based on direct digitization, the VFC inFigure 1 comprises IC

1, IC

2, IC

3A, and

IC3B

. A Wheatstone bridge containingstrain gauge R

Xproduces an output of ap-

proximately 5 mV. An integrator stagecomprising C

6and IC

1, a Linear Technol-

ogy LTC1250 offset-compensated, low-

drift operational amplifier, connects di-rectly across the bridge. (Note that the val-ue of the remaining resistors in the bridgedepends on the application.)

To yield a ratiometric conversion, thevoltage applied to the bridge, V

COMP,

varies with power-supply voltage andequals the difference between the twothreshold voltages of a Schmitt-triggercircuit. In Figure 1, the Schmitt triggercomprises a Maxim MAX9075 compara-tor, IC

2; a CMOS inverter, IC

3A; and the

positive feedback network comprising R1,

R2, and C

1. Equations 1 and 2 define the

Schmitt triggers high, VTH

, and low, VTL

,threshold voltages:

To understand the circuits operation,assume that the comparators output ishigh and, consequently, the inverters out-put is low. Also assume that the seriescombination of the strain gauge, R

X, and

the trimmer, RT, is always equivalent to

R(1X)R. That is, for linear operation,the sensors resistance variation representsa small fraction of the arm resistance.

Under these conditions, the nonin-verting input of IC

1biases to V

DD/2, and

the Wheatstone bridges active arm drivesa positive current, I

I, into the summing

node of IC1. This current causes the in-

tegrators output, VOI

,to ramp down to-ward the low threshold voltage, V

TL, of

the Schmitt trigger.When V

OIV

TL, the comparators out-

put goes to zero, and the inverters out-put consequently rises to V

DD. This ac-

tion inverts the direction of theintegrators input current, causing the in-

+_

R

RX

RT

R

R

IC1IC3A IC3B

IC3C

VCOMP

R1100k

C66.8 nF

VINV

C115 pF

VOI

R2

VCOMP

R3330

C2100 pF

R4

PPMOUT

VINV

VDD

VPPM C318 pF

C418 pF

C51 nF

VDD4V

SPIRALANTENNA

L180 nH

_

+

+IC2_

RF-telemetry transmitter features minimal parts countFrancis Rodes, Eliane Garnier, and Olivier Chevalerias, ENSEIRB Talence, France

Thise RF-telemetry transmitter and strain-gauge amplifier use only three ICs.

(1)

(2)

F igure 1

-

70 edn | January 6, 2005 www.edn.com

ideasdesign

tegrators output to ramp up-ward to the Schmitt triggershigh threshold voltage. Final-ly, when V

OI= V

TH, the com-

parators output goes high,and the above sequence re-peats indefinitely, producing afree-running oscillation inwhich the integrators outputramps up and down betweenthe threshold voltages of theSchmitt trigger (Trace 1 inFigure 2). Meanwhile, thecomparators output andthe inverters output delivertwo square waves with a 50%-duty-cycle ratio (traces 2 and3, respectively, in Figure 2)that drive the bridge.

To produce the PPM signal (Trace 4 inFigure 2), the inverters output drives amonostable circuit comprising a secondinverter, IC

3B, and timing components R

4

and C2, which produces a 15-sec-wide

pulse. Current-limiting resistor R3

pre-vents latch-up of IC

3, and R

2and C

4 set

the output-pulse width.To model the VFCs transfer function,

calculate period TX

of the comparatorsoutput. Due to the symmetry of IC

1s

output, this period is twice the time theintegrators output takes to ramp linear-ly between the two threshold voltages ofthe Schmitt trigger. Consequently, youcan express t

Xas in Equation 3:

where dVOI

/dt is the slope of the ramp atthe integrators output. Assuming thatthe integrators input current is constantduring one period, Equation 4 gives theslope:

After applying a Thevenin transfor-mation of the bridges active arm, you canexpress the integrators input current as

Replacing VTL

, VTH

, and dVOI

/dt in Equa-tion 3 with the respective expressions

from equations 1, 2, and 4 finally yieldsthe frequency in Equation 6.

Knowing that X1, you can approxi-mate the PPMs output frequency byEquation 7:

This transfer function highlights theVFCs three most important features: thatthe modulation frequency, f

X, is directly

proportional to the relative variation ofthe bridges sensor resistance, R

X; that the

modulation frequency is independent ofthe power-supply, V

DD; and, therefore,

that this PPM converter is ratiometric.This feature is attractive for any portable-system application in which the supplyvoltage decreases as the battery ages. Themodulation frequency is independent ofthe PPM pulse width, which eliminatesthe source of error you typically en-counter with single-slope VFCs.

Using the components values shown inFigure 1, the converters frequency spanis: 200 HzF

X600 Hz for a relative vari-

ation of the strain-gauge resist-ance:4.2103R/R4.2103.Consequently, with zero force applied tothe strain gauge, R/R0, and the con-verter produces a 400-Hz modulationfrequency. The waveforms in Figure 2correspond to this case.

To transmit data over a distance of afew meters, the PPM signal modulates an

80-MHz OOK RF transmit-ter. This transmitter com-prises an interruptible Col-pitts oscillator based on avery-high-speed CMOSNOR gate, IC

3C; a 74VHC-

02; and a tank circuit com-prising two identical feed-back capacitors, C

3and C

4;

and a square-spiral pc in-ductor, L. To obtain reliableoscillation start-up, setC

3C

4C. Neglecting the

effects of stray capacitances,you can calculate the outputfrequency of the Colpitts os-cillator via Equation 8:

The values of L, C3, and C

4shown in

Figure 1 produce a carrier frequency, fC,

of approximately 80 MHz. Inductor L1

also doubles as the transmitters antenna,and its characteristics of eight turns in an88-mm pc-board footprint stem froma process that ensures that the transmit-ters radiated power never exceeds 250nW at 80 MHz.

According to European Telecommuni-cation Standard I-ETS 300 220, the trans-mitter requires no license and can oper-ate at any carrier frequency within the 74-to 87.5-MHz band. Consult applicableregulations for unlicensed transmitteroperation in your locality.

At a transmitted power of less than 250nW, an AM receiver with a tangential sen-sitivity of 1 V provides a receptionrange as long as 10m, which is sufficientfor many indoor-telemetry applications.At a maximum PPM frequency of 600Hz, the current drain of the circuit in Fig-ure 1 is approximately 2 mA at a supplyvoltage of 4V.

References1. Williams, Jim, Circuits allow direct

digitization of low- level transducer out-puts, EDN, Nov 29, 1984, pg 183.

2. Williams, Jim, Digitize transduceroutputs directly at the source, EDN, Jan10, 1985, pg 201.

This oscilloscope photo shows circuits internal waveforms:Trace 1 is the integrators output voltage, Trace 2 is the comparators out-put voltage, Trace 3 is the inverters output voltage, and Trace 4 is thePPM-output voltage.

F igure 2

TRACE 1

TRACE 2

TRACE 3

TRACE 4

CHANNEL 1 HIGH2.655V

CHANNEL 1 LOW1.721V

CHANNEL 1 FREQUENCY404.9VLOW SIGNAL AMPLITUDE

CHANNEL 4 + WIDTH15.92 SECLOW SIGNAL AMPLITUDE

(3)

(4)

(5)

(6)

(7)

(8)

-

www.edn.com January 20, 2005 | edn 79

ideasdesign

Texas Instruments BQ2010 battery-gas-gauge IC offers a convenientmethod for recording availablecharge stored in a nickel-cadmium ornickel-metal-hydride battery. However,even though plenty of charge remainsavailable, under certain circumstances,transient-current spikes can fool theBQ2010 into registering a discharged bat-tery. For example, spikes can occur whenyou connect a heating element or aswitched-mode regulator containing ahigh-value input capacitor, or if you mo-mentarily short-circuit the batterys ter-

minals while making a connection.During a current spike, the battery

voltage decreases by the voltage dropacross the batterys internal resistanceplus the voltage drop across the circuitscurrent-sense resistor. The BQ2010 mis-interprets the voltage decrease as a low-cell voltage condition normally seen dur-ing discharge. The device then loses dataon the remaining battery capacity, and,depending on the application, of theBQ2010s Empty output, the load mayinadvertently disconnect. Finally, the bat-tery must contain a partial charge to un-

Enhanced battery gas gauge keeps its data through glitchesHerbert Seidenberg, Costa Mesa, CA

Edited by Brad Thompson

IC4LT1790

VIN VOUT

GND

VOLTAGEREGULATOR

VBATTERY

VINT

VBATTERY

VBATTERY

VLOAD

VCC

VINT

PROGRAMMINGRESISTORS

DISP

SB

SR

LCOM

GND

EMPTY

IC1BQ2010

GAS-GAUGE IC

EMPTY

ON

VOLTAGE SENSE

CURRENT SENSE

LCOM

LCOM

LED DISPLAY

RESISTORNETWORK

CURRENTCOMPENSATION

CURRENT SENSE

CURRENTCOMP

R7

R6

R40.1

R36

VOLTAGE SENSE

VBATTERY

VBATTERY

LOGIC

TIMERON

VLOAD

VLOAD

EMPTY

S1

S2

IC5LTC1477

D6

VLOADJ1

ON/OFF

HIGH-SIDESWITCH

+BATTERY

CURRENT SENSE

+

TO LOAD

IC3BTLC2262_

+

ON

OFF

F igure 1

This circuit improves the BQ2010s current-spike immunity in several ways and adds several useful features.

Enhanced battery gas gauge keeps its data through glitches ..................79

Charge pump converts 5V to 5V ..........82

JFETs offer LC oscillators with few components....................................82

Autostart circuit helps ATX motherboards resume operationafter power interruptions..............................86

Publish your Design Idea in EDN. See theWhats Up section at www.edn.com.

-

80 edn | January 20, 2005 www.edn.com

ideasdesign

latch the BQ2010s Empty output.The circuit in Figure 1 improves the

BQ2010s current-spike immunity inseveral ways and adds several useful fea-tures. First, a 3.3V, current-limited low-dropout voltage regulator, IC

4, supplies

power to IC1, the BQ2010. Second, an

LTC1477 short-circuit-protected, high-side FET switch, IC

5, limits battery-to-

load current to a maximum of 2A. Toprevent IC

1s SB (single-cell voltage)

monitor pin from sensing an invalidEmpty state, current-compensation am-plifier IC

3Bmakes the voltage to the SB

pin current-independent. The negativerail of IC

3Bconnects to the active side of

the ground-referenced current-sense re-sistor, R

4. With no load current, op amp

IC3B

s output should rest at 0V, but few

rail-to-rail op amps provide outputs thatgo to 0V. The solution is to bias the pos-itive side of the op amp enough to set theoutput above V

OL and compensate by

lowering the gas-gauge-voltage sense-re-sistor ratio.

Additional features include a short-circuited load shutoff to prevent IC

5from

going into thermal-protection mode(Figure 2). Also, the entire circuit shutsoff when the battery provides no currentto the load or when the battery is dis-charged.A timer circuit consisting of IC

7,

IC8

and IC9

provides an additional shut-off option. You can set the turnoff delayfrom minutes to days by changing R

33

and C7

to reduce the clock frequency, orby selecting other taps on binary ripplecounters IC

8and IC

9. Pressing switch S

2

or starting a recharging cycle turns thecontroller back on. The parallel-con-nected sections of Schottky diode D

6pro-

vide a current path for recharging thebattery.

Although the resistor values shown inFigure 2 apply to a specific application,you can customize the circuit for a bat-terys chemistry, capacity, internal resist-ance, cell count, and timer and displayoptions. You can calculate componentvalues via a Microsoft Excel 2002 spread-sheet in the Web version of this DesignIdea at www.edn.com. All of the circuitslow-profile, surface-mounted compo-nents fit on one side of a 1.8-sq-in., four-layer board. The switches and LEDreadout connect to the pc boards un-derside.

14 3 1 2

5

4

6

8

12

9

ASTABLE

TRIGGER+ TRIGGER

RETRIGGER

RESET

R3324.9k

VSS

OUT

OUT

OSC OFF

11

13

10 CLOCK

C70.047 F

VCC COM RC EXT C EXT R

7

9765

4

32

131214151

9765

4

32

131214151

RESET

INPUT

VDD

10

VSSCD4040B8 8

Q5

Q2Q3Q4

Q6Q7

Q10Q9Q8

Q12Q11

Q1

VLOAD

16

10CLOCK

TIMER

11

CD4040B

TIME- OUT

VLOAD

7CD4002B

3452

9101112

EMPTY

7

VLOAD

VLOAD

ON

S2

VBATTERY

VLOAD LOGIC

13

R34100k

VLOAD

16

INPUT

RESET

Q5

Q2Q3Q4

Q6Q7

Q10Q9Q8

Q12Q11

Q1VDD

VSS

IC8 IC9

R32100k

IC7CD4047B

ASTABLE

R35100k

R30100k

ON

14

3

VLOADVLOAD VBATTERY

21C5

0.1 FC6

0.1 F

IC2B

CD4002B

J1

OUTPUTCONNECTOR

CURRENTCOMPENSATION

VBATTERY

CURRENT SENSE

CURRENT SENSE

CURRENT SENSE

R2010.5k

R25499k

5

6

R23100k

R2471.5k

IC3B

TLC2262

4

IC2A

21

VIN1

VIN3

VIN2

VINS

VOUT1

VOUT2

EN GND

4+

+

VLOADVBATSWITCH

IC5LTC1477

D620CJQ030

C210 FC3

10 F

ON/OFF

5

8

12

3

7

6

NOTE: IC3A IS UNUSED.

D7BAV74

11

VLOAD

8

21

3

CON2

VLOAD

14

CURRENTCOMPENSATION

_

+_+

You can customize this circuit for a batterys chemistry, capacity, internal resistance, cell count, and timer and displayoptions.F igure 2

-

82 edn | January 20, 2005 www.edn.com

ideasdesign

Versatile switched-capacitorcharge-pump voltage converterscan provide a negative supply volt-age from a positive-voltage source ordouble a positive sources voltage. How-ever, certain applications that consist en-tirely of ECL (emitter-coupled-logic)circuits provide only a negative-voltagesupplyfor example, 5.2V. Figure 1shows how you can use a switched-capacitor converter to obtain a pos-itive power-supply voltage suitable forpowering ECL-to-TTL (transistor-to-transistor-logic)-level translators andother circuits.

Although connections to IC1

may ap-pear to be reversed, the bilateral charac-teristics of IC

1s internal switches allow

use of IC1s output pin as its power in-

put. Capacitor C1

acquires a chargewhen IC

1s internal switches connect the

CAP pin to ground and CAP to thenegative-voltage power source via theoutput pin, OUT. During the next half-cycle, IC

1connects CAP to

ground and CAP to IN(normally used as the input), transfer-ring C

1s positive charge to output ca-

pacitor C3

and the load. With FSEL con-nected to OUT, an internal oscillator setsthe charge-discharge cycles frequency toapproximately 1 MHz.

As Figure 2 shows, IC1s switches pres-

ent internal resistances that affect theoutput voltages magnitude, which is

lower than the input voltage and subjectto less-than-ideal regulation as output-load current increases. For optimum

performance, use low-ESR capacitorsfor C

1,and input and output bypass ca-

pacitors C2

and C3.

INOUT

LV

FSEL

SHDN

IC1MAX1681

CAP+

CAP

VOUT4 TO 5.5V

VIN4 TO 5.5V

C11 F

C31 F

C21 F

8

2

4

5

6

1

7

3 GNDF igure 1

OUTPUTVOLTAGE

(V)

0 20 40 60 80 100 120 1403.8

4

4.2

4.4

4.6

4.8

5

5.2VIN=5V

F igure 2

Charge pump converts 5V to 5VKen Yang, Maxim Integrated Products Inc, Sunnyvale, CA

The backwards switched-capacitor converter converts 5V to 5V.

This load-voltage-versus-current graph shows the effects of the converters nonzero output imped-ance on output regulation.

JFETs offer LC oscillators with few componentsHerminio Martnez, Joan Domingo, Juan Gmiz, and Antoni Grau,Technical University of Catalonia, Barcelona, Spain

By using JFETs in unusual configu-rations, you can design simple,high-frequency LC oscillators withfew passive components. The structurefor implementing the amplifier stagecomprises a JFET transistor that you con-figure as a common drain (Figure 1).

When the JFET transistor works in thesaturation zone, the drain current, I

D, is:

where IDSS

is the maximum saturationcurrent and V

Pis the pinch-off voltage.

You can model the JFET in this satura-

tion zone in the small-signal regime us-ing an infinite input impedance and acurrent source that the gate-source volt-age controls. The following equation de-termines the small-signal transconduc-tance of the transistor:

-

84 edn | January 20, 2005 www.edn.com

ideasdesign

VIN (t)VOUT (t)

VDD

RG RS

Q1

F igure 1

You can configure an amplifier stage, based ona JFET transistor, as a common drain.

To complete the oscillator circuit, you add anLC-resonant tank to the amplifier stage; theresult is a Colpitts oscillator.

VOUT (t)

VDD

C2

L3

C1

RS

Q1

F igure 2

You can develop a Hartley oscillator based ona JFET transistor.

VOUT (t)

VDD

L2

C3

L1

RS

Q1

F igure 3

Gate resistance RG

provides the neces-sary connection from the gate to ground.Its typical value is in the low-megaohmrange to provide the needed high imped-ance of the amplifier structure. Resis-tance R

Sbiases the transistor; the

following equation determines re-sistance:

To complete the oscillator circuit, youadd an LC-resonant tank to the amplifierstage (Figure 2); the result is a Colpitts os-cillator. The connection from the gate toground for dc exists because of the induc-tance of the LC-resonant tank, removingthe gate resistance of the amplifier.

Analyzing the circuit using theBarkhausen criterion, the frequency ofoscillation f

Oof the circuit is:

The necessary condition on the capac-itors so that the circuit can oscillate is:

or, equivalently, the voltage gain, AV, of

the amplifier stage, VOUT

(t)/VG(t), is:

where voltage gain of the common drainstage is:

which demonstrates that the voltage gainin always lower than one.

Similarly, you can develop a Hartleyoscillator based on a JFET transistor (Fig-ure 3). The simulation and experimen-tal results for the Colpitts oscillator cir-cuit uses a 2N3819, an n-channel device,for the JFET. The PSpice parameters forthis transistor are I

DSSof 12 mA and V

P

of 3V. Simulation shows the voltagegain of the amplifier circuit is 0.3064V,and, with C

1 having a value of 50 nF and

C2

having a value of 114 nF, then

and the circuit oscillates (Figure 4),which also shows the start-up process ofthe oscillator. The voltage gain also showsthat the design meets the start-up con-

ditions on the capacitors:

Note that transconductance of thetransistor is equal to the value of the slopeof the curve i

Df(V

GS) at this operating

point. Depending on this point, the ac-tual value of the transconductance will belarger or smaller. Confirming this value,when oscillations start up, the curveiDf(V

GS) restricts the amplitude of the

output signal due to the reduction of thetransconductance when V

GSdecreases to

values close to the pinch-off voltage; inthis zone of the curve, its slope and, there-fore, the transconductance is smaller. Theintrinsic nonlinearity of the JFET tran-sistor limits the gain of the amplifierstage, and no additional circuit stabiliz-ing the amplitude of the output signal isnecessary.

With C1 having a value of 50 nF and C2 having a value of 114 nF, the circuit oscillates.

F igure 4

,

TIME(nSEC)

VOUT(V)

-

86 edn | January 20, 2005 www.edn.com

ideasdesign

Unlike legacy PC motherboards, anATX-style motherboard controls itspower supplys on/off state. If acpower fails, many ATX motherboards donot automatically restart when power re-turns, and that behavior is unacceptablefor a server system that must providenear-continuous service. Although somePCs provide BIOS configuration selec-tions for wake-on-LAN or wake-on-modemoperation, these options dependon another computer to provide thewake-up call. A few ATX motherboardchip sets offer an always-onBIOS option, but chances are, themotherboard thats available foryour server system isnt one ofthese.

The circuit design in Figure 1offers a reliable method of recov-ery from a power interruption.Upon restoration of ac power, anATX power supply delivers astandby voltage of 5V dc at amaximum of 10 mA via Pin 9 ofits power connector (Figure2). With standby power avail-able, low-power CMOS timer

TLC555 CP IC1

functions as an astableoscillator and delivers pulses at approxi-mately 4-sec intervals to MOSFET-out-put optoisolator IC

2. The output of IC

2

connects in parallel with the PCs front-panel power-on switch and in effectpushes the power switch every 4 sec.

In most astable-oscillator designsbased on the generic 555 timer, timingcapacitor C

3connects from pins 2 and 6

to ground. Upon initial application ofpower, IC

1s output goes low, activating

IC2

and generating an immediate pow-

er-on signal. Depending on the mother-boards design, an immediate start-upsignal may cause the motherboard to lockup. Connecting C

3as shown eliminates

the initial start-up pulse.When the power supply switches on,

primary 5V power becomes available atpins 4, 6, 19, and 20, driving diode D

1

into conduction and biasing Pin 7 of IC1

to a level that stops oscillation. AlthoughIC

1s output (Pin 3) can directly drive a

motherboards power-on input, MOS-FET-output optoisolator IC

2removes the

need to trace the polarity of thepower-on switchs connections. Inaddition, IC

2eliminates any pos-

sibility of incompatible logic lev-els that some 3.3V motherboards impose.

You can assemble the start-upcircuit on a small section of proto-typing board and splice its con-nections into the power supplyswiring harness and power-onpushbutton wiring. Variants ofATX connectors exist, so verifywiring before connecting the start-up circuit.

IC1TLC555CP

IC2HSR312LRST

DIS

VCC

OUT

GND CON

1 6

R3820

C20.1 F

C40.1 F

C3100 F

D11N4148

C1100 F

R222.1k1%

R122.1k1%

THRES

TRIG

4

7

6

2

5VSB

8

+

5VSB+

PIN 9PURPLE

WIRE

21

PIN 4, 6,19, OR 20RED WIRE

ASTABLE MODE: 2.7 SECONDS ON1.3 SECONDS OFF

3 1

2

3

PIN 3, 5, 7,13, 15, 16, OR 17

BLACK WIRE

5V

COM

6

5

4 MB2

MB1

PB2

PB1 FROM CHASSISPOWER PUSHBUTTONSWITCH

TO MOTHERBOARDPOWER PUSHBUTTONSWITCH

F igure 1

Autostart circuit helps ATX motherboards resumeoperation after power interruptionsWilliam Mohat , Ameritech, Cleveland, OH

An inexpensive CMOS 555 timer generates power-on-switch closures upon restoration of ac power.

This view of an ATX power supplys connec-tor shows color codes. Pinouts may differ

slightly from manufacturer to manufacturer.

ORANGEBLUEBLACKGREENBLACKBLACKBLACKWHITEREDRED

3.3V12VCOM/PS_ONCOMCOMCOM5V5V5V

ORANGEORANGEBLACKREDBLACKREDBLACKGRAYPURPLEYELLOW

3.3V3.3VCOM5VCOM5VCOMPWR_OK5VSB12V

12345678910

11121314151617181920

NOTES: 5VSB = 10 mA MAXIMUM. SHORT /PS_ON TO COM TO TURN ON.

F igure 2

-

www.edn.com February 3, 2005 | edn 83

ideasdesignEdited by Brad Thompson

Ensuring that new networkedproducts, such as routers, gatewaysor DSLAMs (digital-subscriber-line-access multiplexers) meet stringent tim-ing specifications usually requires a spe-cialized jitter/wander generator. As asubstitute, you can use a standardfunction generator equipped with PM(phase modulation) or FM (frequencymodulation) to measure jitter and wan-der tolerance. This Design Idea describeshow to convert PM and FM parameters(phase deviation, frequency deviation,and modulating frequency) into jitter/wander parametersamplitude in UIs(unit intervals) and frequency.

Network-communications engineersuse the terms jitter and wander todescribe phase noise in digital signals.Wander refers to phase noise at fre-quencies below 10 Hz, and jitterrefers tophase noise at frequencies at or above 10Hz. Defining phase noise requires specify-ing both its amplitude and its frequency.

As Figure 1 shows, if you observe aclock with phase noise on an oscilloscopetriggered by a clock of the same frequen-cy but without phase noise, the rising andfalling edges of the noisy clock appearblurredthat is, not clearly defined intime. If the clock has low frequency-phase noise (wander), the rising and

falling edges move back and forth at arate equal to the wander frequency. Therange of this movement defines the jit-ter/wander amplitude.

Figure 2 illustrates an instance of sine-wave-shaped FM of jitter or wander. Youcan express jitter or wander amplitude inUIs; one UI is equal to the clock period.For example, the amplitude of the jit-ter/wander in Figure 2 is 0.25 UI p-p.

You can use a signal generator to gen-erate waveform jitter and wander by con-necting a low-frequency signal source tothe signal generators PM or FM input.Equation 1 applies to both FM and PMand describes the general form of an an-

gle-modulating signal:s(t)Acos[2f

Ct(t)].

Although in digital communications,s(t) usually approximates a square-wavefunction, using a square wave instead ofa sine wave complicates the math butdoesnt affect the process of angle mod-ulation. For simplicity, this Design Ideauses a sine-wave function for s(t).

For PM, the phase (t) in Equation 1is proportional to the modulation signal:

(t)DPM

cos(2fm

t),where D

PMis the phase deviation (peak

variation of the phase), and fm

representsthe modulating frequency, which is alsothe jitter/wander frequency. The rela-

Use an off-the-shelf signal source as a jitter/wander generator Slobodan Milijevic, Zarlink Semiconductor

The effects of jitter or wander appear as position modulation of a pulses leadingand trailing edges.

1 UI

JITTER/WANDERAMPLITUDE

[UI p-p]

JITTER/WANDERFREQUENCY(Hz)=1/Tj/w

Tj/wF igure 2

Applying an external signal source to a signal generators phase- or frequency-modulation inputproduces a jittery output waveform.

Use an off-the-shelf signal sourceas a jitter/wander generator ......................83

Temperature controller saves energy........84

Calculator program finds closest standard-resistor values..................86

Reduce voltage-reference output noise by half ..............................................................88

Touch switch needs no dc return path......90

Publish your Design Idea in EDN. See theWhats Up section at www.edn.com.

F igure 1

(1)

(2)

The best ofdesign ideas Check it out at:www.edn.com

-

84 edn | February 3, 2005 www.edn.com

ideasdesigntionship between phase deviation and jit-ter/wander amplitude is straightforward,and you can obtain it from:

JITTER/WANDER[UI p-p]D

PM/180, (3)

where DPM

has units of radians in com-munications theory, but, for convenience,most signal generators specify units ofdegrees instead.

For FM, the phase (t) in Equation 1 isproportional to the integral of modulatingsignal.

where DFM

is the frequency deviation(peak variation of the frequency) and f

m

is the modulating frequency. The FMmodulating frequency is the same as thejitter/wander frequency. Equation 5 yieldsthe jitter/wander amplitude:

which derives from Equation 6:

Therefore, the peak-to-peak deviationof (t) is:

in which the factor of 2 originates fromthe peak-to-peak amplitude of a sine-wave function. To get jitter/wander inpeak-to-peak unit intervals, divide Equa-tion 7 by the period of the sine-wavefunction, 2. Thus, you get Equation 6,which is valid only when the modulatingsignal comprises a sine wave because theintegral of a sine wave is also a sine-wavefunction shifted in phase. Fortunately,most jitter/wander-tolerance tests almost

exclusively use sine-wave modulation.Some signal generators specify modu-

lation in phase and frequency span in-stead of phase and frequency deviation.For PM, the span is the peak-to-peakvariation of the phase, and, for FM, thespan is the peak-to-peak variation of thefrequency. That is, the span equals twicethe deviation for both PM and FM. Inthis case, the jitter/wander amplitude forPM is:

and it is:

for FM.

Given the high cost of electricalpower, replacing a conventionalon/off temperature control with aproportional controller can often saveenergy and money. Figure 1 shows a low-cost, high-efficiency, time-proportionaltemperature controller for a residentialwater heater. An Analog Devices ADT14,

IC1, serves multiple functions as a tem-

perature sensor, quad-setpoint, pro-grammable analog temperature monitorand controller. Resistors R

1, R

2, R

3, R

4,and

R5adjust desired temperature at setpoints

SETP1, SETP2, SETP3, and SETP4,which IC

1compares with the actual tem-

perature from its internal sensor. The

ADT14s active-low open-collector out-puts drive Input Port A of IC

2, an 8-bit

Motorola/Freescale 68HC908QT4 mi-crocontroller that provides 4 kbytes offlash memory, 128 bytes of RAM, and anon-chip clock oscillator.

Available at EDNs online version ofthis Design Idea at www.edn.com, List-

VREF

SETP4

SETP3

SETP2

SETP1

GND

VCC

OUT4

OUT3

OUT2

OUT1

VPT

14

15

10

7

2

5

R110.2k

R2475

R3475

R4475

R520k

6

1

8

9

16 4

5

6

7

11

8

HYST

PTA3

PTA2

PTA1

PTA0

PTA3

PTA3

GND

VCC

1

5VVCC

2

3 1 IC3A2

74LS06

ACPOWER

ACPOWER

Q1

HEATER

68HC908QTADT14SENSOR

ZERO-CROSS

CIRCUIT

IC4

R6475

1

2

MOC3043

TIC263M

R1221

6

4

13

IC1 IC2

Temperature controller saves energyTito Smailagich, ENIC, Belgrade, Yugoslavia

This proportional temperature controller features a minimal parts count.F igure 1

-

86 edn | February 3, 2005 www.edn.com

ideasdesign

ing 1 contains commented assembly-lan-guage software. When you load it into themicrocontrollers flash memory, the soft-ware provides the time-proportionalcontrol algorithm. When IC

1s OUT1,

OUT2, OUT3, and OUT4 outputs are in-active, IC

2 switches its output PTA4 to a

totally on-state, 100% duty cycle for max-imum heating. Listing 2 at the Web ver-sion of this Design Idea contains an as-sembled version of the software, andListing 3 presents the hex code for pro-gramming IC

2.

When IC1s OUT1 output is active, IC

2

produces a 75%-duty-cycle output onPTA

4. In similar fashion, when IC

1s

OUT2 output goes active, IC2

producesa 50%-duty-cycle output on PTA4

,, and

when IC1s OUT3 output goes active, IC

2

produces a 25%-duty-cycle output on

PTA4. When IC

1s OUT4 output goes ac-

tive, IC1

disables the output on PTA4 toproduce a totally off state (0% duty cy-cle). Table 1 summarizes the relationshipof IC

2s inputs and output duty cycle.

To minimize component count, IC2s

internal oscillator generates a 12.8-MHzclock that divides to produce a samplepulse whose basic width is 0.1 sec for each1% of output on-time. One cycle of out-put comprises 100 samples for a total du-ration of 10 sec. Thus, for a 25% duty cy-

cle, IC2s output PTA4 generates a 2.5-sec

on interval followed by a 7.5-sec off in-terval. One section of an open-collectorhex inverter, IC

3A, a 74LS06, drives opto-

coupler IC4, an MOC3043, which fea-

tures an internal zero-crossing circuit andpilot triac. Power triac Q

1, a TIC263M

rated for 600V and 25A, controls appli-cation of power to the water heaters 2-kW resistive heating element. For best re-sults, place IC

1in close thermal contact

with the water heaters inner tank.

Calculator program finds closest standard-resistor valuesFrancesc Casanellas, Aiguafreda, Spain

Although it may not appear obviousto newcomers to the electronics-de-sign profession, components valuesfollow one of several progressions that di-vide a decadewide span into equallyspaced increments on a logarithmic scale.For example, when you plot the values of1, 2.2, and 4.7 on a logarithmic scale, theydivide the range 1 to 10 into three rough-ly equal increments (1... 2... 5). To meet re-quirements for greater precision, resistormanufacturers offer parts in several addi-tional series. The most precise series di-vide a decade into 24, 48, or 96 incrementsby computing 10n/m ,where n1... (m1),

and m24, 48, or 96, and then roundingthe values to two or three digits. The re-sults are the R

24, R

48, and R

96series and re-

spectively contain 24, 48, or 96 values perdecade.

You can use a Hewlett-Packard HP-48or HP-49 calculator and one of the fol-lowing programs written in RPN (Re-verse-Polish Notation) to compute thenearest standard value thats closest to arequired value.You enter a required resis-tor value, and the program returns theclosest higher or lower value in the select-ed series. Table 1 lists a few examples.

Each program acts as an operator byprocessing the first line ofthe calculators stack and re-turning the new value in thesame line of the stack. TheR

48and R

96series are math-

ematically exact, and theirprograms consist of only asingle line of code. The List-

ings at the Web version of this Design Ideaat www.edn.com show the code. The val-ues of the older R

24series are not as strict-

ly rounded,and the program is thus some-what more complex.

Note that the values of other compo-nents, such as capacitors, inductors, andzener diodes, also follow preferred-valueseries, making these programs universal-ly applicable. You can view an earlier ver-sion of a standard-value calculator forIBM-compatible PCs at EDNs online ver-sion of Design Ideas. David Kirkby of theDepartment of Medical Physics, Univer-sity College London, UK, wrote the pro-gram in C. EDN first presented it, Resis-tance calculator yields precise values,in the Aug 3, 1995, issue.You can read theinstructions at www.edn.com/archives/1995/080395/16di5.htm. Note that cer-tain portions of the software may requirerewriting for better operation on todaysPCs.

TABLE 1INPUT VALUE IN SELECTED SERIES RETURNS A CLOSEST VALUE OF:47.8 R24 47490 R24 51012.2 R96 12.112.3 R96 12.4

TABLE 1IC2S LOGIC STATES VERSUS OUTPUT DURATIONSPTA3 PTA2 PTA1 On (%) Off (%) On (sec) Off (sec)

1 1 1 100 0 10 01 1 1 75 25 7.5 2.51 1 0 50 50 5 51 0 0 25 75 2.5 7.50 0 0 0 100 100 10

-

88 edn | February 3, 2005 www.edn.com

ideasdesign

Reducing low-frequency (1/f)noise generated by an IC voltagereference can prove difficult. In the-ory, adding a lowpass filter to a refer-ences output reduces noise. In practice,a lowpass RC filter for suppression ofnoise frequencies below 10 Hz requireslarge values of series resistance and shuntcapacitance. Unfortunately, a high-valueseries resistor introduces resistance errorsand thermal noise, and a shunt capaci-tors leakage resistance forms an unpre-dictable and unstable shunt path. To-gether, the two components form a noisyand temperature-dependent voltage di-vider that directly affects the referencesaccuracy and long-term stability. In ad-dition, pc-board surface contaminantscan add yet another possible leakage pathand error source.

You can stack multiple voltage refer-ences in series to reduce their 1/f noise.The references dc outputs add linearly,and their uncorrelated internal noisesources add geometrically. For example,consider a stack of four voltage refer-ences, each comprising a dc referencesource, V

REF, in series with a random-

noise generator, VNOISE

. Adding four ref-erence sources produces the followingoutputs: V

REFTOTAL4V

REF, and V

NOISE-

TOTAL4(V

NOISE)22V

NOISE. The

original ratio of noise voltage to dc ref-erence voltage thus divides in half.

Figure 1 illustrates a method of addingmultiple references to produce a single,less noisy reference voltage. The resistorsare parts of a highly stable metal-filmnetwork, and buffer amplifier IC

5offers

low noise, low input-offset voltage, andlow offset-temperature coefficients.

Tables 1 and 2 present the noise volt-ages that result from stacking four eachof two types of 2.5V references. Eachtable shows the 0.1- to 10-Hz noise volt-age for each of the four references,IC

1through IC

4, and for the com-

bination. Note that the dispersion in theratios of rms to peak-to-peak values re-lates to subjectivity in the method ofmeasuring the values. In addition to low-er 0.1- to 10-Hz noise, the circuit also re-duces long-term drift of the referencevoltage.

Four 2.5V references, IC1 through IC4, produce 10V. Resistors R1 and R2 form a voltage divider thatreduces the 10V output to 2.5V and lowers the output-noise voltage by half. Buffer amplifier IC5isolates the reference circuit from the load.

IC12.5V

REFERENCE IC10VREF

OUTINGND

IC22.5V

REFERENCE IC OUTIN

GND

IC32.5V

REFERENCE IC OUTIN

GND

IC42.5V

REFERENCE IC OUTIN

GND

2.5VREDUCED-

NOISEREFERENCE

OUTPUT

IC5MAX4236A

R24.99k

R14.99k

C50.1 F

C40.1 F

C30.1 F

C1 C2100 F

12V0.1 F

12V

C60.1 F

F igure 1

Reduce voltage-reference output noise by halfAlfredo H Saab and Steve Logan, Maxim Integrated Products Inc, Sunnyvale, CA

TABLE 1NOISE VOLTAGES MEASURED IN FIGURE 1 USING FOUR 2.5V MAX6037 VOLTAGE REFERENCES

Measurement points Noise Noise(V rms) (V p-p)

Reduced noise output 1 10(op amps output to V)Across Reference A (IC1) 1.9 20(OUT to GND)Across Reference B (IC2) 1.6 19(OUT to GND)Across Reference C (IC3) 1.7 20(OUT to GND)Across Reference D (IC4) 2.7 30(OUT to GND)

TABLE 2NOISE VOLTAGES MEASURED IN FIGURE 1 USING FOUR 2.5V MAX6143 VOLTAGE REFERENCES

Measurement points Noise Noise(V rms) (V p-p)

Reduced noise output 0.27 2.2(op amps output to V)Across Reference A (IC1) 0.52 4.7(OUT to GND)Across Reference B (IC2) 0.6 4.8(OUT to GND)Across Reference C (IC3) 0.5 4.3(OUT to GND)Across Reference D (IC4) 0.55 4.7(OUT to GND)

-

90 edn | February 3, 2005 www.edn.com

ideasdesign

Common designs for touch switch-es detect a decrease in resistancewhen a users fingertip either con-nects a contact to the circuits commonground or supplies an injection of 60-Hzac voltage, resulting from immersion inthe electrostatic field that nearby powerlines radiate. But what if no nearby pow-er lines exist and the equipment operatesfrom a battery source, such as in an au-tomotive application, or if a galvanic con-tact to circuit common is unavailable?

The circuit shown in Figure 1 operatesby sensing an increase in capacitance thatresults from touching a contact. Al-though a straightforward design mightrequire a complex circuit, the design

shown offers a low-cost approach thatuses few components.

In Figure 1, IC1A

operates as a square-wave oscillator at approximately 150 kHz.The oscillators output gets ac-coupled topotentiometer R

2that sets the drive level

and, hence, the sensitivity for the touchpad. Applying negative excursions of sev-eral volts of square-wave signal to its gaterepetitively drive N-channel JFET Q

1

from conduction into cutoff. An approx-imation of the square wave swingingfrom 0 to 12V appears at Q

1s drain. A

peak detector circuit formed by D1, R

7

and C4

provides sufficient dc voltage toforce IC

1Bs output to a logic low.

However, if someone touches the

touch pad, any added capacitance toground or circuit common reduces the acdrive at the FETs gate, and Q

1continu-

ously conducts. The square-wave voltageapplied to D

1decreases. The voltage on

C4

drops below the logic threshold, andIC

1Bs output goes high.You can adjust R

2

to set sensitivity and compensate for de-vice-to-device variations in the FETspinch-off voltage. For novelty or nostal-gias sake, you can use one-half of a12AX7 dual triode as an oscillator and theremaining half in place of Q

1. Selecting

plate resistors allows operation with a12V plate power supply.

IC14010

8

IC1401

10

IC14010

IC1C40106

IC1B40106

C41 nF

R71M

R410k

R3100k

R510M

D11N4148

R610k

R210k

R16.8k

C21 nF

C30.1 F

C10.1 F

Q12N5457

12

9

11

13

TOUCH

TOUCH

TOUCHPAD

12V

12V

5 6

3 4

1 2

7

14IC1A

40106

DRIVE LEVEL/SENSITIVITY

F igure 1

Touch switch needs no dc return pathBrad Albing, Philips Medical Systems Inc, Cleveland, OH

A low-cost touch-switch interface uses three Schmitt trigger hex inverters and a single JFET per channel.

-

www.edn.com February 17, 2005 | edn 77

ideasdesign

Digitally controlled potentiome-ters are useful for generating analogcontrol voltages under the controlof a microcontroller. In some applica-tions, manual pushbutton switches couldreplace a microcontroller and simplifyproduct design. Mechanical switches ex-hibit contact bounce, and, when a useractuates them, they may open and closemany times before reaching a stable state.

A digital potentiometers control inputslack switch-debouncing capabilities, andits up/down control is not suited forpushbutton operation. Figure 1 illus-trates solutions to these issues and showshow to use a digital potentiometer tocontrol a boost converter.

The potentiometer, IC1 , a MAX5160M,

presents an end-to-end resistance of 100k. To increment the wipers position,W,you press and hold the U/D pushbutton,S

2, to pull the U/D pin high and then

press and release pushbutton S1

to pulsethe INC input. Similarly, you decrementthe wiper position by releasing S

2and

pulsing S1.

A time-delay network comprising R1,

R2, and C

1masks S

1s switch bounce,

which would otherwise toggle the wipersposition between V

DDand approximate-

ly 0V. When you press S1, capacitor C

1

charges via R2

and causes the INC pin to ramp slowly toward 0V, thereby re-moving the effects of S

1s contact bounce.

The R1C

1time constant requires that

you depress S1

for several milliseconds before the INC input takes effect.

In this application, switching convert-er IC

2,, a MAX1771, operates as a stan-

dard boost converter and increases its 5Vinput to a higher voltage positive output.You can use Equation 1 to set IC

2s out-

R1100k

R210k

S1R610k

2

1

3

4

5V

5V

S2

C10.1 F

5VVIN

MAX5160IC1

7

6

5

VIN

VDD 8

CS

L

W

IC2MAX1771

GND

5

4

6

REF

SHDN

AGND

EXT

CS

FB

VOUT5 TO16V

R333k

+

+

VIN5V C4

68 FC2

0.1 F

2

1

8

3

V+L1

47 H

D11N5817

R510k

R44.7k

7

R70.1

Q1IRF530

200 FC6

INC

U/D

H

GND

5V

C30.1 F

Pushbuttons and digital potentiometer control boost converterSimon Bramble, Maxim Integrated Products Inc, Wokingham, UK

A digital potentiometer, IC1, and two pushbutton switches, S1 and S2, let you adjust the regulated output voltage of boost con-verter IC2 over a 10V range.

Pushbuttons and digital potentiometer control boost converter ................................77

Microcontroller protects dc motor..............78

Improved Kelvin contacts boost current-sensing accuracy by an order of magnitude ..........................80

Active pullup/pulldown network saves watts ......................................................82

Sine-wave step-up converter uses Class E concept ..............................................82

Publish your Design Idea in EDN. See theWhats Up section at www.edn.com.

Edited by Brad Thompson

The best ofdesign ideas Check it out at:www.edn.com

F igure 1

-

78 edn | February 17, 2005 www.edn.com

ideasdesign

Although any overloadeddc motor can draw exces-sive current and sustaindamage, a cooling fans motoris particularly vulnerable dueto fouling by dust, insects, ormisplaced objects. A fewfans include built-in overloadprotection, and others can usean external warning device,such as Microchips TC670 fan-failure detector.

In many products, its essen-tial not only to detect an over-loaded motor, but also toswitch off the motor to preventfailure. Although you can de-sign a protection systemaround the TC670, a low-endmicrocontroller can offer a lessexpensive, more flexible, andeasier to implement alterna-tive. If a product includes a mi-crocontroller, only two sparepins are necessary for motorprotection.

Figure 1 shows a dedicatedprotection circuit based on asmall microcontroller and apower FET. This project uses aneight-pin flash-memory MC68HC-908QT2 from Freescale and an IRF520AFET from Fairchild to control a dc brush-less-fan motor rated for 0.72A at 12V dc.A high or low output voltage on outputPA5 of IC

1 controls Q

1, an N-channel FET

that in turn controls the motor. Currentthrough the motor develops a voltage, V,thats proportional to the motor currentacross sense resistor R

1. A lowpass filter

comprising R2

and C1

reduces noise onthe sense voltage you apply to input PA4

and IC1s built-in A/D con-

verter. Voltage regulator IC2

provides stable 5V power forIC

1.

Under normal operation,the voltage across R

1measures

approximately 0.52V. Whenthe motor undergoes an over-load, voltage increases until itreaches a preset upper limit of0.85V. The output on PA5then drops to a low level,switching off transistor Q

1 to

stop the motor, and lightingD

1to indicate the overload.

When the motor stops, itdraws no current, and thesense voltage falls below theminimum threshold value of0.3V. The microcontrollersoutput on PA5 remains lowand holds off Q

1, a state that

it maintains indefinitely untilyou cycle the circuits poweroff and then on.

The control program, in as-sembly language for the MC-68HC908, features a straight-

forward algorithm adaptableto other microcontrollers that

include an A/D converter. A 2.5-sec de-lay routine prevents the motor fromstarting until the systems power-supplyvoltage stabilizes. You can download thelisting from the online version of this Design Idea at www.edn.com.

LED

78L051 3

2

IC2

D1

IC1

12V

DCMOTOR

Q1IRF520

R11.3

R2100k

C110 F

2

3

1

8

1

2

3

MC68HC908QT2

PA5

PA4

V

NOTE: D1, A LITE-ON LTL-4223-R2, INCLUDES A BUILT-IN RESISTOR.

F igure 1

Microcontroller protects dc motorAbel Raynus, Armatron International Inc, Malden, MA

Controller for dc brushless fan motor features minimal parts count.

put to a nominal 12V output without thedigital potentiometer:

Connecting IC1s wiper via 10-k re-

sistor R5

to IC2s FB (feedback) node sets

IC2s voltage-feedback level. Although

inclusion of feedback resistors R3, R

4,

and R5

and digital potentiometer IC1

complicates the precise calculation ofIC

2s output voltage, you can simplify the

math by calculating the output voltages

at the potentiometers extreme settings.Thus, with IC

1s wiper set to 0V, R

equals the paralleled resistance of R4

andR

5, and IC

2s maximum output voltage

becomes Equation 2:

or VMAX16.84V.

With IC1s wiper set to 5V, you can at-

tempt to calculate the minimum outputvoltage by summing voltages into thefeedback node:

which simplifies to VMIN0.48V.

However, Equation 3 provides an incor-rect value for V

MINbecause a boost con-

verters output voltage cannot go belowits input voltage. You can approximateV

MINby substituting a value of 10 k for

R5

in Equation 3 and solving for VMIN

:V

MIN4.93V. Refer to the manufacturers

application notes for additional compo-nent information.

(2)

(3)

(1)

-

80 edn | February 17, 2005 www.edn.com

ideasdesign

Many power-supply designs relyon accurately sensing the voltageacross a current-sense element.Multiphase regulators use the sense volt-age to force current sharing among phas-es, and single-phase regulators to controlthe current-limit setpoint. As internalcomplexity and clock speeds increase,processors impose narrower operatingmargins for power-supply voltages andcurrents, which in turn make accuratecurrent sensing critically important. Themost accurate of several available meth-ods involves inserting a low-value cur-rent-sensing resistor in the power sup-plys output path. Another populartechnique uses the parasitic resistance ofa switching regulators output inductoras the sense element. For either method,currents of 20A or more per power-sup-ply phase impose a sense-resistance lim-it of approximately 1 m. Precision re-sistors of 1% accuracy are available atreasonable cost, but an error of 1% of 1m amounts to only 10 .

The resistance of solder joints that at-tach a sense resistor or inductor can eas-ily exceed 10 and, worse yet, can varysignificantly during a production run. Inthe past, discrete four-wire resistors pro-vided separate high-current and sense-voltage connections, allowing accurateKelvin sensing and excluding voltagedrops that the high-current connectionsintroduce. Unfortunately, four-wire senseresistors or inductors are unavailable inlow cost SMD packages. Thus, most pow-er-supply designers use two-wire sensecomponents and apply a Kelvin-connec-tion pc-board-layout technique (Figure1). However, test results reveal that ap-plying conventional Kelvin sensing tech-niques to low-value resistors introducestransduction errors as high as 25%anunacceptable error margin for designsthat require high accuracy.

So, whats a power-supply designer todo? The answer involves a slight variationon an old idea that requires only a minor

change in a sense resistors mountingfootprint. To compare performance ofconventional Kelvin connections versusthe proposed method, a test board in-cludes three pc-layout footprints for in-stallation of 1-m, 1%-accurate, surface-mount resistors. In all three patterns,current enters and exits the resistor viatraces (not shown) on the pads left andright sides, respectively.

In Figure 1a, applying a current of4.004A produces a sense voltage at theKelvin terminals of 4.058 mV, a 1.35% er-ror. At 8.002A, the sense voltage at theKelvin terminals measures 8.090 mV, a1.1% error. In Figure 1b, a current of4.004A produces a sense voltage at theKelvin terminals of 5.01 mV, a 25% error.At 8.002A, the sense voltage at the Kelvinterminals measures 9.462 mV for an er-

ror of 18.2%. Figure 2 shows an im-proved component footprint. Each largesolder pad includes a central cutout areathat partially surrounds a narrow padthat solders directly to the sense elementand thus carries no current. This ap-proach removes from the sense path thelarge-area solder joints that mount thepart and carry high load current.

When you apply a current of 4.002A tothe pads in Figure 2, voltage at the Kelvinterminals measures 4.004 mV, a 0.05%error. At 8.003A, the sense voltage meas-ures 8.012 mV, an error of only 0.11%and an order of magnitude improvementover Figure 1a. Sense-voltage variationover temperature should greatly improve,and solder-thickness variation no longeraffects the sense voltage. Best of all, thetechnique costs nothing to implement.

Obviously, the technique in Figure 2works only with terminations sufficient-ly wide to allow dividing the solder padinto three sections and still retain ade-quate soldering area to handle the high-current connections. However, for manydesigns, this simple technique can signif-icantly improve the accuracy of currentsharing, V-I load-line characterization,and current-limit setpoints.

CURRENT FLOW

S1 S2

CURRENT FLOW

(a)

(b)

S1 S2

S1 S2

Improved Kelvin contacts boost current-sensing accuracy by an order of magnitudeCraig Varga, National Semiconductor Corp, Phoenix, AZ

Conventional solderpads offer two choices

for Kelvin connections: on the pads inneredges (a) or outer corners (b).

Modified pads provideisolated Kelvin connec-

tions that eliminate errors introduced by volt-age drops across soldered connections carryinghigh current.

F igure 1

F igure 2

-

82 edn | February 17, 2005 www.edn.com

ideasdesign

Many power applications rangingfrom luminescent and fluorescentlighting to telephone-ringing volt-age generators require a more or less si-nusoidal-drive voltage. These applica-tions typically require a waveform of onlymoderate quality, and its frequency isntespecially critical. However, avoidingwaveform discontinuities that cause un-wanted current peaks, excessive device

dissipation, and EMC problems rules outusing filtered square waves or otherstepped waveforms. Sometimes, a trape-zoidal drive may be acceptable but itsonly a second choice at best. This DesignIdea proposes a method of generatingsine waves that offers a number of ad-vantages over more complex methods:

The circuit requires only one power-switching device, and you can use an ana-

log or a digital signal to drive the switch-ing device. The circuit also requires onlya few components: a diode, a switchingtransistor or a MOSFET, an inductor ora transformer, and a capacitor. Further,the designs circuit losses are low, and theswitching device experiences minimalstress during operation. Figure 1 showsthe basic circuit, and Figure 2 illustrates

Sine-wave step-up converter uses Class E conceptLouis Vlemincq, Belgacom, Evere, Belgium

The control circuit in Figure 1presents a relatively low input resist-ance and thus imposes a low value onexternal pulldown resistor R

1to provide

the desired low-level input voltage. Inturn, R

1 wastes power by drawing a rela-

tively high current through switch S1. For

example, suppose that the control circuitpresents an input resistance of 2.2 k andrequires a logic-low input of 5V or less.At a V

CCof 24V, R

1must not exceed 500

for a current drain of 24/50048 mA.The power dissipated in R

1is thus

242/0.51152 mW, which requires a 2Wresistor for reliable operation.

In this application, the system includesthree controls with three input circuits,which present a total current of 432 mA

and adds approximately 10W to the pow-er budget. To reduce wasted power, it usesan active pulldown circuit (inside thedashed line in Figure 2).As long as switchS

1remains closed, PNP transistor Q

1s

base voltage exceeds its emitter voltagedue to diode D

1s forward voltage drop.

Thus, Q1

doesnt conduct, and the con-trol circuits input voltage rests atV

CC0.7V (D

1s forward voltage drop).

Opening S1

reverse-biases D1, and the

base current flowing through resistor R1

turns on Q1, which saturates and pulls the

circuits input to VCE(SAT)

. Closed-circuitcurrent through S

1is thus V

CC/R

1. For ex-

ample, with VCC

of 24V and R1

having avalue of 10 k, I24/102.4 mA, and R

1

dissipates 0.058W, or approximately 20times less power than in Figure 1. In thisapplication, current demand of the ninecontrol-circuit inputs decreases from 432to 22 mA and saves pc-board space byeliminating the need for using 2W. As avariant, Figure 3 shows an active-pullupversion of the circuit.

ENABLE

D2

S1

VCC

R22.2k

R1500

I ENABLE

D2D1

Q1

S1

VCC

R22.2k

R110k

I

D1

Q1

R110k

S2

VDD

Active pullup/pulldown network saves wattsJB Guiot, DCS Dental AG, Allschwil, Switzerland

A conventional networkrequires a low-value pulldown resistor.

An active pulldown cir-cuit substitutes a saturated transistor for apower-consuming pulldown resistor.

Rearranging the circuit andusing an NPN transistor for Q1 yields an active-pullup network.

F igure 1F igure 3F igure 2

(continued on pg 86)

-

86 edn | February 17, 2005 www.edn.com

ideasdesign

waveforms within the circuit.In operation, the sine-wave output ap-

pears across inductor L in a series LC cir-cuit. An external clock source pro-duces gate drive for transistor Q at afrequency thats lower than the LC cir-cuits natural resonant frequency. Whenthe transistor conducts, the inductor re-ceives a charging current via diode D.When conduction ends, energy stored inthe inductor transfers to capacitor C, anda damped oscillation begins (uppermosttrace in Figure 2). The voltage across ca-pacitor C approximates a sine wave (toptrace). Drain current in transistor Qshows that no current flows until the ca-pacitor voltage forward-biases diode D(middle trace). The gate-drive pulse in-terval is lower than the series-resonantfrequency that L and C present (bottomtrace).

During the negative-going portion ofthe cycle, the external clock source appliesgate drive to the transistor. Diode D is stillreverse-biased, and thus no current flowsinto Q. When the voltage across C goespositive, diode D conducts and allows

current to recharge the inductor and re-plenish energy lost in the previous cycle.In balanced operation, energy suppliedduring the conduction phase replenish-es energy supplied to the load and dissi-pated in component losses.

To produce a higher peak voltage, youextend the conduction interval by raising

the drive frequency or by extending theon interval. You can regulate the outputvoltage by applying conventional closed-loop feedback techniques to a variable-frequency clock oscillator or, in digitalsystems, by altering the clocks duration.For most applications in which load cur-rent is relatively fixed, such as in an elec-troluminescent panel lamp, an open-loopadjustment or manual control offers suf-ficient flexibility once you determine aclock-frequency range that correspondsto the desired degree of illumination.

For peak voltages not exceeding 10times the power-supply voltage, you canconnect the load directly to the junctionof D, L, and C. You can achieve highervoltage-to-step-up ratios at the expenseof applying additional voltage and cur-rent stress to L and C. Instead, you canadd an isolated secondary step-up wind-ing to the inductor. For optimum effi-ciency, use components designed forhigh-frequency power handlingfor ex-ample, a polypropylene-dielectric capac-itor and a low-loss inductor.

If the load consists of an electrolumi-nescent panel that behaves as a lossy ca-pacitor, you may be able to eliminate theuse of external capacitor C. Transistor Qmust obviously be able to withstand peakvoltages and currents that the circuit im-poses, but its specifications are otherwiserelatively noncritical. No switching lossoccurs at the beginning of the conduc-tion due to the Class E mode of opera-tion, and the output capacitor assists thedevices turn-off recovery. For outputvoltages not exceeding approximately50V, you can improve efficiency by se-lecting a Schottky or other fast-recoverydiode for use in the circuit.

For powering lamps and generatingtelephone-ringing signals, the sine wavesflat spots are of little consequence be-cause of their relatively short durationand low harmonic-energy content. Youcan minimize these intervals by reducingthe LC ratio and thus increasing theloaded Q factor of the LC circuit. How-ever, for a given output voltage, increas-ing Q factor also increases the peak cur-rent because the same amount of energymust transfer to the inductor in lesstime.

OUTPUT

L

D

QGATE-DRIVEINPUT

C

F igure 1

Few components are necessary to produce apseudo sine wave.

The circuit in Figure 1 produces these waveforms.

VOLTAGE ACROSS

CAPACITORVCC

GROUND

DRAINCURRENT

GATEDRIVE

TRANSISTOROFF INTERVAL

TRANSISTOR QCONDUCTION

INTERVALF igure 2

(continued from pg 82)

-

www.edn.com March 3, 2005 | edn 71

ideasdesign

Applications such as audio equal-izers require bandpass filters with aconstant maximum gain thats inde-pendent of the filters quality factor, Q.However, all of the well-known filter ar-chitecturesSallen-Key, multiple-feed-back, state-variable, and Tow-Thomassuffer from altered maximum gain whenQ varies. Equation 1 expresses the sec-ond-order bandpass transfer function ofa bandpass filter:

where K represents the filters gain con-stant.When the input frequency equals

O,

the filters gain,AMAX

, is proportional to theproduct, KQ. Thus, modifying the qualityfactor alters the gain and vice versa.

This Design Idea describes a filterstructure in which K is inversely propor-tional to Q. Altering Q also modifies K,producing a magnitude-plot set in whichthe curves maintain the same maximumgain at the central frequency

0that is,

KQ remains constant. Figure 1 shows thefilter, which comprises a twin T cell withan adjustable quality factor and a differ-ential stage. The differential stage com-prises op amp IC

3and resistors R

5A

through R5D

. This stage outputs the dif-ference between the filters input signaland the twin-T networks output. Capac-itors C

1and C

2are of equal value,

CC1C

2, capacitor C

3equals 2C, resis-

tors R1

and R2

are also equal and of val-ue RR

1R

2, and R

3equals R/

2. Equa-

tion 2 describes the twin-T circuitstransfer-function response as a notch fil-ter producing output V

BR(t):

Equation 3 describes the compete cir-cuits transfer function, a bandpass-filterresponse with output V

OUT(t):