CMOS Process Flow (1)

Transcript of CMOS Process Flow (1)

-

7/30/2019 CMOS Process Flow (1)

1/28

CMOS Process Flow

Susanta Sen

Institute of Radio Physics & Electronics

University of Calcutta

-

7/30/2019 CMOS Process Flow (1)

2/28

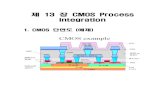

p-Si substrate

p-Si substrate

Transistor Fabrication

Top

View

Cross-

sectional

View

Oxidize Si (Gate Oxide formation)

Deposit Poly-Si

Cover with Gate Mask

Etch exposed Poly-Si

Etch exposed Oxide

Remove Gate Mask

Cover with Source-Drain Mask

Implant n-type dopant ions

Remove Source-Drain Mask

The transistor is completed

-

7/30/2019 CMOS Process Flow (1)

3/28

How to mask selective regions?

Photolithography

Photoresists

Sensitive to light

Resists chemical etchants

Steps of photolithography

Spin-Coat Si surface with photoresist

Bake to dry

Expose and develop pattern

Hard bake when necessary

-

7/30/2019 CMOS Process Flow (1)

4/28

to Vacuum Pump

Spin

5000rpm

20 sec.

Sprinkle

Photoresist

Steps of Lithography:1. Coat with Photoresist

-

7/30/2019 CMOS Process Flow (1)

5/28

Steps of Lithography

Bring Photo mask on the sample

Expose with UV light

-

7/30/2019 CMOS Process Flow (1)

6/28

Steps of Lithography:Develop Exposed Photoresist

Positive Resist:Exposed region

removed

Negative Resist:Unexposed region

removed

-

7/30/2019 CMOS Process Flow (1)

7/28

CMOS Process

Needs both p- and n-MOS devices

p-substrate good for n-MOS

Convert some region to n-doped

n-well or n-tub

Twin tub process also used

-

7/30/2019 CMOS Process Flow (1)

8/28

p-Si Substrate

Create n-wellGrow thick oxide

p-Si Substrate

Pattern photoresistEtch oxideRemove photoresistDiffuse n-dopantEtch remaining oxide

-

7/30/2019 CMOS Process Flow (1)

9/28

Isolate TransistorsDefine Active Areas

p-Si Substrate

Deposit Silicon NitridePattern Silicon NitrideEtch Silicon to form deep trenchesForm Thick Oxide to fill up trenchesEtch Silicon Nitride

Ready to fabricate Transistors

Grow thin oxide,deposit Poly-Si and pattern GateCover p-transistors only with photoresist & implant n-dopantCover n-transistors only with photoresist & implant p-dopantRemove photoresistThe transistors are ready

-

7/30/2019 CMOS Process Flow (1)

10/28

Next

Interconnectsto complete the

Circuit

-

7/30/2019 CMOS Process Flow (1)

11/28

p-Si Substrate

Prepare for Interconnect

1. Connect Poly2. Deposit thick oxide3. Etch contact cuts4. Fill hole with metal5. interconnectwithmetal

-

7/30/2019 CMOS Process Flow (1)

12/28

Circuit Layout

-

7/30/2019 CMOS Process Flow (1)

13/28

What are the Masks

Active Area Poly-Si Contact

Cut

Metallization

-

7/30/2019 CMOS Process Flow (1)

14/28

How to Align different levels?

Alignment Marks

-

7/30/2019 CMOS Process Flow (1)

15/28

Assignment 1

2-input NAND Gate

2-input NOR Gate

Design the Mask Sets forthe following circuits:

-

7/30/2019 CMOS Process Flow (1)

16/28

Lithographic Imperfections

UndercutLines become narrow

Disconnection

BulgeLines become wider

Shorts to adjacent line

Misalignment between layers

Device failure

-

7/30/2019 CMOS Process Flow (1)

17/28

Undercut and Bulge

-

7/30/2019 CMOS Process Flow (1)

18/28

Misalignment

S DG

Channel short Circuit

-

7/30/2019 CMOS Process Flow (1)

19/28

Design Rules

Takes care of manufacturing tolerances

Specifies minimum allowed dimensions

Line width

Spacing between lines on same layer

Spacing between lines on different layers

Overlap between features where required

Diffusion requires higher tolerance

Specified in terms of Scalable parameter ()

Design Rule Check (DRC) essential

-

7/30/2019 CMOS Process Flow (1)

20/28

Stick Diagram Layout Design Problem:

Satisfy both Circuit Topology & Design

Rules

Overwhelming task for large design

Follow Two-step process

1. Stick Diagram

Circuit topology Cartoon representation

2. Layout Diagram Expand each line to rectangle

Follow Design Rules

-

7/30/2019 CMOS Process Flow (1)

21/28

Stick Diagram Basics

Features represented by Lines (sticks) Poly / Diffusion / Metal etc.

Different colours for different layers

poly

n-diffusion

p-diffusion

metal 1

metal 2

contact / via

p-transistor

n-transistor

VDD

VSS

OutIn

-

7/30/2019 CMOS Process Flow (1)

22/28

Assignment 2

Draw Stick Diagrams for:

NAND Gates (2, 3, 4 inputs)

NOR Gates (2, 3, 4 inputs)

2 to 1 MUX

2-input XOR

-

7/30/2019 CMOS Process Flow (1)

23/28

Stick Diagram to Layout

2

1

-

7/30/2019 CMOS Process Flow (1)

24/28

Assignment 3

Draw Layouts

for

Stick Diagrams

of

Assignment 2

-

7/30/2019 CMOS Process Flow (1)

25/28

Layout Design Issues

Multilevel circuit Metal to be routed over transistors

Limits number of interconnects

Transistors in Series Height changes Different height cells

Difficult to abut into regular-shape layout

CAD tools Placement & Routing issues

Standard Cell Concept

-

7/30/2019 CMOS Process Flow (1)

26/28

Standard Cell Layout Diffusion lines Horizontal

Poly-silicon lines Vertical

Input/Output Ports Above & Below Cell

Cells & Routing Channels in Alternate Rows

Cell 1 Cell 2 Cell 3 Cell 4

-

7/30/2019 CMOS Process Flow (1)

27/28

Standard Cell Transistors arranged horizontally

Extend diffusion line for more transistors

A A

Add Input

B

Modify connections

Cell height does not change

A.B

New Logic

-

7/30/2019 CMOS Process Flow (1)

28/28

Assignment 4

Repeat

Assignments 2 & 3

in

Standard Cell Style