CMOS Manufacturing Process

Transcript of CMOS Manufacturing Process

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOSManufacturing

Process

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

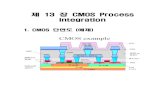

A Modern CMOS Process

p-well n-well

p+

p-epi

SiO2

AlCu

poly

n+

SiO2

p+

gate-oxide

Tungsten

TiSi2

DualDual--Well TrenchWell Trench--Isolated CMOS ProcessIsolated CMOS Process

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Circuit Under Design

This two-inverter circuit (of Figure 3.25 in the text) will bemanufactured in a twin-well process.

VDD VDD

VinVout

M1

M2

M3

M4

Vout2

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

The Manufacturing Process

For a great tour through the process and its different steps, checkhttp://www.fullman.com/semiconductors/semiconductors.html

http://bwrc.eecs.berkeley.edu/Classes/IcBook

For a complete walk-through of the process (64 steps), check theBook web-page

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

oxidation

opticalmask

processstep

photoresist coatingphotoresistremoval (ashing)

spin, rinse, dryacid etch

photoresist

stepper exposure

development

Typical operations in a single photolithographic cycle (from [Fullman]).

Photo-Lithographic Process

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Patterning of SiO2

Si-substrate

Si-substrate Si-substrate

(a) Silicon base material

(b) After oxidation and depositionof negative photoresist

(c) Stepper exposure

PhotoresistSiO2

UV-light

Patternedoptical mask

Exposed resist

SiO2

Si-substrate

Si-substrate

Si-substrate

SiO2

SiO2

(d) After development and etching of resist,chemical or plasma etch of SiO2

(e) After etching

(f) Final result after removal of resist

Hardened resist

Hardened resist

Chemical or plasmaetch

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOS Process at a GlanceDefine active areasEtch and fill trenches

Implant well regions

Deposit and patternpolysilicon layer

Implant source and drainregions and substrate contacts

Create contact and via windowsDeposit and pattern metal layers

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOS Process Walk-Through

p+

p-epi (a) Base material: p+ substrate with p-epi layer

p+

(c) After plasma etch of insulatingtrenches using the inverse of the active area mask

p+

p-epiSiO2

3SiN

4

(b) After deposition of gate-oxide andsacrificial nitride (acts as abuffer layer)

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOS Process Walk-ThroughSiO2

(d) After trench filling, CMPplanarization, and removal of sacrificial nitride

(e) After n-well and VTp adjust implants

n

(f) After p-well andVTn adjust implants

p

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOS Process Walk-Through

(g) After polysilicon depositionand etch

poly(silicon)

(h) After n+ source/drain andp+source/drain implants. These

p+n+

steps also dope the polysilicon.

(i) After deposition of SiO2insulator and contact hole etch.

SiO2

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOS Process Walk-Through

(j) After deposition and patterning of first Al layer.

Al

(k) After deposition of SiO 2insulator, etching of via’s,deposition and patterning ofsecond layer of Al.

AlSiO2

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Jan M. Rabaey

Design Rules

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

3D Perspective

Polysilicon Aluminum

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Design Rules

l Interface between designer and process engineer

l Guidelines for constructing process masksl Unit dimension: Minimum line width

» scalable design rules: lambda parameter» absolute dimensions (micron rules)

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOS Process Layers

Layer

Polysilicon

Metal1

Metal2

Contact To Poly

Contact To Diffusion

Via

Well (p,n)

Active Area (n+,p+)

Color Representation

Yellow

Green

Red

Blue

Magenta

Black

Black

Black

Select (p+,n+) Green

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Layers in 0.25 µm CMOS process

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Intra-Layer Design Rules

Metal24

3

10

90

Well

Active3

3

Polysilicon2

2

Different PotentialSame Potential

Metal13

3

2

Contactor Via

Select2

or6

2Hole

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Transistor Layout

1

2

5

3

Tran

sist

or

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Vias and Contacts

1

2

1

Via

Metal toPoly ContactMetal to

Active Contact

1

2

5

4

3 2

2

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Select Layer

1

3 3

2

2

2

WellSubstrate

Select3

5

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

CMOS Inverter Layout

A A’

np-substrate Field

Oxidep+n+

In

Out

GND VDD

(a) Layout

(b) Cross-Section along A-A’

A A’

Digital Integrated Circuits EE141Manufacturing ProcessManufacturing Process

Design Rule Checker

poly_not_fet to all_diff minimum spacing = 0.14 um.