High Voltage Normally-off GaN MOSC- HEMTs on Silicon ... Li-CFES13.pdf · High Voltage Normally-off...

Transcript of High Voltage Normally-off GaN MOSC- HEMTs on Silicon ... Li-CFES13.pdf · High Voltage Normally-off...

-

High Voltage Normally-off GaN MOSC-HEMTs on Silicon Substrates for Power

Switching Applications

Zhongda Li, John Waldron, Shinya Takashima, Rohan Dayal, Leila Parsa, Mona Hella,

and T. Paul Chow Department of Electrical, Computer, & Systems Engineering

Rensselaer Polytechnic Institute

Troy, NY USA

E-mail: [email protected]

This work was supported by SRC (Task 1961.001) and NSF ERC on Smart Lighting (EEC-0812056), and made use of ERC Shared Facilities supported by the NSF under Award Number EEC-9731677.

-

Zhongda Li 2 CFES Annual Conference 2013

Outline

Introduction

Design and Fabrication of the GaN MOS Channel HEMTs on Silicon Substrate

Experimental DC Characteristics

Circuit Results

Simulation of a Buck-Boost Converter

Experimental Demonstration of GaN MOS Bidirectional Switch on Silicon Substrate

-

Zhongda Li 3 CFES Annual Conference 2013

Introduction

GaN has been very attractive for power switching applications

10x critical field compared with silicon

Up to 200 oC operation temperature

2D electron gas (2DEG) with mobility up to 2000cm2/V-s

GaN MOS channel devices (MOSFETs and MOS Channel HEMTs) has the advantages of

Normally-off operation

Absence of gate turn-on

Low gate leakage

-

Zhongda Li 4 CFES Annual Conference 2013

Silicon

DrainSource

UID GaN

Gate

AlN/GaN Buffer

UID GaN

Al0.25Ga0.75N

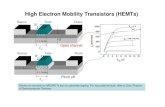

GaN MOS Channel HEMTs

MOS channel 2DEG

• The GaN MOS channel HEMTs (MOSC-HEMTs) were the combination of the GaN HEMTs and GaN MOSFETS

• The drift region utilized the highly conductive 2DEG similarly as in GaN HEMTs

• The MOS channel was formed by etching off the AlGaN to remove the 2DEG under the gate

• Deep submicron (0.3 µm) MOS channel was used in order to reduce its resistance component

• The use of the silicon substrate greatly improved the cost-effectiveness of this GaN device

-

Zhongda Li 5 CFES Annual Conference 2013

Design of the GaN MOSC-HEMTs • Two commercial GaN-on-Si epis were used in

fabricating the GaN MOSC-HEMTs

• Epi A has a optimal 20 nm thick GaN cap, but a thin total epi thickness of 1.8µm which limits the vertical BV

• Epi B has ≤ 1 nm GaN cap which was insufficient in achieving good RESURF effects, and a thicker total epi thickness of 4 µm

• Due to the difference in GaN cap, different

designs were used on the two Epi

Device on Epi A

Device on Epi B

Silicon

DrainSource

UID GaN

Gate

AlN/GaN Buffer

UID GaN

Al0.25Ga0.75N

Silicon

Al0.10Ga0.90N

DrainSource

UID GaN

Gate

AlN/GaN Buffer

Al0.25Ga0.75NCF4 plasma

treated

≤

-

Zhongda Li 6 CFES Annual Conference 2013

RESURF Effects from the GaN Cap

AlGaN

GaN

(+Qpol 1)(- Qpol 2)

+Qf

GaN(- Qpol 1)(+Qpol 2)

- Qf

(- Qpol 2)Passivation(+Qpas)

• The 20nm GaN cap on Epi A provided net negative polarization charges (-Qf) at the top GaN/AlGaN interface which balanced the net positive polarization charges (+Qf)

• Electric field lines (perpendicular to equivalent potential lines) terminate on the negative charges at the –Qf, n+ Si substrate, and the gate electrode.

Fixed Charges in the Drift Region

-

Zhongda Li 7 CFES Annual Conference 2013

Breakdown Simulations: GaN MOSC-HEMTs on Epi A

• Numerical simulations (MEDICI) showed a higher BV and a much better RESURF effect, with low gate corner field and a more uniform surface field

Oxide Field along Surface

At BV=646V, with GaN cap

Oxide Field along Surface

At BV=40V, without GaN cap

-

Zhongda Li 8 CFES Annual Conference 2013

Breakdown Simulations: GaN MOSC-HEMTs on Epi B

AlGaN

GaN

(+Qpol 1)(- Qpol 2)

+Qf

Passivation(-Qpol 1)(+Qpas)

0

200

400

600

800

1000

1200

0.0E+00 2.0E+12 4.0E+12 6.0E+12 8.0E+12

Bre

ak

do

wn

Vo

lta

ge

(V)

Total Charges (cm-2)

BV overall

BV GaN

Limited by

gate oxide

breakdown

• For devices on Epi B, the 1 nm GaN cap was insufficient in inducing negative polarization charge

• Thus the high oxide field at the gate corner can limit the overall BV of the device

• The total fixed charges (+Qf) needed to be reduced, here by means of incorporation of negative fluorine ions into the AlGaN using CF4 plasma treatment

Fixed Charges in the Drift Region

Oxide Field along Surface

At BV=646V, with GaN cap

Oxide Field along Surface

At BV=40V, without GaN cap

-

Zhongda Li 9 CFES Annual Conference 2013

Device Fabrication 0. Starting material 1. Mesa isolation

2. Epi B: CF4 plasma treatment 3. Deposit and pattern field plate oxide

-

Zhongda Li 10 CFES Annual Conference 2013

Device Fabrication (Continued)

6. Deposit ILD and lift-off Ti/Al/Ni/Au ohmic

metal 7. Evaporate and pattern Ti/Al final metal

4. Etch recess MOS channel 5. Sputter and pattern polysilicon gate

-

Zhongda Li 11 CFES Annual Conference 2013

Experimental DC Characteristics

0

20

40

60

80

100

120

140

160

0 2 4 6 8 10 12 14 16

ID(m

A/m

m)

VD (V)

VG=15V, step= -2V

0

5

10

15

20

25

30

35

40

45

50

0 2 4 6 8 10 12 14 16

ID(m

A/m

m)

VD (V)

VG=13V,

step=-2V

Output IDS-VDS on Epi A Output IDS-VDS on Epi B

• The GaN MOSC-HEMTs on Epi A with 0.3 µm MOS channel and 8 µm drift length showed a threshold voltage of +0.5V, and best Ron,sp of 4.05 mΩ-cm

2, which was among the lowest reported values for normally-off GaN MOSC-HEMTs.

• The GaN MOSC-HEMTs on Epi B with the same dimensions showed higher Ron,sp of 35 mΩ-cm2, which was attributed to a lower MOS channel mobility caused by the rougher GaN surface

-

Zhongda Li 12 CFES Annual Conference 2013

Analysis of Specific On-Resistance

0

2

4

6

8

10

12

14

16

18

20

22

0 1 2 3 4 5

Ron

,sp

(mΩ

-cm

2)

Channel Length (µm)

MOSC-HEMT(with GaN Cap Layer)

MOSC-HEMT(without GaN Cap Layer)

HEMT

Furukawa & RPI, SiO2 [4]

RPI, SiO2 [2]

MIT, Al2O3 [8]

This work, SiO2

MOS channel Drift Access Contact

μ (cm2/V-s) 55 2500 2500 -N (cm-2) 1.10E+13 2.50E+12 2.50E+12 -

Rsh (Ω/sq.) 1.03E+04 1.00E+03 1.00E+03 -L (μm) 0.255 8 9.745 -

W (μm) 600 600 600 600R (Ω) 4.39 13.33 16.25 3.49

Ron Percentage 12% 36% 43% 9%

Ron,sp ( mΩ-cm2) 4.05

• The analysis of the resistance components of the 4 mΩ-cm2 device showed that with the deep submicron channel design, only 12% of the total resistance came from the MOS channel

• The experimental results were consistent with those from the numerical simulation when scaling down the MOS channel, showing that the GaN MOSC-HEMTs were able to achieve comparable Ron,sp to that of GaN HEMTs

-

Zhongda Li 13 CFES Annual Conference 2013

Experimental Breakdown Characteristics: Epi A (20nm GaN Cap)

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

0 100 200 300 400

Cu

rren

t (m

A/m

m)

VD (V)

ID, 20um

IG, 20um

ID, 8um

IG, 8um

• ID increased sharply at BV while IG stayed the same, indicating that the breakdown happened in the bulk of the semiconductor near the drain side instead of at the gate corner

• The low gate field design enhanced the robustness of the device

• On Epi A, a non-destructive breakdown voltage of 350 V was measured, regardless of the drift lengths of the device (8 µm to 20 µm)

• This indicated that the breakdown voltage was limited by vertical breakdown voltage of the epi due to the thin total epi thickness

-

Zhongda Li 14 CFES Annual Conference 2013

Experimental Breakdown Characteristics: Epi B (CF4 Treated)

-0.4

-0.2

0.0

0.2

0.4

0.6

0.8

1.0

1.2

0 100 200 300 400 500 600 700 800 900

Cu

rren

t (m

A/m

m)

VD (V)

ID

IG

• Devices fabricated on the thick GaN epi (epi B) without CF4 plasma treatment showed a BV of only 40 V regardless of drift length

• Devices with 20 µm CF4-plasma-treated drift region showed a BV of 840 V

• However, the breakdown happened at the gate corner and thus was destructive, due to the less effective RESURF effects from the CF4 plasma treatment compared with the thick GaN cap

-

Zhongda Li 15 CFES Annual Conference 2013

Ron,sp vs. BV

• The Ron,sp vs BV plot of this work exceeds the silicon limit, but is not as good as the state-of-the-art performances due to the BV limitation of the thin GaN epi thickness

• Higher BV up to 1200V has been projected from numerical simulations with thick GaN epi layers or other BV enhancement techniques

MIT'10

Furukawa'11

Toshiba'07NEC'09

Furukawa/ RPI '10This work

1

10

100

100 1000 10000

Sp

ec

ific

On

-re

sis

tan

ce

(m

oh

m-c

m2)

Breakdown Voltage (V)

1D 2H-GaN

Limit

1D Si Limit

Projected perfornance with thick GaN epi or other techniques

-

Zhongda Li 16 CFES Annual Conference 2013

SPICE Simulation of a Buck-Boost Converter using GaN MOSC-HEMT

Device optimization at 10 MHz Power stage efficiency

• SPICE model of the GaN MOSC-HEMT were extracted from MEDICI simulations and used in buck-boost converter simulations, projecting system efficiency of 90% with ideal inductors

-

Zhongda Li 17 CFES Annual Conference 2013

GaN MOS Bidirectional Switch on Silicon Substrate

VG

V+

V-

S

D

D

S

G

G

• We have also demonstrated a GaN MOS bidirectional switch on silicon substrate using the GaN MOSC-HEMTs fabricated on Epi A

• GaN bidirectional switch operation:

• On-state: (VG>VTH):

• Both D1 and D2 are on, switch conducts bidriectionaly

• Off-state (VG

-

Zhongda Li 18 CFES Annual Conference 2013

GaN MOS Bidirectional Switch on Silicon Substrate

-5

-4

-3

-2

-1

0

1

2

3

4

5

-1 -0.5 0 0.5 1

Cu

rren

t (m

A)

Bias Voltage (V)

-2V

0V

2V

4V

6V

8V

10V

12V

-10

-5

0

5

10

-300 -200 -100 0 100 200 300

Cu

rren

t (µ

A)

Bias Voltage (V)

• The on-resistance of the AC switch is twice of the single device, and the blocking capability up to 200V

Bidirectional Conduction I-V Bidirectional Blocking I-V

-

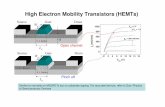

Zhongda Li 19 CFES Annual Conference 2013

Source Drain

Fins

Recess etch

GaN MOS Channel FinFETs Lc 300nm : without Fin structure Lc 300nm : with Fin structure

*Shinya Takashima et al, to be published

0

50

100

150

200

250

0 5 10 15Id

(m

A/m

m)

Vd (V)

Lc=0.3um

VG=-2 to 7V Step=1V

0

50

100

150

200

0 5 10 15

Id (

mA

/m

m)

Vd (V)

Lc=0.3um

VG=-2 to 7V Step=1V

0

50

100

150

200

250

300

- 2 0 2 4 6

Id (

mA

/m

m)

Vg (V)

Lch=1.1um

Lch=0.8um

Lch=0.6um

Lch=0.4um

Lch=0.3um

Lch=0.2um

0

20

40

60

80

100

120

140

160

- 2 0 2 4 6

Id (

mA

/m

m)

Vg (V)

Lch=1.1um

Lch=0.8um

Lch=0.6um

Lch=0.3um

ID-VG : without Fin structure ID-VG : with Fin structure

VD=10V VD=10V

-

Zhongda Li 20 CFES Annual Conference 2013

Summary

We have designed and fabricated GaN MOS Channel HEMTs with deep submicron MOS channels on silicon substrates on two different epi layers

Best specific on-resistance of 4 mΩ-cm2

Breakdown voltage of 350V on Epi A limited by the epi thickness, and 840V on Epi B which has a thicker GaN epi

A buck-boost converter has been simulated using SPICE parameters of the device

A GaN MOS bidirectional switch on silicon substrate has also been demonstrated

-

Zhongda Li 21 CFES Annual Conference 2013

Thank you!