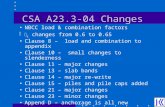

Csa 04

Transcript of Csa 04

-

7/31/2019 Csa 04

1/49

Click to edit Master subtitle style

6/6/12

Chapter 4

Input Output Systems

-

7/31/2019 Csa 04

2/49

6/6/12

Input / Output Problems Why peripherals are connected

directly to the system bus Wide variety of peripherals Delivering different data formats

At different speeds either slow or fast Need I/O modules and its functions

Interface to processor and Memory Interface to one or more peripherals

22

-

7/31/2019 Csa 04

3/49

6/6/12

Model of I/O Module

33

-

7/31/2019 Csa 04

4/49

6/6/12

External Devices Human readable - user

Screen, printer, keyboard Machine readable - equipment

magnetic disk, tape, sensors and actuators

Communication remote places Modem Network Interface Card (NIC)

44

-

7/31/2019 Csa 04

5/49

6/6/12

Diagram

55

-

7/31/2019 Csa 04

6/49

6/6/12

I/O Module Functions Control & Timing

CPU Communication Device Communication Data Buffering Error Detection

66

-

7/31/2019 Csa 04

7/49

6/6/12

Control And Timing To coordinate the flow of traffic between

CPU and devices Steps

CPU checks I/O module device status I/O module returns status If ready, CPU requests data transfer I/O module gets data from device I/O module transfers data to CPU

77

-

7/31/2019 Csa 04

8/49

6/6/12

Processor Communication I/O module has to communicate with

processor also Command decoding Data Status reporting Address recognition

Device communication: Must communicate with device also Commands Status information Data

88

-

7/31/2019 Csa 04

9/49

6/6/12

Data buffering Buffered in I/O module and then sent to

peripheral devices In opposite direction also same

Error detection

Report errors to the processor. Mechanical and electrical malfunctions

(paper jam, bad disk number) Changes in bit pattern Parity bits

99

-

7/31/2019 Csa 04

10/49

6/6/12

I/O Module Block Diagram

1010

-

7/31/2019 Csa 04

11/49

6/6/12

I/O Module Decisions Hide device properties to CPU

Support multiple or single device Control device functions or leave for

CPU

1111

-

7/31/2019 Csa 04

12/49

6/6/12

Input Output Techniques Programmed

Interrupt driven Direct Memory Access (DMA)

1212

P d I/O

-

7/31/2019 Csa 04

13/49

6/6/12

Programmed I/O CPU has direct control over I/O

Sensing status Read/write commands Transferring data

CPU waits for I/O module to completeoperation

Wastes CPU time

1313

ki

-

7/31/2019 Csa 04

14/49

6/6/12

Working CPU issues command to I/O module

I/O module performs operation I/O module sets status bits CPU checks status bits periodically

I/O module does not inform CPU directly orinterrupt it

1414

-

7/31/2019 Csa 04

15/49

6/6/12

I/O Commands While executing CPU issues

Address of the I/O module External device An I/O command.

Commands Control - activate or telling module what to

do Test - check status

e.g. powered on or not, Error. Read to obtain a data from peripheral Write take data to peripheral

1515

-

7/31/2019 Csa 04

16/49

6/6/12 1616

-

7/31/2019 Csa 04

17/49

6/6/12

Addressing I/O Devices Each device given unique identifier CPU commands contain identifier

(address)

1717

I/O M i

-

7/31/2019 Csa 04

18/49

6/6/12

I/O Mapping Memory mapped I/O

Devices and memory share an address space Treats data and status registers as memory

locations No special commands for I/O

Same instructions for both data and memory

Isolated I/O Separate address spaces Need I/O or memory select lines

Special commands for I/O Limited set

1818

M M d I/O

-

7/31/2019 Csa 04

19/49

6/6/12

Memory Mapped I/O

1919

-

7/31/2019 Csa 04

20/49

6/6/12

Isolated I/O

2020

I t t D i I/O

-

7/31/2019 Csa 04

21/49

6/6/12

Interrupt Driven I/O Overcomes CPU waiting

No repeated CPU checking of device I/O module interrupts when ready

2121

i i

-

7/31/2019 Csa 04

22/49

6/6/12

Basic Operation CPU issues read command

I/O module gets data from peripheralwhile CPU does other work

I/O module interrupts CPU

CPU requests data I/O module transfers data

2222

-

7/31/2019 Csa 04

23/49

6/6/12 2323

mp e nterrupt rocess ng

-

7/31/2019 Csa 04

24/49

6/6/12

mp e nterrupt rocess ng

2424

-

7/31/2019 Csa 04

25/49

6/6/12 2525

Design Iss es

-

7/31/2019 Csa 04

26/49

6/6/12

Design Issues How the processor identifies that which

module issued the interrupt? How does the processor deals with

multiple interrupts?

2626

-

7/31/2019 Csa 04

27/49

6/6/12

Module Different line for each module

Limits number of devices Software poll

CPU asks each module in turn Slow

Daisy Chain or Hardware poll Interrupt Acknowledge sent down a

chain Requested module responds by placing

a word on data bus containing anidentifier - vector

Vectored interrupt2727

-

7/31/2019 Csa 04

28/49

6/6/12

Bus arbitration Uses vectored interrupt

Module must claim the bus before it can raiseinterrupt

One module can do Processor detects interrupt and

acknowledges, the module places its vector

2828

M lti l I t t

-

7/31/2019 Csa 04

29/49

6/6/12

Multiple Interrupts Based on priority

Multiple lines Each line has its priority

Software polling Polling determines priority

Daisy chain Order of modules

Bus arbitration only current master can interrupt

2929

-

7/31/2019 Csa 04

30/49

6/6/12

89C59A interrupt controller 80x86 has one interrupt line only

80x86 based systems use 82C59A interruptcontroller

82C59A has 8 interrupt lines

3030

-

7/31/2019 Csa 04

31/49

6/6/12

-82C59A

Accepts interrupts from attached

modules Determines priority Signals processor (raises INTR line) CPU Acknowledges (INTA line) Puts correct vector on data bus CPU processes interrupt

3131

-

7/31/2019 Csa 04

32/49

6/6/12 3232

Interrupt modes

-

7/31/2019 Csa 04

33/49

6/6/12

Interrupt modes Fully nested

Ordered in priority from 0(IR0) to 7(IR7) Rotating

Equal priority, then serviced one afterother

Special mask Take interrupts from certain devices only

3333

-

7/31/2019 Csa 04

34/49

6/6/12

Interface

3434

-

7/31/2019 Csa 04

35/49

6/6/12

82C55A

3535

Direct Memory Access

-

7/31/2019 Csa 04

36/49

6/6/12

Direct Memory Access Interrupt driven and programmed I/O

require active CPU intervention Transfer rate is limited Number of instructions must be executed for

single I/O transfer

DMA Large volumes of data can be moved easily

DMA controller takes over from CPU for

I/O

3636

DMA Block Diagram

-

7/31/2019 Csa 04

37/49

6/6/12

DMA Block Diagram

3737

DMA Operation

-

7/31/2019 Csa 04

38/49

6/6/12

DMA Operation CPU tells DMA controller:-

Read/Write Device address Starting address of memory block for data Amount of data to be transferred

CPU carries on with other work DMA controller deals with transfer

Without going to the processors

DMA controller sends interrupt whenfinished

Processor is involved only at the starting

and at end of transfer 3838

-

7/31/2019 Csa 04

39/49

6/6/12

-Stealing

DMA controller takes over bus for a cycle

Transfer of one word of data and returnscontrol to the processor

Not an interrupt

CPU does not switch context Slows down CPU but not as much as CPU

doing transfer

3939

DMA and Interrupt Breakpoints

-

7/31/2019 Csa 04

40/49

6/6/12

DMA and Interrupt Breakpointsduring an Instruction Cycle

4040

DMA Configurations (1)

-

7/31/2019 Csa 04

41/49

6/6/12

DMA Configurations (1)

Single Bus, Detached DMA controller Each transfer uses bus twice

I/O to DMA then DMA to memory

CPU is suspended twice

4141

DMA Configurations (2)

-

7/31/2019 Csa 04

42/49

6/6/12

DMA Configurations (2)

Single Bus, Integrated DMAcontroller

DMA may support more than onedevice

Each transfer uses bus once DMA to memory

4242

DMA Configurations (3)

-

7/31/2019 Csa 04

43/49

6/6/12

DMA Configurations (3)

Separate I/O Bus

Each transfer uses bus once DMA to memory

CPU is suspended once

4343

Intel 8237A DMA Controller

-

7/31/2019 Csa 04

44/49

6/6/12

Intel 8237A DMA Controller Interfaces to 80x86 family and DRAM

DMA module needs buses it sends HOLDsignal to processor Processor responds HLDA then DMA can

use buses Ex. transfer data from memory to disk

Device requests by pulling DREQ (DMArequest) high

DMA puts high on HRQ (hold request), CPU finishes present bus cycle and puts

high on HDLA (hold acknowledge). HOLD remains active for duration of DMA DMA activates DACK (DMA acknowledge),4444

-

7/31/2019 Csa 04

45/49

6/6/12

Systems Bus

4545

-

7/31/2019 Csa 04

46/49

6/6/12

DMA starts transfer DMA deactivates HRQ, giving bus back to

CPU While DMA using buses processor idle

and while Processor using bus, DMA idle

Known as fly-by DMA controller Data does not pass through and is not stored

in DMA chip DMA only between I/O port and memory

Not between two I/O ports or two memorylocations

4646

I/O Channels - Evolution

-

7/31/2019 Csa 04

47/49

6/6/12

I/O Channels - Evolution CPU directly controls the peripherals

I/O module programmed I/o I/O module interrupt DMA

Processor on its own CPU initiates I/O module with memory

4747

I/O Channel Architecture

-

7/31/2019 Csa 04

48/49

6/6/12

I/O Channel Architecture

4848

-

7/31/2019 Csa 04

49/49

Byte multiplexor low speed devices Block multiplexor high speed

devices