TWO-LEVEL COMBINATIONAL LOGIC

Transcript of TWO-LEVEL COMBINATIONAL LOGIC

Combinational Logic, Spring 1999

1

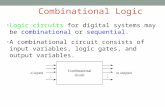

TWO-LEVEL COMBINATIONAL LOGIC

OVERVIEW

Canonical forms

Two-level simplification

Boolean cubes

Karnaugh maps

Quine-McClusky (Tabulation) Method

Don't care terms

Canonical and Standard Forms

Minterms and Maxterms

For two binary variables and combined with an AND operation, the orE F minterms

standard products are: , and . That is, two binary variables provideEFß EF ß E F E Fw w w w

# ú % 8 ## 8 possible combinations (minterms.) variables have minterms. Each minterm has

each variable being primed if the corresponding bit of the binary number is a and!

unprimed if a "Þ

Similarly, two binary variables and combined with an OR operation, the E F maxterms

or are: , and . Two binary variables alsostandard sums E Ä Fß E Ä F ß E Ä F E Ä Fw w w w

provide possible combinations (maxterms) and variables have maxterms. Each# ú % 8 ## 8

maxterm has each variable being primed if the corresponding bit of the binary number is a "

and unprimed if a !Þ

A maxterm is the complement of its corresponding minterm, and vice versa.

Sum of Products (or Minterms)

A Boolean function can be expressed as a sum of minterms. The minterms whose sum

defines the Boolean function are those that give the 1's of the function in a truth table.

Product of Sums (or Maxterms)

A Boolean function can be expressed as a product of maxterms. The maxterms whose

sum defines the Boolean function are those that give the 0's of the function in a truth table.

Minterms and Maxterms for Three Binary Variables

Combinational Logic, Spring 1999

2

Minterms Maxterms

Term Designation Term Designation\ ] ^

! ! !

! ! "

! " !

! " "

" ! !

" ! "

" " !

" " "

\ ] ^ 7 \ Ä ]

\ ] ^ 7

\ ] ^ 7

\ ] ^ 7

\] ^ 7

\] ^ 7

\] ^ 7

\] ^ 7

w w w!

w w"

w w#

w$

w w%

w&

w'

(

Ä ^ Q

\ Ä ] Ä ^ Q

\ Ä ] Ä ^ Q

\ Ä ] Ä ^ Q

\ Ä ] Ä ^ Q

\ Ä ] Ä ^ Q

\ Ä ] Ä ^ Q

\ Ä ] Ä ^ Q

!

w"

w#

w w$

w%

w w&

w w'

w w w(

Example: Given a three-variable truth table as follows:

\ ] ^ J J

! ! ! ! !

! ! " " !

! " ! ! !

! " " ! "

" ! ! " !

" ! " ! "

" " ! ! "

" " " " "

Function Function " #

J J" #and can be expressed as a sum of products as follows:

Combinational Logic, Spring 1999

3

J ú \ ] ^ Ä \] ^ Ä \] ^ ú 7 Ä 7 Ä 7" " % (w w w w

J ú \ ] ^ Ä \] ^ Ä \] ^ Ä \] ^ ú 7 Ä 7 Ä 7 Ä 7# $ & ' (w w w

J J" #and can also be expressed as a product of sums as follows:

J ú Ð\ Ä ] Ä ^ ÑÐ\ Ä ] Ä ^ ÑÐ\ Ä ] Ä ^ ÑÐ\ Ä ] Ä ^ ÑÐ\ Ä ] Ä ^ Ñ"w w w w w w w

ú Q Q Q Q Q! # $ & '

J ú Ð\ Ä ] Ä ^ ÑÐ\ Ä ] Ä ^ ÑÐ\ Ä ] Ä ^ ÑÐ\ Ä ] Ä ^ Ñ#w w w

ú Q Q Q Q! " # %

Boolean functions expressed as a sum of products or product of sums are said to be in

canonical form

A convenient way to express these function is by using a short notation, decimal form:

J Ð\ß ] ß ^Ñ ú 7Ð"ß %ß (Ñ J Ð\ß ] ß ^Ñ ú 7Ð$ß &ß 'ß (Ñ" #! ! and

or

J Ð\ß ] ß ^Ñ ú QÐ!ß #ß $ß %ß &ß 'Ñ J Ð\ß ] ß ^Ñ ú QÐ!ß "ß #ß %Ñ" #N N and

Standard forms

A Boolean function is said to be in if the function contains one, two or any standard form

number of literals. For example:

J ú ] Ä \] Ä \ ] ^ J ú \Ð] Ä ^ ÑÐ\ Ä ] Ä ^ Ä [ Ñ" #w w w w w wor

A Boolean function may be expressed in a nonstandard form. For example, the function

J ú Ð[\ Ä ] ^ÑÐ[ \ Ä ] ^ Ñw w w w

Examples:

1) Given the following truth table. Express in a canonical minterms and maxterms.J

Combinational Logic, Spring 1999

4

\ ] ^ J

! ! ! !

! ! " "

! " ! !

! " " !

" ! ! "

" ! "

" " !

" " " "

1

1

2) Design a digital logic circuit that will activate an alarm if a door or window is open

during non-business hours. Assume that

Clock (non-business hours) (business hours)

Door (closed) (opened)

Window (closed) (opened)

Alarm (off) (on)

G ú ! "

H ú ! "

[ ú ! "

E ú ! "

Conversion between canonical form

1) To convert from a sum of products to a product of sums: rewrite the minterm

canonical form in a shorthand notation then replace the existing term numbers by the missing

numbers. For example:

J Ð\ß ] ß ^Ñ ú 7Ð"ß $ß 'ß (Ñ ú QÐ!ß #ß %ß &Ñ! N

2) To convert from a product of sums to a sum of products: rewrite the maxterm

canonical form in a shorthand notation then replace the existing term numbers by the missing

numbers. For example:

J Ð\ß ] ß ^Ñ ú QÐ!ß #ß %ß &Ñ ú 7Ð"ß $ß 'ß (ÑN !

Combinational Logic, Spring 1999

5

3) To obtain the minterm (or maxterm) canonical form of the complement, given the

Boolean function in a sum of products (or product of sums) form : list the term numbers that

are missing in For example:J Þ

J Ð\ß ] ß ^Ñ ú 7Ð!ß #ß %ß &Ñ J Ð\ß ] ß ^Ñ ú 7Ð"ß $ß 'ß (Ñ! ! Ê w

J Ð\ß ] ß ^Ñ ú QÐ"ß $ß 'ß (Ñ J Ð\ß ] ß ^Ñ ú QÐ!ß #ß %ß &ÑN NÊ w

Positive and Negative Logic

Truth Table Positive Logic Negative Logic

\ ] ^ \ ] ^ \ ] ^

low low low 0 0 0 1 1 1low high low 0 1 0 1 0 1high low low 1 0 0 0 1 1high high high 1 1 1 0 0 0

Combinational Logic, Spring 1999

6

Truth Table Positive Logic Negative Logic

\ ] ^ \ ] ^ \ ] ^

low low high 0 0 1 1 1 0low high low 0 1 0 1 0 1high low low 1 0 0 0 1 1high high low 1 1 0 0 0 1

Example: Traffic lights -- to define three signals

Functionally Complete Operation Sets

A functionally complete operation set is a set of logic functions from which any

combinational logic expression can be realized. For example, AND, OR, and NOT can be

realized using NAND or NOR.

Not using NAND gates

Combinational Logic, Spring 1999

7

NOT realized using NAND

AND using NAND gates D ú BC ú BCà âa bw w

OR using NAND gates D ú B Ä C ú B Ca bw w w

XOR using NAND gates D ú B ä C ú B C Ä BC ú B C BCà â à â à âa b a b a b a bw w w ww w w ww w w

Note that

E Ä F ú E ì F E Ä F ú E ì F

E ì F ú E Ä F E ì F ú E Ä F

– –– –

– –– –a ba b

AND, NOR equivalent logic

B C B C B ì C B Ä C B Ä C B ì C

! ! " " ! ! " "

! " " ! ! ! ! !

" ! ! " ! ! ! !

" " ! ! " " ! !

– – – – – –

´

Combinational Logic, Spring 1999

8

´

OR, NAND equivalent logic

B C B C B Ä C B ì C B Ä C B ì C

! ! " " ! ! " "

! " " ! " " " "

" ! ! " " " " "

" " ! ! " " ! !

– – – – – –

´

´

Conversion from AND/OR to NAND/NAND

Conversion from AND/OR to NOR/NOR

Combinational Logic, Spring 1999

9

Conversion from OR/AND to NOR/NOR

Conversion from OR/AND to NAND/NAND

Examples:

1 convert to a NAND/NAND circuit.Ñ J ú EÐF Ä GHÑ Ä FG

Combinational Logic, Spring 1999

10

2) Covert the above circuit to NOR/NOR circuit.

3) J ú E\ Ä \ Ä H

\ ú FG

Combinational Logic, Spring 1999

11

Assignment#2 p.166: 2.7, 2.8, 2.18-22, 2.24, 2.26, 2.27, 2.29, 2.30, 2.35

Simplification of Boolean Functions

Boolean cubes

Examples

1) J Ð\ß ] Ñ ú \] Ä \]w

2) Full adder

Karnaugh Map Method

Two-, Three- and Four- K Maps

Combinational Logic, Spring 1999

12

Examples: Simplify each of the followings Boolean functions:

1) J Ð\ß ] ß ^Ñ ú 7Ð#ß $ß %ß &Ñ! Full adder#Ñ

3) 3, 4, 6, 7J Ð\ß ] ß ^Ñ ú 7Ð Ñ! 4) 0, 2, 4, 5, 6J Ð\ß ] ß ^Ñ ú 7Ð Ñ! 5) J ú \ ] Ä \ ^ Ä \] ^ Ä ] ^w w w

0, 2, 4, 5, 6'Ñ J Ð[ß \ß ] ß ^Ñ ú 7Ð "ß ß )ß *ß "#ß "$ß "% Ñ! (Ñ J ú [ \ ] Ä \ ] ^ Ä [ \] ^ Ä [ \ ]w w w w w w w w w

Prime Implicants

A is a minterm obtained by combining the maximum possible number ofprime implicant

adjacent squares in the map. If a minterm in a square is covered by only one prime implicant,

that prime implicant is said to be .essential

Example: 0, 2, 3, 5, 7 10, 11, 5J Ð[ß \ß ] ß ^Ñ ú 7Ð ß )ß *ß "$ß " Ñ!Examples of four-variable map

Two-bit comparator

Two-bit binary adder

Don't Care Conditions

Examples:

1Ñ J ÐEß F ß G ß HÑ ú 7Ð"ß $ß (ß ""ß "&Ñ Ä .Ð!ß #ß &Ñ! 2) J ÐEß F ß G ß HÑ ú 7Ð%ß &ß 'ß )ß *ß "!ß "$Ñ Ä .Ð!ß (ß "&Ñ! ) BCD increment by 1 function.$

Combinational Logic, Spring 1999

13

Combinational Logic, Spring 1999

14

Five and Six Variable Functions MinimizationFive variable K-maps

Example: p. 83 J ÐEß F ß G ß HßIÑ ú 7 Ð#ß &ß (ß )ß "!ß "$ß "&ß "(ß "*ß #"ß #$ß #%ß #*ß $"Ñ!

Combinational Logic, Spring 1999

15

Example: J ÐEß F ß G ß Hß I ß J Ñ ú 7Ð#ß )ß "!ß ")ß #%ß #'ß $%ß $(ß %#ß %&ß &!ß &$ß &)ß '"Ñ!

The Tabulation (Quine-McCluskey) Method

The tabulation method consists of two parts.

1) Find all prime implicants.

2) Find the smallest collection of prime implicants that cover the complete on-set of the

function.

Combinational Logic, Spring 1999

16

Example: J ÐEß F ß G ß HßIÑ ú 7 Ð#ß &ß (ß )ß "!ß "$ß "&ß "(ß "*ß #"ß #$ß #%ß #*ß $"Ñ!

28

5101724

7131921

152329

31

I II00010 0 - 010*01000 010 - 0*

0010101010 001 - 1000111000

00111011011001110101

011111011111101

11111

- 1000*

10 - 101 - 0101100 - 110 - 01

0 - 111 - 0111 - 1101011 - 110 - 111 - 101101 - 1

- 11111 - 111111 - 1

0 - 1 - 1 - 01 - 1 - - 10

III

110 - - 1*

- - 111 - 11 - 11 - 1 - 1

- - 1 - 1*

IV

The prime implicants are 0 - 010, 010-0, - 1000, 10 - - 1, and - - 1 - 1.

Then J ÐEß F ß G ß HßIÑ ú E G HI Ä FG H I Ä EF I Ä G Iw w w w w w w

Examples:

Combinational Logic, Spring 1999

17

1) J Ð [ ß \ ß ] ß ^ Ñ ú 7Ð"ß %ß 'ß (ß )ß *ß "!ß ""ß "#ß "&Ñ! #Ñ J ÐEß F ß G ß HßIÑ ú 7Ð!ß #ß $ß %ß &ß 'ß (ß ""ß "&ß "'ß ")ß "*ß #$ß #(ß $"Ñ!

3) J ÐEß F ß G ß HÑ ú 7Ð%ß &ß 'ß )ß *ß "!ß "$Ñ Ä .Ð!ß (ß "&Ñ!Assignment#$ p.236: 3.1-3.9, 3.12-3.14, 3.16, 3.23, 3.25, 3.28, 3.33, 3.36, 3.43, 3.47, 3.50

Example: Design a 6311 error detector where each of the decimal digits (0,1,...,9) can be

represented by a 4-bit code with weights 6, 3, 1, 1.

6 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 13 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 11 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 11 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

0 0 1 0 0 0 1 0 0 0 1 0 0 1 1 10 1 2 3 4 5 6 7 8 9

ABCDF

Combinational Logic Design Procedure

The design of combinational logic circuits starts from the verbal outline of the problem and

ends in a logic circuit diagram or a set of Boolean functions from which the logic diagram

can be easily obtained.

1. The problem is stated.

2. The number of available input variables and required output variables is determined.

3. The input and output variables are designed letter symbols.

4. The truth table that defines the required relationships between inputs and outputs is

derived.

5. The simplified Boolean function for each output is obtained.

6. The logic diagram is drawn.

Adders

Half–adders

A half-adder is a circuit that performs addition of two bits. Let the input variables be and\

] ß W G Ðand output variables be (sum) and carry).

Combinational Logic, Spring 1999

18

\ ] W G

! ! ! !

! " " !

" ! " !

" " ! "

W ú \ ] Ä \] ú Ð\ Ä ] ÑÐ\ Ä ] Ñ ú \] Ä \ ] ú \ ä ]w w w w w w

G ú \] ú Ð\ Ä ] Ñw w w

Full-adders

A full–adder is a combinational circuit that forms the arithmetic sum of three input bits.

Combinational Logic, Spring 1999

19

\ ] ^ W G

! ! ! ! !

! ! " " !

! " ! " !

! " " ! "

" ! ! " !

" ! " ! "

" " ! ! "

" " " " "

W ú \ ] ^ Ä \ ] ^ Ä \] ^ Ä \] ^ ú ^ ä Ð\ ä ] Ñw w w w w w

G ú \] Ä \^ Ä ] ^

SubtractorsHalf–subtractors

A half–subtractor is a combinational circuit that subtracts two bits and produces their

difference.

\ ] H F

! ! ! !

! " " "

" ! " !

" " ! !

Combinational Logic, Spring 1999

20

H ú \ ] Ä \]w w

F ú \ ]w

Full subtractors

A full–subtractor is a combinational circuit that performs a subtraction between two bits, taking

into account that a 1 may have been borrowed by a lower significant stage.

\ ] ^ H F

! ! ! ! !

! ! " " "

! " ! " "

! " " ! "

" ! ! " !

" ! " ! !

" " ! ! !

" " " " "

H ú \ ] ^ Ä \ ] ^ Ä \] ^ Ä \] ^w w w w w w

F ú \ ] Ä \ ^ Ä ] ^w w

Code conversion

The availability of a large variety of codes for the same discrete elements of information

results in the use of different codes by different digital systems. It is sometimes necessary to

use the output of one system as the input of another. A conversion circuit must be inserted

between the two systems if each uses different codes for the same information. Therefore, a

code converter is a circuit that makes the two systems compatible even though each uses a

different binary code. The following is an example of conversion form the BCD to the

excess–3 code.

Combinational Logic, Spring 1999

21

Input BCD Output Excess-3 Code

X X X X

X X

E F G H [ \ ] ^

! ! ! ! ! ! " "

! ! ! " ! " ! !

! ! " ! ! " ! "

! ! " " ! " " !

! " ! ! ! " " "

! " ! " " ! ! !

! " " ! " ! ! "

! " " " " ! " !

" ! ! ! " ! " "

" ! ! " " " ! !

" ! " !

" ! " " X X

X X X X

X X X X

X X X X

X X X X

" " ! !

" " ! "

" " " !

" " " "