Chapter #2: Two-Level Combinational Logic

description

Transcript of Chapter #2: Two-Level Combinational Logic

No. 2-1

Chapter #2: Two-Level Combinational Logic

No. 2-2

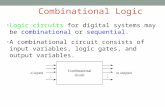

Motivation

Rapid prototyping technology

Use of computer aided design tools: espresso

Design Techniques that Spanning Multiple Technologies

Transistor-Transistor Logic (TTL)

Complementary Metal on Oxide Silicon (CMOS)

Multiple Design Representations

Truth Tables

Static gate descriptions

Dynamic waveform descriptions

Further Amplification on the Concepts of Chapter #1:

No. 2-3

Chapter Overview

Logic Functions and Switches

Not, AND, OR, NAND, NOR, XOR, XNOR

Gate Logic

Laws and Theorems of Boolean Algebra

Two Level Canonical Forms

Incompletely Specified Functions

Two Level Simplification

Boolean Cubes

Karnaugh Maps

Quine-McClusky Method

Espresso Method

No. 2-4

Logic Functions: Boolean Algebra

is Algebraic structure consisting of:

set of elements B

binary operations {+, •}

unary operation {'}

such that the following axioms hold:

1. B contains at least two elements, a, b, such that a ≠ b

2. Closure a,b in B, (i) a + b in B (ii) a • b in B

3. Commutative Laws: a,b in B, (i) a + b = b + a (ii) a • b = b • a

4. Identities: 0, 1 in B (i) a + 0 = a (ii) a • 1 = a

5. Distributive Laws: (i) a + (b • c) = (a + b) •(a + c) (ii) a •(b + c) = a b + a • c

6. Complement: (i) a + a' = 1 (ii) a • a' = 0

No. 2-5

Logic Functions: Boolean AlgebraNote that B = {0,1}, + = OR, • = AND, ' = NOT is a Boolean Algebra

must verify that the axioms hold:E.g., Commutative Law:

0 + 1 = 1 + 0 1 = 1

0 • 1 = 1 • 0 0 = 0

Theorem: any Boolean function that can be expressed as a truth table can be written as an expression in Boolean Algebra using ', +, •

Reviewfrom

Chapter 1

X Y

Description Z = 1 if X and Y are both 1

Gates Truth Table Switches

XY

ZY 0 1 0 1

X 0 0 1 1

Z 0 0 0 1

X • Y

false

true

NOT

AND

OR

Description If X = 0 then X ' = 1 If X = 1 then X ' = 0

Switches Gates

X

X X 0 1

X 1 0

T ruth T able

X T rue

False X

Description Z = 1 if X or Y (or both) are 1

Gates T ruth T able Switches X Y Z X

0 0 1 1

Y 0 1 0 1

Z 0 1 1 1

X Y

X + Y

False

T rue

No. 2-6

Logic Functions: From Expressions to GatesMore than one way to map an expression to gates

E.g., Z = A' • B' •(C + D) = (A' •(B' •(C + D)))

T1

T2

Literal: each appearance of a variable or its complement in an expression

E.g., Z = A B' C + A' B + A' B C' + B' C

use of 3-input gate

3 variables, 10 literals

A

B

C

D T

2

T 1

Z

Z

A

B

C

D

No. 2-7

Description Z = 1 if X is 0 or Y is 0

Gates T ruth T able Switches

X Y

X • Y

False

T rue X 0 0 1 1

Y 0 1 0 1

Z 1 1 1 0

X Y

Z

F0 0 0 0 0

F1 0 0 0 1

F2 0 0 1 0

F3 0 0 1 1

F4 0 1 0 0

F5 0 1 0 1

F6 0 1 1 0

F7 0 1 1 1

F8 1 0 0 0

F9 1 0 0 1

F10 1 0 1 0

F1 1 1 0 1 1

F12 1 1 0 0

F13 1 1 0 1

F14 1 1 1 0

F15 1 1 1 1

X 0 0 1 1

Y 0 1 0 1

0 X • Y X Y X + Y X Y

1

Logic Functions: NAND, NOR, XOR, XNOR16 functions of two variables:

X, X', Y, Y', X • Y, X+Y, 0, 1 only half of the possible functions

NAND

NORDescription Z = 1 if both X and Y are 0

Gates T ruth T able Switches X

Y Z X

0 0 1 1

Y 0 1 0 1

Z 1 0 0 0

X Y

X + Y False

T rue

•

No. 2-8

Logic Functions: NAND, NOR Implementation

NAND, NOR gates far outnumber AND, OR in typical designs

easier to construct in the underlying transistor technologies

Any Boolean expression can be implemented by NAND, NOR, NOT gates

In fact, NOT is superfluous (NOT = NAND or NOR with both inputs tied together)

X0

1

Y0

1

X NOR Y1

0

X0

1

Y0

1

X NAND Y1

0

No. 2-9

Logic Functions: XOR, XNORXOR: X or Y but not both ("inequality", "difference")XNOR: X and Y are the same ("equality", "coincidence")

X Y = X Y' + X' Y X Y = X Y + X' Y'

(a) XOR (b) XNOR

Description Z = 1 if X has a different value than Y

Gates

T ruth T able

X

Y Z

X 0 0 1 1

Y 0 1 0 1

Z 0 1 1 0

Description Z = 1 if X has the same value as Y

Gates

T ruth T able

X

Y Z

X 0 0 1 1

Y 0 1 0 1

Z 1 0 0 1

No. 2-10

Logic Functions: Waveform View

No. 2-11

Logic Functions: Rationale for Simplification

Logic Minimization: reduce complexity of the gate level implementation

reduce number of literals (gate inputs)

reduce number of gates

reduce number of levels of gates

fewer inputs implies faster gates in some technologies

fan-ins (number of gate inputs) are limited in some technologies

fewer levels of gates implies reduced signal propagation delays

minimum delay configuration typically requires more gates

number of gates (or gate packages) influences manufacturing costs

Traditional methods: reduce delay at expense of adding gates

New methods: trade off between increased circuit delay and reduced gate count

Traditional methods: reduce delay at expense of adding gates

New methods: trade off between increased circuit delay and reduced gate count

No. 2-12

Logic Functions: Alternative Gate Realizations

Two-Level Realization(inverters don't count)

Multi-Level RealizationAdvantage: Reduced Gate

Fan-ins

Complex Gate: XORAdvantage: Fewest Gates

Number of gates: Z1 - 3x inverters, 3x 3-input AND, 1x 3-input OR Z2 - 2x inverters, 3x 2-input AND, 1x 2-input OR Z3 - 1x 2-input AND, 1x 2-input XOR

0 1 0 1 0 1

A B C

0

0

Z 1

Z 2

Z 3

0

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Z 0 1 0 1 0 1 1 0

No. 2-13

Logic Functions: Waveform Verification

Under the same input stimuli, the three alternative implementations have essentially the same waveform behavior.

Slight delay variations due to differences in number of gate levels

The three implementations are equivalent

There are some glitches in all of them!

No. 2-14

Gate Logic: Laws of Boolean AlgebraDuality: a dual of a Boolean expression is derived by replacing AND operations by ORs, OR operations by ANDs, constant 0s by 1s, and 1s by 0s (literals, I.e., inputs are left unchanged).

Any statement that is true for an expression is also true for its dual!

Useful Laws/Theorems of Boolean Algebra:

Operations with 0 and 1:

Idempotent Law:

Involution Law:

Laws of Complementarity:

Commutative Law:

1. X + 0 = X2. X + 1 = 1

1D. X • 1 = X2D. X • 0 = 0

3. X + X = X 3D. X • X = X

4. (X')' = X

5. X + X' = 1 5D. X • X' = 0

6. X + Y = Y + X 6D. X • Y = Y • X

No. 2-15

Gate Logic: Laws of Boolean Algebra (cont)

Distributive Laws:

Simplification Theorems:

DeMorgan's Law:

Duality:

Theorems for Multiplying and Factoring:

Consensus Theorem:

8. X •(Y+ Z) = (X • Y) + (X • Z) 8D. X + (Y • Z) = (X + Y) •(X + Z)

9. X • Y + X • Y' = X10. X + X • Y = X11. (X + Y') • Y = X • Y

9D. (X + Y) • (X + Y') = X10D. X •(X + Y) = X11D. (X • Y') + Y = X + Y

12. (X + Y + Z + ...)' = X' • Y' • Z' •...13. {F(X1,X2,...,Xn,0,1,+, •}' = {F(X1',X2',...,Xn',1,0, • +)}

12D. (X • Y • Z •...) ' = X' + Y' + Z' + ...

14. (X + Y + Z + ...) = X • Y • Z •...

15. {F(X1,X2,...,Xn,0,1,+, •} = {F(X1,X2,...,Xn,1,0, • +)}

D

D

14D. (X • Y • Z •...) = X + Y + Z + ...D

16. (X + Y) •(X' + Z) = X • Z + X' • Y 16D. X • Y + X' • Z = (X + Z) •(X' + Y)

17. (X • Y) + (Y • Z) + (X' • Z) = X • Y + X' • Z

17D. (X + Y) •(Y + Z) •(X' + Z) = (X + Y) •(X' + Z)

Associative Laws:7. (X + Y) + Z = X + (Y + Z) = X + Y + Z

7D. (X • Y) • Z = X •(Y • Z) = X • Y • Z

No. 2-16

Gate Logic: Laws of Boolean AlgebraProving theorems via axioms of Boolean Algebra:

E.g., prove the theorem: X • Y + X • Y' = X

E.g., prove the theorem: X + X • Y = X

X • (Y +Y')=X= X •1= X

dist, law 8complementarity theorem 5identity (1D)

X •1+ X •Y= X • (1+Y)= X •1= X

identity 1Ddistidentity 2identity 1D

No. 2-17

Gate Logic: Laws of Boolean AlgebraProving theorems via axioms of Boolean Algebra:

E.g., prove the theorem: X • Y + X • Y' = X

X • Y + X • Y' = X •(Y + Y')

X •(Y + Y') = X •(1)

X •(1) = X

distributive law (8)

complementary law (5)

identity (1D)

E.g., prove the theorem: X + X • Y = X

X + X • Y = X • 1 + X • Y

X • 1 + X • Y = X •(1 + Y)

X •(1 + Y) = X •(1)

X •(1) = X

identity (1D)

distributive law (8)

identity (2)

identity (1)

No. 2-18

Gate Logic: Laws of Boolean AlgebraDeMorgan's Law

(X + Y)' = X' • Y'

(X • Y)' = X' + Y'

NOR is equivalent to ANDwith inputs complemented

NAND is equivalent to ORwith inputs complemented

Example:Z = A' B' C + A' B C + A B' C + A B C'

Z' = (A + B + C') • (A + B' + C') • (A' + B + C') •(A' + B' + C)

DeMorgan's Law can be used to convert AND/OR expressionsto OR/AND expressions

DeMorgan's Law can be used to convert AND/OR expressionsto OR/AND expressions

X 0 0 1 1

Y 0 1 0 1

X 1 1 0 0

Y 1 0 1 0

X + Y 1 0 0 0

X•Y 1 0 0 0

X 0 0 1 1

Y 0 1 0 1

X 1 1 0 0

Y 1 0 1 0

X + Y 1 1 1 0

X•Y 1 1 1 0

No. 2-19

Gate Logic: Laws of Boolean AlgebraApply the laws and theorems to simplify Boolean equations

Example: full adder's carry out function

Cout = A' B Cin + A B' Cin + A B Cin' + A B Cin

No. 2-20

Gate Logic: Laws of Boolean AlgebraApply the laws and theorems to simplify Boolean equations

Example: full adder's carry out function

Cout = A' B Cin + A B' Cin + A B Cin' + A B Cin

= A' B Cin + A B' Cin + A B Cin' + A B Cin + A B Cin

= A' B Cin + A B Cin + A B' Cin + A B Cin' + A B Cin

= (A' + A) B Cin + A B' Cin + A B Cin' + A B Cin

= (1) B Cin + A B' Cin + A B Cin' + A B Cin

= B Cin + A B' Cin + A B Cin' + A B Cin + A B Cin

= B Cin + A B' Cin + A B Cin + A B Cin' + A B Cin

= B Cin + A (B' + B) Cin + A B Cin' + A B Cin

= B Cin + A (1) Cin + A B Cin' + A B Cin

= B Cin + A Cin + A B (Cin' + Cin)

= B Cin + A Cin + A B (1)

= B Cin + A Cin + A B

identity

associative

No. 2-21

A + 0 = A A + 1 = 1

A A

0

=

A 1

=

1

Gate Logic: Switching Equivalents

Idempotent Laws Identity Laws

Complementarity Laws Simplification Theorems

A • A = A

A A

A

A

A

A + A = A

= =

A

A + A = 1 A • A = 0

A

A

=

1

A A

=

0

X Y + X Y = X X + X Y = X

X Y

X Y

X Y

X

= =

X X

No. 2-22

Gate Logic: 2-Level Canonical Forms

Truth table is the unique signature of a Boolean function

Many alternative expressions (and gate realizations) may have the same truth table

Canonical form: standard form for a Boolean expression provides a unique algebraic signature

Sum of Products Formalso known as disjunctive normal form, minterm expansion

F = A' B C + A B' C' + A B' C + A B C' + A B C0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

F' = A' B' C' + A' B' C + A' B C'

F 0 0 0 1 1 1 1 1

F 1 1 1 0 0 0 0 0

C 0 1 0 1 0 1 0 1

B 0 0 1 1 0 0 1 1

A 0 0 0 0 1 1 1 1

No. 2-23

Gate Logic: Two Level Canonical Forms

Sum of Products

Shorthand Notation forMinterms of 3 Variables

minterm:

ANDed product of literals in which eachvariable appears exactly once, in true orcomplemented form (but not both!)

F in canonical form:

F(A,B,C) = m(3,4,5,6,7)= m3 + m4 + m5 + m6 + m7= A' B C + A B' C' + A B' C + A B C' + A B C

Minimized gate-level implementation

F = A B' (C + C') + A' B C + A B (C' + C)

= A B' + A' B C + A B

= A (B' + B) + A' B C

= A + A' B C

= A + B C2-Level AND/OR

Realization F' = (A + B C)' = A' (B' + C') = A' B' + A' C'

B

C

A

F

A B C = m 1 A B C = m 2 A B C = m 3 A B C = m 4 A B C = m 5 A B C = m 6 A B C = m 7

A

0 0 0 0 1 1 1 1

B

0 0 1 1 0 0 1 1

C

0 1 0 1 0 1 0 1

Minterms

A B C = m 0

product terms

Minterm product term

No. 2-24

Gate Logic: 2 Level Canonical Forms

Product of Sums / Conjunctive Normal Form / Maxterm Expansion

Maxterm Shorthand Notationfor a Function of Three Variables

Maxterm:ORed sum of literals in which eachvariable appears exactly once in eithertrue or complemented form, but not both!

Maxterm form:Find truth table rows where F is 00 in input column implies true literal1 in input column implies complemented literal

F(A,B,C) = M(0,1,2)

= (A + B + C) (A + B + C') (A + B' + C)

F'(A,B,C) = M(3,4,5,6,7)

= (A + B' + C') (A' + B + C) (A' + B + C') (A' + B' + C) (A' + B' + C')

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Maxterms A + B + C = M 0 A + B + C = M 1 A + B + C = M 2 A + B + C = M 3 A + B + C = M 4 A + B + C = M 5 A + B + C = M 6 A + B + C = M 7

No. 2-25

Gate Logic: Two Level Canonical FormsSum of Products, Products of Sums, and DeMorgan's Law

F' = A' B' C' + A' B' C + A' B C'

Apply DeMorgan's Law to obtain F:

(F')' = (A' B' C' + A' B' C + A' B C')'

F = (A + B + C) (A + B + C') (A + B' + C)

F' = (A + B' + C') (A' + B + C) (A' + B + C') (A' + B' + C) (A' + B' + C')

(F')' = {(A + B' + C') (A' + B + C) (A' + B + C') (A' + B' + C) (A' + B' + C')}'

F = A' B C + A B' C' + A B' C + A B C' + A B C

Apply DeMorgan's Law to obtain F:

No. 2-26

Gate Logic: Two-Level Canonical FormsFour Alternative Implementations of F:

Canonical Sum of Products

Minimized Sum of Products(simplest)

Canonical Products of Sums

Minimized Products of Sums

A

B

F 2

F 3

F 4

F 1 C

No. 2-27

Gate Logic: Two-Level Canonical FormsWaveform Verification of the Three Alternatives

Eight Unique Combinationsof Three Inputs

Except for short-duration glitches,output waveforms of thefour implementations are

essentially identical

100 200

A

B

C

F 1

F 2

F 3

No. 2-28

Gate Logic: Two-Level Canonical FormsMapping Between Forms

1. Minterm to Maxterm conversion: rewrite minterm shorthand using maxterm shorthand replace minterm indices with the indices not already used

E.g., F(A,B,C) = m(3,4,5,6,7) = M(0,1,2)

2. Maxterm to Minterm conversion:rewrite maxterm shorthand using minterm shorthandreplace maxterm indices with the indices not already used

E.g., F(A,B,C) = M(0,1,2) = m(3,4,5,6,7)

3. Minterm expansion of F to Minterm expansion of F':in minterm shorthand form, list the indices not already used in F

E.g., F(A,B,C) = m(3,4,5,6,7) F'(A,B,C) = m(0,1,2) = M(0,1,2) = M(3,4,5,6,7)

4. Minterm expansion of F to Maxterm expansion of F':rewrite in Maxterm form, using the same indices as F

E.g., F(A,B,C) = m(3,4,5,6,7) F'(A,B,C) = M(3,4,5,6,7) = M(0,1,2) = m(0,1,2)

The same goes to Maxterm case

No. 2-29

Gate Logic: Positive vs. Negative LogicNormal Convention: Postive Logic/Active High

Low Voltage = 0; High Voltage = 1

Alternative Convention sometimes used: Negative Logic/Active Low

Behavior in termsof Electrical Levels

Two Alternative InterpretationsPositive Logic ANDNegative Logic OR

Dual Operations

Negative Logic Positive Logic V oltage T ruth T able

F low low low high

F 0 0 0 1

F 1 1 1 0

A low low high high

B low high low high

B 0 1 0 1

A 0 0 1 1

A 1 1 0 0

B 1 0 1 0

F

No. 2-30

Gate Logic: Positive vs. Negative LogicConversion from Positive to Negative Logic

Positive Logic NOR: A + B = A • B

Negative Logic NAND: A • B = A + B

Dual operations: AND becomes OR, OR becomes AND Complements remain unchanged

Negative Logic Positive Logic V oltage T ruth T able

F high low low low

F 1 0 0 0

F 0 1 1 1

A low low high high

B low high low high

B 0 1 0 1

A 0 0 1 1

A 1 1 0 0

B 1 0 1 0

F

No. 2-31

(c)

Change Request

(active low)

T imer Expired

(active low)

Change Lights

(active low)

Bubble Mismatch

(d)

(a)

Change Request

(active high)

T imer Expired

(active high)

Change Lights

(active high)

Active High

(b)

Change Request

(active low)

T imer Expired

(active low)

Change Lights

(active low)

Active Low

Change Request

(active low)

T imer Expired

(active low)

Change Lights

(active low)

Bubble Match

Gate Logic: Positive vs. Negative LogicPractical Example

Mismatch betweeninput and outputlogic polarities

Use NAND w/ invertedinputs if negative logic

Use OR gate if inputpolarities are neg. logic

Use AND gateif active high

A + B = ((A + B)')' = (A' • B')'

No. 2-32

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

W 0 0 0 0 0 0 0 1 1 0 X X X X X X

X 0 0 0 1 1 1 1 0 0 0 X X X X X X

Y 0 1 1 0 0 1 1 0 0 0 X X X X X X

Z 1 0 1 0 1 0 1 0 1 0 X X X X X X

Gate Logic: Incompletely Specified Functionsn input functions have 2 possible input configurations

for a given function, not all input configurations may be possible

this fact can be exploited during circuit minimization!

E.g., Binary Coded Decimal Digit Increment by 1BCD digits encode the decimal digits 0 - 9 in the bit patterns 0000 - 1001

n

2 2

These input patterns shouldnever be encountered in practice

associated output values are"Don't Cares"

Off-set of W

On-set of W

Don't care (DC) set of W

No. 2-33

Gate Logic: Incompletely Specified FunctionsDon't Cares (d) and Canonical Forms

Z = m0 + m2 + m4 + m6 + m8 + d10 + d11 + d12 + d13 + d14 + d15

Z = m(0, 2, 4, 6, 8) + d(10, 11, 12 ,13, 14, 15)

Z = M1 • M3 • M5 • M7 • M9 • D10 • D11 • D12 • D13 • D14 • D15

Z= M(1, 3, 5, 7, 9) • D(10, 11, 12, 13, 14 ,15)

Canonical Representations of the BCD Increment by 1 Function:

No. 2-34

Gate Logic: Two-Level SimplificationAlgebraic Simplification:

not an algorithm/systematic procedure

how do you know when the minimum realization has been found?

Computer-Aided Tools:

precise solutions require very long computation times, especially for functions with many inputs (>10)

heuristic methods employed ? "educated guesses" to reduce the amount of computation good solutions not best solutions

Still Relevant to Learn Hand Methods:

insights into how the CAD programs work, and their strengths and weaknesses

ability to check the results, at least on small examples

don't have computer terminals during exams!!!

No. 2-35

A 0 0 1 1

B 0 1 0 1

G 1 0 1 0

A 0 0 1 1

B 0 1 0 1

F 0 0 1 1

Gate Logic: Two-Level Simplification

Key Tool: The Uniting Theorem - A (B' + B) = AKey Tool: The Uniting Theorem - A (B' + B) = A

F = A B' + A B = A (B' + B) = A

A's values don't change within the on-set rows

B's values change within the on-set rows

G = A' B' + A B' = (A' + A) B' = B'

B's values stay the same within the on-set rows

A's values change within the on-set rows

B is eliminated, A remains

A is eliminated, B remains

Essence of Simplification:find two element subsets of the ON-set where only one variable changes its value. This single varying variable can be eliminated!

No. 2-36

Gate Logic: Two-Level SimplificationBoolean Cubes

Visual technique for identifying when the Uniting Theorem can be applied

Just another way torepresent the truth table

n input variables =n dimensional "cube"

2-cube 3-cube

4-cube

XYZ

X

011

010

000

001

111

110

100

101 Y Z

WXYZ

0111 0011

0010

0000

0001

0110

1010

0101

0100 1000

1011

1001

1110

1111

1101

1100

Y Z

W

X

XY

1-cube

X

X

01

00

11

10

Y

0 1

No. 2-37

Gate Logic: Two-Level Simplification

Mapping Truth Tables onto Boolean Cubes

ON-set = filled-in nodes

OFF-set = empty nodes

DC-set = X'd nodes

F

G

A asserted and unchanged

B varies within loop

A varies within loop

B complemented and unchanged

Adjacency plane

reduces expression

01 11

10 00

B

A

01 11

10 00

A

B

No. 2-38

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

A

B

Cin 0 1 0 1 0 1 0 1

Cout 0 0 0 1 0 1 1 1

011 111

010 110

001

000 100

101 Cin

Gate Logic: Two-Level SimplificationThree variable example: Full Adder Carry Out

(A' + A) B Cin

A B (Cin' + Cin)

A (B + B') Cin

Cout = B Cin + A B + A Cin

The ON-set is coveredby the OR of the subcubes

of lower dimensionality

No. 2-39

011 111

101

100

110 010

001

000

B

C

A

Gate Logic: Two-Level Simplification

Subcubes (or adjacency plane) of Higher Dimensions than 1

F(A,B,C) = m(4,5,6,7)

On-set forms a rectangle, i.e., a cube of two dimensions

represents an expression in one variable i.e., 3 dimensions - 2 dimensions

A is asserted and unchangedB and C vary (A=1)

This subcube represents theliteral A

No. 2-40

Gate Logic: Two-Level SimplificationIn a 3-cube:

a 0-cube, i.e., a single node, yields a term in three literals

a 1-cube, i.e., a line of two nodes, yields a term in two literals

a 2-cube, i.e., a plane of four nodes, yields a term in one literal

a 3-cube, i.e., a cube of eight nodes, yields a constant term "1"

In general,

an m-subcube within an n-cube (m < n) yields a term with n - m literals

attempts to find the smallest number of the highest-dimensionality adjacency planes that contain all the nodes of the function’s on-set.

CAD algorithm for minimization,

No. 2-41

A B 0 1

0

1

0

1

2

3

0

1

2

3

6

7

4

5

AB C

0

1

3

2

4

5

7

6

12

13

15

14

8

9

11

10

A

B

AB

CD

A

00 01 11 10

0

1

00 01 11 00

00

01

11

10 C

B

D

Gate Logic: Two-Level SimplificationKarnaugh Map Method

hard to draw cubes of more than 4 dimensions

K-map is an alternative method of representing the truth table that helps visualize adjacencies in up to 6 dimensions

Beyond that, computer-based methods are needed

2-variableK-map

3-variableK-map

4-variableK-map

Numbering Scheme: 00, 01, 11, 10Gray Code - only a single bit changes from code word to next code word

Should be 10

No. 2-42

Gate Logic: Two-Level SimplificationKarnaugh Map Method

Adjacencies in the K-Map

Wrap from first to last column

Top row to bottom row

000

001

010

01 1

1 10

1 1 1

100

101

00 01 11 10

0

1

AB C

A

B

011

010

000

001

100

110

101

111

B

C

A

No. 2-43

Gate Logic: Two-Level SimplificationK-Map Method Examples

F = ?

A asserted, unchangedB varies

G = ?

B complemented, unchangedA varies

Cout = ? F(A,B,C) = ?

A

B 0 1

0 1

0 1

0

1

A

B 0 1

1 1

0 0

0

1

A B A

B

Cin 00 01 11 10

0

1

0

0

0

1

1

1

0

1

AB C

A

00 01 11 10

0

1

0

0

0

0

1

1

1

1

B

No. 2-44

Gate Logic: Two-Level SimplificationK-Map Method Examples

F = A

A asserted, unchangedB varies

G = B'

B complemented, unchangedA varies

Cout = AB + Bcin + ACin F(A,B,C) = A

A

B 0 1

0 1

0 1

0

1

A

B 0 1

1 1

0 0

0

1

A B A

B

Cin 00 01 11 10

0

1

0

0

0

1

1

1

0

1

AB C

A

00 01 11 10

0

1

0

0

0

0

1

1

1

1

B

No. 2-45

Gate Logic: Two-Level SimplificationMore K-Map Method Examples, 3 Variables

F(A,B,C) = m(0,4,5,7)

F =

F'(A,B,C) = m(1,2,3,6)

F' =

F' simply replace 1's with 0's and vice versa

00 C

AB 01 11 10

1 0 0 1

1 1 0 0

A

B

0

1

00 C

AB

01 11 10

0 1 1 0

0 0 1 1

A

B

0

1

No. 2-46

Gate Logic: Two-Level SimplificationMore K-Map Method Examples, 3 Variables

F(A,B,C) = m(0,4,5,7)

F = B' C' + A C

In the K-map, adjacency wraps from left to rightand from top to bottom

F'(A,B,C) = m(1,2,3,6)

F' = B C' + A' C

Compare with the method of using DeMorgan's Theorem and Boolean Algebra to reduce the complement!

F' simply replace 1's with 0's and vice versa

00 C

AB 01 11 10

1 0 0 1

1 1 0 0

A

B

0

1

00 C

AB

01 11 10

0 1 1 0

0 0 1 1

A

B

0

1

Why not group m4 and m5?

No. 2-47

Gate Logic: Two-Level Simplification

K-map Method Examples: 4 variables

F(A,B,C,D) = m(0,2,3,5,6,7,8,10,11,14,15)

F =

AB 00 01 11 10

1 0 0 1

0 1 0 0

1 1 1 1

1 1 1 1

00

01

11

10 C

CD

A

D

B

No. 2-48

Gate Logic: Two-Level Simplification

K-map Method Examples: 4 variables

F(A,B,C,D) = m(0,2,3,5,6,7,8,10,11,14,15)

F = C + A' B D + B' D'

K-map Corner AdjacencyIllustrated in the 4-Cube

Find the smallest numberof the largest possible

subcubes that cover theON-set

AB 00 01 11 10

1 0 0 1

0 1 0 0

1 1 1 1

1 1 1 1

00

01

11

10 C

CD

A

D

B

0011

D

0010

0000

0111

0110

0001 C

A

B 0100 1000

1100

1101

1111

1110

1001

1011

1010

0101

No. 2-49

Gate Logic: Two-Level Simplification

K-map Method: Circling Zeros to get product of sums form

AB 00 01 11 10

1 0 0 1

0 1 0 0

1 1 1 1

1 1 1 1

00

01

11

10 C

CD

A

D

B

F = (B + C + D) (A + C + D) (B + C + D)

F = B C D + A C D + B C D

F = B C D + A C D + B C D

F = (B + C + D) (A + C + D) (B + C + D)

Replace F by F, 0’s become 1’s and vice versa

No. 2-50

Gate Logic: Two-Level Simplification

K-map Example: Don't Cares

F(A,B,C,D) = m(1,3,5,7,9) + d(6,12,13)

F = w/o don't cares

F = w/ don't cares

Don't Cares can be treated as 1's or 0's if it is advantageous to do soDon't Cares can be treated as 1's or 0's if it is advantageous to do so

AB 00 01 11 10

0 0 X 0

1 1 X 1

1 1 0 0

0 X 0 0

00

01

11

10 C

CD

A

D

B

No. 2-51

Gate Logic: Two-Level Simplification

K-map Example: Don't Cares

F(A,B,C,D) = m(1,3,5,7,9) + d(6,12,13)

F = A'D + B' C' D w/o don't cares

F = C' D + A' D w/ don't cares

Don't Cares can be treated as 1's or 0's if it is advantageous to do soDon't Cares can be treated as 1's or 0's if it is advantageous to do so

By treating this DC as a "1", a 2-cubecan be formed rather than one 1-cube

AB 00 01 11 10

0 0 X 0

1 1 X 1

1 1 0 0

0 X 0 0

00

01

11

10 C

CD

A

D

B AB

00 01 11 10

0 0 X 0

1 1 X 1

1 1 0 0

0 X 0 0

00

01

11

10 C

CD

A

D

B

In Product of Sums form: F = D (A' + C')

Same answer as above, but fewer literals

No. 2-52

Gate Logic: Two-Level SimplificationDesign Example: Two Bit Comparator

Block Diagramand

Truth Table

A 4-Variable K-mapfor each of the 3output functions

F 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

F 2 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0

F 3 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

B 0 1 0 1

A 0 0 1 1

=, >, < F 1 A B = C D F 2 A B < C D F 3 A B > C D

A B

C D

N 1

N 2

No. 2-53

Gate Logic: Two-Level SimplificationDesign Example: Two Bit Comparator

F1 =

F2 =

F3 =

AB 00 01 11 10

1 0 0 0

0 1 0 0

0 0 1 0

0 0 0 1

00

01

11

10 C

CD

A

D

B

K-map for F 1

AB 00 01 11 10

0 0 0 0

1 0 0 0

1 1 0 1

1 1 0 0

00

01

11

10 C

CD

A

D

B

K-map for F 2

AB 00 01 11 10

0 1 1 1

0 0 1 1

0 0 0 0

0 0 1 0

00

01

11

10 C

CD

A

D

B

K-map for F 3

No. 2-54

Gate Logic:Two-Level SimplificationDesign Example: Two Bit Comparator

F1 = A' B' C' D' + A' B C' D + A B C D + A B' C D'

F2 = A' B' D + B' C D + A' C

F3 = B C' D' + A C' + A B D'

= (A xnor C) (B xnor D) much simpler, but not in sum of products form1’s on K-map diagonals make XOR or XNOR

AB 00 01 11 10

1 0 0 0

0 1 0 0

0 0 1 0

0 0 0 1

00

01

11

10 C

CD

A

D

B

K-map for F 1

AB 00 01 11 10

0 0 0 0

1 0 0 0

1 1 0 1

1 1 0 0

00

01

11

10 C

CD

A

D

B

K-map for F 2

AB 00 01 11 10

0 1 1 1

0 0 1 1

0 0 0 0

0 0 1 0

00

01

11

10 C

CD

A

D

B

K-map for F 3

No. 2-55

Gate Logic: Two-Level Simplification

Design Example: Two Bit Adder

Block Diagramand

Truth Table

A 4-variable K-mapfor each of the 3output functions

+ N 3

X 0 0 0 0 0 0 0 1 0 0 1 1 0 1 1 1

Y 0 0 1 1 0 1 1 0 1 1 0 0 1 0 0 1

Z 0 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

B 0 1 0 1

A 0 0 1 1

A B

C D

N 1

N 2

X Y Z

No. 2-56

Gate Logic: Two-Level SimplificationDesign Example (Continued)

X =

Z =

Y =

AB 00 01 11 10

0 0 0 0

0 0 1 0

0 1 1 1

0 0 1 1

00

01

11

10 C

CD

A

D

B

K-map for X

AB 00 01 11 10

0 0 1 1

0 1 0 1

1 0 1 0

1 1 0 0

00

01

11

10 C

CD

A

D

B

K-map for Y

AB 00 01 11 10

0 1 1 0

1 0 0 1

1 0 0 1

0 1 1 0

00

01

11

10 C

CD

A

D

B

K-map for Z

No. 2-57

Gate Logic: Two-Level SimplificationDesign Example (Continued)

X = A C + B C D + A B D

Z = B D' + B' D = B xor D

Y = A' B' C + A B' C' + A' B C' D + A' B C D' + A B C' D' + A B C D

= B' (A xor C) + A' B (C xor D) + A B (C xnor D)

= B' (A xor C) + B (A xor C xor D)gate countreduced if

XOR available

1's on diagonal suggest XOR!

AB 00 01 11 10

0 0 0 0

0 0 1 0

0 1 1 1

0 0 1 1

00

01

11

10 C

CD

A

D

B

K-map for X

AB 00 01 11 10

0 0 1 1

0 1 0 1

1 0 1 0

1 1 0 0

00

01

11

10 C

CD

A

D

B

K-map for Y

AB 00 01 11 10

0 1 1 0

1 0 0 1

1 0 0 1

0 1 1 0

00

01

11

10 C

CD

A

D

B

K-map for Z

No. 2-58

\ D \ A \ C

Y 1

A

C

D

\ B

B

Y 2

Gate Logic: Two-Level SimplificationDesign Example (Continued)

Two alternativeimplementations of Ywith and without XOR

Note: XOR typicallyrequires 4 NAND gates

to implement!

X XOR Y

X

Y

No. 2-59

Gate Logic: Two-Level SimplificationDesign Example: Binary-Coded Decimal (BCD) Increment By 1

W =

X =

Y =

Z =

AB 00 01 11 10

0 0 X 1

0 0 X 0

0 1 X X

0 0 X X

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

0 1 X 0

0 1 X 0

1 0 X X

0 1 X X

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

0 0 X 0

1 1 X 0

0 0 X X

1 1 X X

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

1 1 X 1

0 0 X 0

0 0 X X

1 1 X X

00

01

11

10 C

CD

A

D

B

Z Y

X W

No. 2-60

Gate Logic: Two-Level Simplification

W = B C D + A D'

X = B C' + B D' + B' C D

Y = A' C' D + C D'

Z = D'

AB 00 01 11 10

0 0 X 1

0 0 X 0

0 1 X X

0 0 X X

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

0 1 X 0

0 1 X 0

1 0 X X

0 1 X X

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

0 0 X 0

1 1 X 0

0 0 X X

1 1 X X

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

1 1 X 1

0 0 X 0

0 0 X X

1 1 X X

00

01

11

10 C

CD

A

D

B

Z Y

X W

No. 2-61

Gate Logic: Two Level SimplificationDefinition of Terms

implicant: single element of the ON-set or any group of elements that can be combined together in a K-map (= adjacency plane)

prime implicant: implicant that cannot be combined with another implicant to eliminate a term

essential prime implicant: if an element of the ON-set is covered by a single prime implicant, it is an essential prime

Objective:

grow implicants into prime implicants

cover the ON-set with as few prime implicants as possible

essential primes participate in ALL possible covers

No. 2-62

Gate Logic: Two Level Simplication Examples to Illustrate Terms

6 Prime Implicants:

A' B' D, B C', A C, A' C' D, A B, B' C D

Essential

Minimum cover = essential implicants + one more prime implicant= B C' + A C + A' B' D

5 Prime Implicants:

B D, A B C', A C D, A' B C, A' C' D

essential

Essential implicants form minimum cover= A B C‘ + A C D + A' B C + A' C' D

AB 00 01 11 10

0 1 1 0

1 1 1 0

1 0 1 1

0 0 1 1

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

0 0 1 0

1 1 1 0

0 1 1 1

0 1 0 0

00

01

11

10 C

CD

A

D

B

No. 2-63

Gate Logic: Two Level Simplification

More Examples

Prime Implicants:

B D, C D, A C, B' C

essential

Essential primes form the minimum cover= BD + AC + B' C

AB 00 01 11 10

0 0 0 0

0 1 1 0

1 1 1 1

1 0 1 1

00

01

11

10 C

CD

A

D

B

No. 2-64

Gate Logic: Two-Level SimplificationAlgorithm: Minimum Sum of Products Expression from a K-Map

Step 1: Choose an element of ON-set not already covered by an implicant

Step 2: Find "maximal" groupings of 1's and X's adjacent to that element.Remember to consider top/bottom row, left/right column, andcorner adjacencies. This forms prime implicants (always a powerof 2 number of elements).

Repeat Steps 1 and 2 to find all prime implicants

Step 3: Revisit the 1's in the K-map. If covered by a single primeimplicant, it is essential, and participates in final cover. The 1's itcovers do not need to be revisited

Step 4: If there remain 1's not covered by essential prime implicants, thenselect the smallest number of prime implicants that cover theremaining 1's

No. 2-65

Gate Logic: Two Level SimplificationExample: f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

Initial K-map

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

No. 2-66

Gate Logic: Two Level SimplificationExample: f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

Initial K-map Primes aroundA' B C' D'

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

No. 2-67

Gate Logic: Two Level SimplificationExample: f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

Initial K-map Primes aroundA' B C' D'

Primes aroundA B C' D

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

Note: don’t worry about the blue colored elements. I couldn’t fix the figures.

No. 2-68

Gate Logic: Two-Level SimplificationExample Continued

Primes aroundA B' C' D

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

No. 2-69

Gate Logic: Two-Level SimplificationExample Continued

Primes aroundA B' C' D'

Primes aroundA B C' D

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

No. 2-70

Gate Logic: Two-Level SimplificationExample Continued

Primes aroundA B' C' D'

Primes aroundA B C' D

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

AB 00 01 11 10

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

00

01

11

10 C

CD

A

D

B

Essential Primeswith Min Cover

(each element covered once)

No. 2-71

Gate Logic: Two-Level Simplification5-Variable K-maps

f(A,B,C,D,E) = m(2,5,7,8,10,13,15,17,19,21,23,24,29 31)

=

BC DE

BC DE

A =0

A =1

00 01 11 10 00

01

11

10

00 01 11 10 00

01

11

10

0 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

16 20 28 24

17 21 29 25

19 23 31 27

18 22 30 26

1

00

1

10

1

10 BC

DE 00 01 11

00

01

11

10

A=0

BC DE 00 01 11

01

11

10

A=1

1 1

1

1 1

1

1 1

1 1 1

No. 2-72

Gate Logic: Two-Level Simplification5-Variable K-maps

f(A,B,C,D,E) = m(2,5,7,8,10,13,15,17,19,21,23,24,29 31)

= C E + A B' E + B C' D' E' + A' C' D E'

BC DE 00 01 11 10

00

01

11

10

A=0

BC DE 00 01 11 10

00

01

11

10

A=1

1 1

1

1

1 1

1

1

1 1 1

1 1 1

BC DE

BC DE

A =0

A =1

00 01 11 10 00

01

11

10

00 01 11 10 00

01

11

10

0 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

16 20 28 24

17 21 29 25

19 23 31 27

18 22 30 26

No. 2-73

Gate Logic: Two Level Simplification6- Variable K-Maps

f(A,B,C,D,E,F) =m(2,8,10,18,24,

26,34,37,42,45,50,53,58,61)

=

CD EF

CD EF

AB =00

AB =01

00 01 11 10 00

01

11

10

00 01 11 10 00

01

11

10

0 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

16 20 28 24

17 21 29 25

19 23 31 27

18 22 30 26

CD EF

AB =11

00 01 11 10 00

01

11

10

48 52 60 56

49 53 61 57

51 55 63 59

50 54 62 58

CD EF

AB =10

00 01 11 10 00

01

11

10

32 36 44 40

33 37 45 41

35 39 47 43

34 38 46 42

CD EF

CD EF

AB =00

AB =01

00 01 11 10 00

01

11

10

00 01 11 10 00

01

11

10

CD EF

AB =11

00 01 11 10 00

01

11

10

CD EF

AB =10

00 01 11 10 00

01

11

10

1

1 1

1

1 1

1 1

1 1

1 1

1 1

No. 2-74

Gate Logic: Two Level Simplification6- Variable K-Maps

f(A,B,C,D,E,F) =m(2,8,10,18,24,

26,34,37,42,45,50,53,58,61)

= D' E F' + A D E' F+ A' C D' F'

CD EF

CD EF

AB =00

AB =01

00 01 11 10 00

01

11

10

00 01 11 10 00

01

11

10

0 4 12 8

1 5 13 9

3 7 15 11

2 6 14 10

16 20 28 24

17 21 29 25

19 23 31 27

18 22 30 26

CD EF

AB =11

00 01 11 10 00

01

11

10

48 52 60 56

49 53 61 57

51 55 63 59

50 54 62 58

CD EF

AB =10

00 01 11 10 00

01

11

10

32 36 44 40

33 37 45 41

35 39 47 43

34 38 46 42

CD EF

CD EF

AB =00

AB =01

00 01 11 10 00

01

11

10

00 01 11 10 00

01

11

10

CD EF

AB =11

00 01 11 10 00

01

11

10

CD EF

AB =10

00 01 11 10 00

01

11

10

1

1 1

1

1 1

1 1

1 1

1 1

1 1

No. 2-75

Gate Logic: CAD Tools for SimplificationQuine-McCluskey Method

Tabular method to systematically find all prime implicants

Implication Table

Column I 0000 0100 1000 0101 0110 1001 1010 0111 1101

1111

f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

Step 1: Fill Column 1 with ON-set and DC-set minterm indices. Group by number of 1's.

Stage 1: Find all prime implicants

No. 2-76

Gate Logic: CAD Tools for SimplificationQuine-McCluskey Method

Tabular method to systematically find all prime implicants

Implication Table

Column I Column II 0000 √ 0-00 -000 0100 √ 1000 √ 010- 01-0 0101 √ 100- 0110 √ 10-0 1001 √ 1010 √ 01-1 -101 0111 √ 011- 1101 √ 1-01

1111 √ -111 11-1

f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

Step 1: Fill Column 1 with ON-set and DC-set minterm indices. Group by number of 1's.

Step 2: Apply Uniting Theorem Compare elements of group w/ N 1's against those with N+1 1's. Differ by one bit implies adjacent. Eliminate variable and place in next column.

E.g., 0000 vs. 0100 yields 0-00 0000 vs. 1000 yields -000

When used in a combination, mark with a check. If cannot be combined, mark with a star. These are the prime implicants.

Repeat until no further combinations can be made.

Stage 1: Find all prime implicants

No. 2-77

Gate Logic: CAD Tools for SimplificationQuine-McCluskey Method

Tabular method to systematically find all prime implicants

Implication Table

Column I Column II Column III 0000 √ 0-00 * 01-- * -000 * 0100 √ -1-1 * 1000 √ 010- √ 01-0 √ 0101 √ 100- * 0110 √ 10-0 * 1001 √ 1010 √ 01-1 √ -101 √ 0111 √ 011- √ 1101 √ 1-01 *

1111 √ -111 √ 11-1 √

f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

Step 1: Fill Column 1 with ON-set and DC-set minterm indices. Group by number of 1's.

Step 2: Apply Uniting Theorem Compare elements of group w/ N 1's against those with N+1 1's. Differ by one bit implies adjacent. Eliminate variable and place in next column.

E.g., 0000 vs. 0100 yields 0-00 0000 vs. 1000 yields -000

When used in a combination, mark with a check. If cannot be combined, mark with a star. These are the prime implicants.

Repeat until no further combinations can be made.

Stage 1: Find all prime implicants

No. 2-78

Gate Logic: CAD Tools for SimplificationQuine-McCluskey Method Continued

Prime Implicants:

0-00 = A' C' D'

100- = A B' C'

1-01 = A C' D

-1-1 = B D

-000 = B' C' D'

10-0 = A B' D'

01-- = A' B

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

No. 2-79

Gate Logic: CAD Tools for SimplificationQuine-McCluskey Method Continued

Prime Implicants:

0-00 = A' C' D'

100- = A B' C'

1-01 = A C' D

-1-1 = B D

-000 = B' C' D'

10-0 = A B' D'

01-- = A' B

Stage 2: find smallest set of prime implicants that cover the ON-set

recall that essential prime implicants must be in all covers

another tabular method- the prime implicant chart

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

X 1 0 1

0 1 1 1

0 X X 0

0 1 0 1

No. 2-80

Gate Logic: CAD Tools for Simplification

rows = prime implicantscolumns = ON-set elementsplace an "X" if ON-set element is covered by the prime implicant

Prime Implicant Chart

No. 2-81

Gate Logic: CAD Tools for Simplification

rows = prime implicantscolumns = ON-set elementsplace an "X" if ON-set element is covered by the prime implicant

Prime Implicant Chart

If column has a single X, than theimplicant associated with the rowis essential. It must appear inminimum cover

No. 2-82

Gate Logic: CAD Tools for SimplificationPrime Implicant Chart (Continued)

Eliminate all columns covered byessential primes

No. 2-83

Gate Logic: CAD Tools for SimplificationPrime Implicant Chart (Continued)

Eliminate all columns covered byessential primes

Find minimum set of rows thatcover the remaining columns

f = A B' D' + A C' D + A' Bf = A B' D' + A C' D + A' B

No. 2-84

Gate Logic: CAD Tools for SimplificationESPRESSO Method (Berkeley Tool)

Problem with Quine-McCluskey: the number of prime implicants grows rapidly with the number of inputs

upper bound: 3 /n, where n is the number of inputsn

finding a minimum cover is NP-complete, i.e., a computational expensive process not likely to yield to any efficient algorithm

Espresso: trades solution speed for minimality of answer

don't generate all prime implicants (Quine-McCluskey Stage 1)

judiciously select a subset of primes that still covers the ON-set

operates in a fashion not unlike a human finding primes in a K-map

No. 2-85

Gate Logic: CAD Tools for SimplificationEspresso Method: Overview

1. Expands implicants to their maximum sizeImplicants covered by an expanded implicant are removed from further considerationQuality of result depends on order of implicant expansionHeuristic methods used to determine orderStep is called EXPAND

Irredundant cover (i.e., no proper subset is also a cover) is extracted from the expanded primesJust like the Quine-McCluskey Prime Implicant ChartStep is called IRREDUNDANT COVER

Solution usually pretty good, but sometimes can be improvedMight exist another cover with fewer terms or fewer literalsShrink prime implicants to smallest size that still covers ON-setStep is called REDUCE

Repeat sequence REDUCE/EXPAND/IRREDUNDANT COVER to find alternative prime implicantsKeep doing this as long as new covers improve on last solution

A number of optimizations are tried, e.g., identify and remove essential primes early in the process

2.

3.

4.

5.

No. 2-86

Gate Logic: CAD Tools for SimplificationEspresso Inputs and Outputs

.i 4

.o 1

.ilb a b c d

.ob f

.p 100100 10101 10110 11000 11001 11010 11101 10000 -0111 -1111 -.e

-- # inputs-- # outputs-- input names-- output name-- number of product terms-- A'BC'D'-- A'BC'D-- A'BCD'-- AB'C'D'-- AB'C'D-- AB'CD'-- ABC'D-- A'B'C'D' don't care-- A'BCD don't care-- ABCD don't care-- end of list

f(A,B,C,D) = m(4,5,6,8,9,10,13) + d(0,7,15)

Espresso Input Espresso Output

.i 4

.o 1

.ilb a b c d

.ob f

.p 31-01 110-0 101-- 1.e

f= A C' D + A B' D' + A' B

No. 2-87

Gate Logic: CAD Tools for Simplification

Espresso: Why Iterate on Reduce, Irredundant Cover, Expand?

Initial Set of Primes found bySteps1 and 2 of the Espresso

Method

4 primes, irredundant cover,but not a minimal cover!

Result of REDUCE:Shrink primes while still

covering the ON-set

Choice of order in which to perform shrink is important

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 1 0 0

1 1 1 1

0 0 1 1

1 1 1 1

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 1 0 0

1 1 1 1

0 0 1 1

1 1 1 1

No. 2-88

Gate Logic: CAD Tools for SimplificationEspresso Iteration (Continued)

Second EXPAND generates adifferent set of prime implicants

IRREDUNDANT COVER found byfinal step of espresso

Only three prime implicants!

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 1 0 0

1 1 1 1

0 0 1 1

1 1 1 1

AB

CD 00 01 11 10

00

01

11

10

D

B

C

A

1 1 0 0

1 1 1 1

0 0 1 1

1 1 1 1

No. 2-89

Practical Matters: Technology Metrics

• Bipolar: TTL (transistor-transistor logic) and ECL (emitter-coupled logic) families

• MOS (metal oxide semiconductor): CMOS (complementary MOS)

Metric Bipolar MOS

Gate delay Low Medium

Integration Low High

Power High Low

Noise Good Good

Cost Low Medium

Fan-out Fair Good

Drive Good Low

No. 2-90

Practical Matters: TTL Packaged Logic

• TTL (transister-transistor logic)

• 74-series components

• A logic family – can be interconnected w/o too much concern about electrical operation

No. 2-91

Practical Matters: TTL Packaged Logic

• Subfamilies – 74XX: standard

– 74HXX: higher speed, more power consumption

– 74LXX: lower speed

– 74SXX: Schottky TTL (S TTL)

– 74LSXX: low-power Schottky (LS TTL) √

– 74ASXX: advanced Schottky (AS TTL)

– 74ALSXX: advanced low-power Schottky (ALS TTL)

• Speed-Power product– Trade-off between speed and power consumption

Delay (nsec) Power (mW) Speed-Power Product

Standard 9 10 90

LS TTL 9 2 √ 18

ALS TTL 5 1.3 √ 6.5 √

S TTL 3 √ 20 60

AS TTL 1.6 √ 20 32

No. 2-92

Logic Functions: Alternative Gate Realizations

Two-Level Realization(inverters don't count)

Multi-Level RealizationAdvantage: Reduced Gate

Fan-ins

Complex Gate: XORAdvantage: Fewest Gates

Number of gates: Z1 - 3x inverters, 3x 3-input AND, 1x 3-input OR Z2 - 2x inverters, 3x 2-input AND, 1x 2-input OR Z3 - 1x 2-input AND, 1x 2-input XOR

0 1 0 1 0 1

A B C

0

0

Z 1

Z 2

Z 3

0

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Z 0 1 0 1 0 1 1 0

No. 2-93

Logic Functions: Alternative Gate Realizations

Two-Level Realization(inverters don't count)

Multi-Level RealizationAdvantage: Reduced Gate

Fan-ins

Complex Gate: XORAdvantage: Fewest Gates

TTL Package Counts: Z1 - three packages (1x 6-inverters, 1x 3-input AND, 1x 3-input OR) Z2 - three packages (1x 6-inverters, 1x 2-input AND, 1x 2-input OR) Z3 - two packages (1x 2-input AND, 1x 2-input XOR)

0 1 0 1 0 1

A B C

0

0

Z 1

Z 2

Z 3

0

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

C 0 1 0 1 0 1 0 1

Z 0 1 0 1 0 1 1 0

No. 2-94

Two-Level Logic: Summary

Primitive logic building blocksINVERTER, AND, OR, NAND, NOR, XOR, XNOR

Canonical FormsSum of Products, Products of Sums

Incompletely specified functions/don't cares

Logic Minimization

Goal: two-level logic realizations with fewest gates and fewest number of gate inputs

Obtained via Laws and Theorems of Boolean Algebra

or Boolean Cubes and the Uniting Theorem

or K-map Methods up to 6 variables

or Quine-McCluskey Algorithm

or Espresso CAD Tool