Questions Combinational Circuit

-

Upload

vigneswaran-vignesh -

Category

Documents

-

view

215 -

download

0

Transcript of Questions Combinational Circuit

-

7/25/2019 Questions Combinational Circuit

1/2

KAMBAN ENGINEERING COLLEGE, TIRUVANNAMALAIDEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

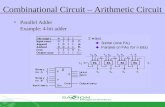

UNIT II COMBINATIONAL CIRCUITS

MODEL QUESTIONS

Two marks qus!"o#s

1. Define a combinational circuit. Draw its block diagram.2. Define propogation delay.

3. Draw the block diagram of Half adder and give its truthtable.

4. Describe the truth table of a half-subtractor and write the oolean e!pression

corresponding to the difference and borrow.

". #mplement the given function in 4 $ 1 multiple!er $ % &'m ()*1*3*"*+,

+. ist some applications of multiple!er.

. /ive the other names for multiple!er and demultiple!er.

0. ist some important demultiple!er #s.

. ention the difference between D56 and 56.

1). Draw a 1 to 2 demultiple!er circuit.

11. Draw a 2 to 1 multiple!er circuit.12. Define decoder. /ive its applications.

13. Draw a 4 6 1+ decoder constructed with two 3 6 0 decoders.

14. Define encoder.

1". 7hat is priority encoder8

1+. Design 1$ 0 demultiple!er using two 1$ 4 demultiple!er.

1. /ive the applications of demultiple!er.

10. 7hat is the function of the enable input in a multiple!er8

1. an a decoder function as a demultiple!er8

2). 9!plain the design procedure for combinational circuit.

A#swr "# D!a"$

1. Describe and e!plain the following circuits $i, %ull adder

ii, omparator (0,

2. Design and e!plain the working of a 4 to 1 ultiplier. (0,

3. #mplement a 3 to 0 line decoder. (0,

4. #mplement the logic function : & (;**, & 'm (1*2*, using 41"1; and 41"3.

". Design a D adder to add two D digits. (1+,

+. Design a 4 < bit binary to D code converter. (1),

. Design a 4 < bit binary to gray code converter. (+,

0. #mplement the following function with a multiple!er. (+,

%(a*b*c*d , & '()*1*3**4.0*.1",

. 9!plain with truth table and gate level circuit diagram for a full adder. (12,

1). #mplement the given function using multiple!er

%(!*y*=, & '()*2*+*,

11. 9!plain the concept and working of >uadruple 2 to 1 line multiple!er. (+,

12. Design a 4 bit adder?subtractor using logic gates and e!plain its operation. (0,

13. 7hat is a decoder8 7ith necessary diagrams e!plain the operation of 4 to1+ line

decoder. (1+,

14. 7hat is a decoder8 How is it different from encoder8 (4,

1". 7hat is the simplest logic circuit for a decoder that produces a 1 output when the

D input is )))).

1+. 9!plain in detail about magnitude comparator. (1+,

-

7/25/2019 Questions Combinational Circuit

2/2