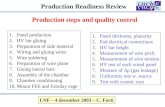

Pixel Support Tube Production Readiness Review Parts Overview

Production Readiness Review

-

Upload

hiram-hurley -

Category

Documents

-

view

40 -

download

0

description

Transcript of Production Readiness Review

C . BeigbederC . Beigbeder

Production Readiness ReviewProduction Readiness Review

On behalf of: On behalf of: Sergey Barsuk, Sergey Barsuk, Dominique Breton, Dominique Breton, Olivier Callot, Olivier Callot, Daniel Charlet, Daniel Charlet, Olivier Duarte, Olivier Duarte, Beng Ky, Beng Ky, Jacques Lefrançois, Jacques Lefrançois, Frédéric Machefert, Frédéric Machefert, Patrick Robbe,Patrick Robbe,Vanessa TocutVanessa TocutIoana Videau.Ioana Videau.

PRR PRR Mars 200Mars 20066

The FE board in the FE crate.The FE board in the FE crate.

264264 boards including boards including sparesspares

will be produced will be produced

65006500 + +15001500 Channels ChannelsInIn

14+414+4 ECAL & HCAL ECAL & HCAL cratescrates

366.7 mm366.7 mm

280mm280mm

26 x ‘9U‘ Crates26 x ‘9U‘ Crates

PRR PRR Mars 200Mars 20066

L0 calorimeter triggerL0 calorimeter trigger

Detector + PM8x4 cells/FE card

10 m cables

80 m optical link

Selection Crate

Pla

tform

on

top

of ca

lorim

ete

r

LVDS links

14 ECAL crates 4 HCAL cartes 8 Prs/SPD crates 8 cards per half crate

FE

FE

FE

FE

FE

FE

FE

FE

Ba

rrack

LVDS links

L0 Decision Unit

80 inputs

TotalEnergy

FE

FE

FE

FE

FE

FE

FE

FE

HighestElectron

HighestPhoton

ECAL HCAL

HighestHadron

SecondHighest

Highestlocal

80 linksfrom 50 cards

8 inputs 4 inputs

28 inputs

4 outputs

One Validation card per half ECAL crateOne SPD sum perhalf PreShower crate

FE

PreShower / SPD

AddressFE

FE

FE

Validation Card

LUT

highestelectron

highestphoton

28 inputs

highest

local

28 inputs

LUT

Level 0 Decision Unit

8 inputs x 8 bits

Merge back to 50

address match

highest

Highest global

highest

global

28 inputs

E TOT

8 inputsSPD

multiplicity

Add

16 inputs

SPDmultiplicity

Add

PRR PRR Mars 200Mars 20066

A crate … almost full !A crate … almost full !

PRR PRR Mars 200Mars 20066

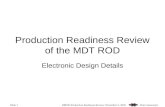

Calorimeter FE board.Calorimeter FE board.

PRR PRR Mars 200Mars 20066

Some details Some details

Delay linesDelay lines

Analog chipAnalog chip

ADCADC

Delay chipDelay chip

FE_FE_PgaPga

Trig_PGA Trig_PGA

SeqSeq_Pga_Pga

GlueGlue_Pga_Pga

SerializersSerializers + +DeserializersDeserializers

Rad-hard regulatorsRad-hard regulators

DelatchersDelatchers

Clock Clock Receiver/Receiver/driversdrivers

Analog inputAnalog inputconnectorsconnectors

AXAXconnectorconnector

LemoLemo(Probes)(Probes)

APAAPAconnectorconnector

PRR PRR Mars 200Mars 20066

Block diagram of the FE Block diagram of the FE board.board.

M axC lu s te r

Serializ er2 1 /4

E x tC h an n el 1 2 . . 4 & C o r n er

C h an n el 7 . . 0 & C o r n er

J ta g

P o w e rSuppl i e s

L E ds

7 2

Serializ er2 1 /4

3 2C h an n el : 7 - 1 5 - 2 3 - 3 11 6

E x tC h an n el 3 2 1 0

3 2D es erializ er2 1 /4 1 6

Sha p e r A D C1 2 bit s /4 0 M h z

Serializ er2 1 /4

T im in g Ad ju s tm en tS etu p

D ela y ch ip

Ad a

ptat

ion

Del

ay li

nes

An a lo g I n p u tc o n n ec to r s

L 0 D a ta

T rig ger D a ta

1 2 8

S id en eig h bo u rsLVTTL

7 2

F E _ Pg a

I2 C

S eq p g a

N eig h b o u r sto p & b o tto m

T o C ro c

T o V a lida tio n2 1

V ersio n 1 /0 3 /2 0 06

3 2 C ha nne lsfrom P m s

E ven tF o rm ater

2 0

3 2 Tri g _ Pg a

L 0 & trig g e r da ta pro ce s s

7 2

I2 C

Fifo S py

I2 C

C om m an ds

2 1

C om m an ds

S e qu e n ce r

R e g u la to rs /D e la tch e r

G lu eL e ds

S ilico n Ex plo re r

Pro be

P ro b e

P ro b e

C lo ck dis t ibu t io ne le m e n ts

E C S

Sp e c s

Fifo S py

I2 C

I2 C

8C o rn er

Pro be O u tpu tM U X

D ela y ch ip

Serializ er2 1 /4 T o P S2 1

J ta g P rogra m m e r

T o P SSerializ er2 1 /4

P ro b e

D es erialC lo ck

D es erialC lo ck

PRR PRR Mars 200Mars 20066

Analog part.Analog part.

10 meters ( same for all )10 meters ( same for all )

On-detector clippingOn-detector clipping

Delay lineDelay line

BufferBuffer

Cable effect cancellationCable effect cancellation

Pedestal adjustment to ~128binsPedestal adjustment to ~128bins

P m

B uffe r In te gra tor

Vs s

Vd d

A na log C hip

B IC M O S 0.8 um Inte gra te d c irc uit 4 c ha nne ls pe r c h ip

+

-

5 n s

2 5

6 5

2 7

4 5

1 2 M

3 3 3 7

5 1 .1

3 3

3 3 0

3 .3 k1 .5 K

2 5 n s

11 0

2 .2 n F

4 7 0 p F

2 7

2 2 n F

1 .0 7 k

A D C1 2 b its 4 0 M h z

4 p F

2 .7 k

4 .7 k

1 n F

1 n F

4 .7 k

4 .7 n F

+ 3 V

1 0 k

2 0 k

The set of resistors can be easily The set of resistors can be easily removed to match the variation on removed to match the variation on the input impedance of the ADC the input impedance of the ADC (+- 64 ADC count )(+- 64 ADC count )

PRR PRR Mars 200Mars 20066

Delay ChipDelay Chip

0,00E+00

5,00E-09

1,00E-08

1,50E-08

2,00E-08

2,50E-08

3,00E-08

0 5 10 15 20 25 30

Série1

Linéaire (Série1)

• Technology : AMS 0.8µm pure CMOS process in a 28 pin SOZ package• Production tested and recorded in a database: yield is about 95%. • The power consumption is about [email protected].• The linearity is better than +/- 100ps per step. • The clock jitter is less than 15ps RMS for all channels.

Needs to receive a reset after programming of a large step on the output delays.Needs to receive a reset after programming of a large step on the output delays.

PRR PRR Mars 200Mars 20066

Fe PGAFe PGA

A D C d a ta 3

A D C d a ta 2

A D C d a ta 1

A D C d a ta 0

A ddC o u n te r/

L ate nc yo ffs e t /3 v

R d

A dd

L0 La te nc y R a mC irc u lar b u ffe r

F e_ P g a

T rig g er d a ta (1 6 b its @ 8 0 M hz )

L 0

W r

D ata

A dd

8 0

4 0 M hzC lock

I2 Cinte rfa c e C han 0 _ re g /3 v

C han 1 _ re g /3 v

V ersion 1 /03 /20 0 6

D ata

R ea d ou tS eq u en cer

C han 2 _ re g /3 v

C han 3 _ re g /3 v

T riggerC a lib ra t ion

1 2 1 2

8

T riggerC a lib ra t ion

1 2 1 2

8

T riggerC a lib ra t ion

1 2 1 2

8

T riggerC a lib ra t ion

1 2 1 2

8

2 0L 0 D a ta

D e ra ndo m is e r1 6 de p th 3 V F ifo

T es tR AM

5 b lo c k s

1 21 2

1 21 2

T est seq u en ce

T es tC h an 3

S tatu s

In terru p t

N T A

ad d

N eig hb ou rs d a ta (up to 3 2 b its@ 4 0 M hz )

L 0 F eR eset

W r Rd

D a ta D a ta

W r

D a ta D a ta

W r

D a ta D a ta

R d cm d

W r

D a ta D a ta

T es tC h an 2T es tC h an 1T es tC h an 0

T es tC h an 3

T es tC h an 2

T es tC h an 1

T es tC h an 0

I2 C

P seud o P Msig na ls

E n ab le

A ddC o u n te rtestm od e

testm od e

1 6 * 3

Spy F i fo

F ifo

Rd

Rd

Rd

Ef

Ef

Ef

Ef

E m p ty F ifo

C k L 0

C loc k

F ifo

F ifo

F ifo

S u b tra cto r

S u b tra cto r

S u b tra cto r

S u b tra cto r

P L L

3 modes for3 modes forRAM advanceRAM advance

Needs to be checkedNeeds to be checkedpermanently. Added in permanently. Added in the control wordthe control word

Duty cycle of 50%Duty cycle of 50%( ( FDRFDR ) )

PRR PRR Mars 200Mars 20066

Triple voting FIFO Triple voting FIFO (derandomizer)(derandomizer)

R a m

W r A ddress

C lock

5 A d d 0

3 v c ounte rR d A ddress

5

C lock

R d f ifoS yn ch reset

C lock3 v c ounte r

W r fifo E n a b l e

C lock

S yn ch reset

F ro n d E n d R eset

E n a b l e

A d d 1

A d d 3 1

C ounte rW r fifo E n a b l e

C lock

S yn ch reset

F ro n d E n d R eset

C ounte rE n a b l e S yn ch reset

C ounte rE n a b l e S yn ch reset

3 V o tin g o u tp u t

E m p ty fifo=

PRR PRR Mars 200Mars 20066

G l o b a l C l o c k

V ersio n 0 1 /0 3 /2 0 0 6

A D C d a t a

L0 D a ta

C k

D Q

C k

D Q

T r e sh

M u x

C k

D Q

+2 5 6

1 2

1 3firststa g e

a d d _ ech

+

M u xM i n

a d d er

1

0

1 2

C lk in v se l3 vreg

O ldsubm o de3 vreg

3 vreg

1

0

3

3 vreg

1 2 1 2

su b ra c to rsa t_ ech

S u b

S a t

C k

D Q

R

1 2

trig g er_ Ca lib

A

B

Sub_ z e r o

C a lib_ C t e3 vreg

A * B R o u n d& S a t

2 0 8

8 Trig g er D a ta

2 0

F E _ P g aL0 a n d tr ig g e r d a ta p ro ce s s in g p a r t : M o d u le S u b tra ct5 C lo ck cy cle s In p u t to O u tp u t

C k

D Q

R

-2 5 6

3 vreg

1

0

T e st P a t t e r n

Test p a ttern d a ta

C k

D Q

R

C k

D Q

R

C k

D Q

R

1 2

C k

D Q

R

C k

D Q

G a in* 4

ADC data processingADC data processing

Clock adjustment study:Clock adjustment study:next talknext talk

2 methods for pedestal subtraction 2 methods for pedestal subtraction

Possibility to decrease the HVPossibility to decrease the HV

PRR PRR Mars 200Mars 20066

Principles of ECAL/HCAL L0 TriggerPrinciples of ECAL/HCAL L0 Trigger

3 7 11 15 19 23 27 31

2 6 10 14 18 22 26 30

1 5 9 13 17 21 25 29

0 4 8 12 16 20 24 28

3 7 11 15 19 23 27 31

2 6 10 14 18 22 26 30

1 5 9 13 17 21 25 29

0 4 8 12 16 20 24 28

3 7 11 15 19 23 27 31

2 6 10 14 18 22 26 30

1 5 9 13 17 21 25 29

0 4 8 12 16 20 24 28

3 7 11 15 19 23 27 31

2 6 10 14 18 22 26 30

1 5 9 13 17 21 25 29

0 4 8 12 16 20 24 28

FeP

GA

0

FeP

GA

1

FeP

GA

2

FeP

GA

3

FeP

GA

4

FeP

GA

5

FeP

GA

6

FeP

GA

7Crates

Front-end boards

y

x

z

Calorimeter cells

Cable links between crates (16 bits serialized 280 MHz) – 2 Cables per card

Backplane connections (40 MHz)

Compute from the 12 bit ADC energy value a calibrated 8 bit ET value (done in FePGA).

Compute the 32 2x2 candidates (sums), using 45 inputs:

Select the highest of the 32 sums and identify its positions,

Sum 8 disconnected candidates to obtain the sum of all cells on this card.

PRR PRR Mars 200Mars 20066

TrigPGA : block diagramTrigPGA : block diagram

G l o bal Vi e w , Tr i g _ P G AV ersio n 2 2 /0 3 /2 0 0 6

T rig _ P G A

T rig g er D a ta

1 2 8 @ 8 0 M h z

(3 2 C h a n els F E B )

8 S id e N eig h b o u rs

4 U p S id e N eig h n o u rs

1 In C o n er

(F R O M F e_ P G A )

Sp yF IF O

h ig h e st su m

a d d re ss h ig h e st su m

to ta l e n e rg y

8 85

I2 C

T est S eq u en ce

(F R O M S eq _ P G A )32

su

m o

utp

ut

45 s

um

in

pu

tPgmDelay Ram

PgmDelay Ram

PgmDelay Ram

PgmDelay Ram

BX IDCpt

B X ID cp t reset

( to V a lid a tio n )

R eg isters

Pg m d e la y

D a tac om p uting

E c e lla d d e r

o u t_ c o rn e r

o u t_ t r ig _ b c id

Ro u te d Clk40o u t_ c lk 4 se ria l i se r

The phase of the clockThe phase of the clockof the serializer comes of the serializer comes from the trigpga (from the trigpga (FDRFDR))

I/O used 306 out of 317 : 266 inputs 39 outputs And 1 bidirectionnal

PRR PRR Mars 200Mars 20066

Internal view of data computingInternal view of data computing

A d d r_ H ig est_ S u m

D a tac om p uting

h ig h es t s u m

a d d r es s h ig h es t s u m

to ta l en er g y

4 A d d er

F i rs t S tag e

8

C L K

8

2 A d d er

S eco n d S tag e

88

1 A d d er

T h ird S tag e

8

C L K

8

1 6 C o m p

F irs t S tag e

C L K

8 C o m p are+ M u x

S eco n d S tag e

4 C o m p are+ M u x

T h ird S tag e

C L K

2 C o m p are+ M u x

F o u rth S tag e

1 C o m p are+ M u x

F i fth S tag e

C L K

8

5

8

5

8

5

8

5

8

5

H ig est_ S u m

85

85

8

5

(F R O M E cell_ Ad d er)

4 fl ip flo p

F is t S tag e

C L K

2 fl ip flo p

S eco n d S tag e

T o ta l_E n erg y

1 fl ip flo p

T h ird S tag eT wo F is t C lo ck C ycle s

Se co n d C lo ck C ycle

T h ird C lo ck C ycle

4 fl ip flo p

F is t S tag e

S u m 0

S u m 1

8

CL K

8

CL K

S u m 0

S u m 1

8

CL K

8

CL K

PRR PRR Mars 200Mars 20066

Front-end PGAs.Front-end PGAs.

R ea d ou tS eq u en cer

C irc ula rLa te nc yR a m

L0 d a taD e ra nd om ise rF ifo

p a ra m e te r_ re g

D a tap rocessin g

I2 Cin terfa ce

p a ra m e te r_ re g

L 0 d a ta

F e _ Pg a

2

F r on t E n d d a ta

T r ig g e r d a ta

R d

R ea d ou tseq u en cer &p a ri ty en cod er

D a tap roc e ss ing

E vt d a ta

T o C r oc

8 * 2 0 bits

C ha n Bd ecod er

8Ev t I dco u n te r

B C idco u n te r

re s e t Ev t

re s e t B C

D e ra nd om ise rF ifo

R d

T e s t se q ue nc e

I2 C

L 0 F e R e se t

L 0

T est pa ttern

L 0

T e s t se q ue nc e

L 0 F eR eset

I2 C

V ersion 1 /03 /2006

L 0Sequencer

L 0

P SSP D bits La ten cyR a m

C pt A dd

Spy F i fo

Spy F i fo

La ten cyR a m

I2 Cin terfa ce

2 1

w r r d

La ten cyR a m

E m p ty F i fo

E m p ty F ifo

B C Id _ T r ig g e r_ R e se t

C ha nne l B

4 8

4

E m p ty F ifo

Se q_ Pg a

C loc kP L L

C loc k for se r ia lize r

E C SD ir/In v

C lo c k

The serializer clockThe serializer clockcomes from SEQcomes from SEQ

PRR PRR Mars 200Mars 20066

Processing and formattingProcessing and formatting

078151617181920

BX - Id L0 - Id

Pari

ty

PRS/

SPD

Cal

ib.

Tes

t

Seq .

PRS/

SPD

Channel 8

Channel 4

Channel 0

Header

Separator

Separator

Trailer (Vertical Parity)

Channel 31

[É ]

011121920

Par

ity

Data ECAL/HCALTrigger ECAL/HCAL

Parity

Line i

Channel

4x ( ( i - 1 ) modulo 8 ) + int ( ( i Ğ 1 ) / 8 )

Line 1É

Derandomizer FIFO : 1bit ‘ And ‘ of the 8 Fe + 1 bit for the Derandomizer FIFO : 1bit ‘ And ‘ of the 8 Fe + 1 bit for the Sequencer. Sequencer.

2 Bits of PS/SPD +2 Bits of PS/SPD +Calibration pulse and its maskCalibration pulse and its mask

2 1

E vt & B c cou n terL 0 an d P s S p d d ata D e r a n d o m i s e r

FIFO

In 0In 1

In 9

M U X

w rfifo W r

rd fi fo

C k

D Q

C L

C k

D QFe P g a 0 20

P a r it y

C l o c k

EN

In p u t e n

C k

D Q

C L

C le a r o u tp u t re g

2 1

C k

D QFe P g a 7 20

P a r it y

C l o c k

EN

In p u t e n

T o C ro c

C l o c k

C l o c k

H o rizo n ta l P a rity

S e l m u x

PRR PRR Mars 200Mars 20066

Glue PGAGlue PGA

C tr l l ine

8 b D ata l ine

S LA V E _ R E C E IV E R

SP E C S C l o c k r e c e i ve rr e g i o n

I2 C _ 1

J TAG

I 2 C _ O UTPUT

SP E C S_ B U S

J TA G _ O UTPUT

S LA V E _R E G IS T E R

M U X J T A GE X P LO R E R

I2 C _ 2

S LA V E _ D A T A _ C T R L

SP E C S w o r d E m i t te r

SL AVE E m i tte r C TR L

SP E C S C l o c k e m i t te rr e g i o n

F IF O

JTA

G E

XP

LO

RE

R

JTA

G F

PG

A

L ED SC O NTR O L

R C _ L E D

L E D S

SP E C S_ B U S

Only calorimeter- Only calorimeter- specific blockspecific block

PRR PRR Mars 200Mars 20066

Clock distribution Clock distribution

FDRFDR

FDRFDR

Next talkNext talk

FDRFDR

Next talkNext talk

New design of the clock treeNew design of the clock tree

D es erializ er2 1 /4

C o m m o nB a ck p la n e

N eig h b o u r sto p & b o tto m

An al ogIn pu tB l ock

D e lC h i p

D ela yC h ip

S N6 5L V D S 1 0 4

Serializ er2 1 /4

8 F e pg a _ B lo c k s

F e pg a_ bl o c k

P m t e st P ulse

8 L V D S dif C lo ck s1 6

S e ria lC k 0

S e ria lC k 1

A d jCk 1

G lo b a lC k

T rig _ P g a

9 0L V 0 4 8

1 L V D S dif C lo ck

C k

D Q2 1

C lo ck f rom seria l izer

G lob a l clo ck

E cs R d R eg ister

S eria l D a ta

A d ju sted C lock

C loc k f rom C roc

C o m m an d s

C k

D Q

C k

D Q

E cs

2 1 + C lo ck

2 1

L v 0 1 0

P L L

F e p g a

P L L

P L L

S eq p g a

P L L

G lu eI 2 C

V ersio n 1 /0 3 /2 0 0 6

1 6

S N6 5L V D S 1 0 4

S N6 5L V D S 1 0 4

S N6 5L V D S 1 0 4

PRR PRR Mars 200Mars 20066

+ 3 .3 V F u se

c te

F au lt

In

M ax 869

+ 3 .3 V _ F ep g a 3 to04 9 1 3

R e g ula tor

O n

Vc ore _ F e p g a 3 to0 (1 .5 v )

F au lt

In

M ax 869

+ 3 .3 V _ F ep g a 7 to44 9 1 3

R e g ula tor

O n

Vc ore _ F e p g a 7 to4 a nd T r ig g e r_ p g a (1 .5 V)

F au lt

In

M ax 869

+ 3 .3 V _ G lu e 8 S eq

O n

4 9 1 3R e g ula tor

Vc ore _ A p a ( 2 .5 v )

-5 V F u se7 9 1 3

R e g ula tor

F u se4 9 1 3

R e g ula tor

+ 5 V

In terru p t

In terru p t

C om m on sign a l to specs in terru p t

V a d c+ 3 .3 V _ g lu e com p on en ts ( seria l i zer , d ela y chip .. .)

A na log + 3 VA d 8 042 V 1 sh aper

A d 8 042 V 2 sh aper

A na log -4 V

C lerm on t

Power distributionPower distributionBoard Consumption : Board Consumption : +5 V = 4A+5 V = 4A+3.3V = 2 A+3.3V = 2 A-5V = 1 A-5V = 1 A

Fault is sent individually via a dedicated line to the CROC ( Fault is sent individually via a dedicated line to the CROC ( FDRFDR ) )

PRR PRR Mars 200Mars 20066

Programming-debugging : JTAG Programming-debugging : JTAG ChainChain

2 J ta g ch a in s : A x celera to r a n d P ro A sic

D ed ic a ted J tag p in s D ed ic a ted J tag p in sT C K T D I T D OT M S T C K T D I T D OT M S

G lu e p g aA P A 1 5 0

S eq p g a

A P A 3 0 0

IS P ( P roA sic p ro gram m in g C on n ecto r )

S ilicon E xp lorerjtag con n ecto r

F e p g aA x 2 5 0

D ed icat ed J t agp in s

T ckT m s

T d iT d o

T C K

T M S

T D I

T D O

T D I[n ]

TD I[n :0 ]

T D O [n ]

TD O [n :0 ]

T D I

T D O

Tr ig p g aA x 5 0 0

T ckT m sT d i

T d o

T C K

T M S

T D I

T D O

T D I

T D O

T C K

T M S

Lem o

D ed icat ed J t agp in s

P rob e s

' h om e-m ade 'P ro bes

P rob e s

EC S

TD O [n -1 :0 ]

EC S

T D I[0 ]

T D O [0 ]

Pro

gram

mab

leO

utpu

t

P r o g r a m m a b leO u tp u t

V ersion 1 /0 3 /2 006

PRR PRR Mars 200Mars 20066

Test Control Test Control

3 Modes :3 Modes :

• L0 advanceL0 advance• Clock advanceClock advance• Calibration advanceCalibration advance

Calibration Calibration

L0dataL0data• Spy ramSpy ram• CrocCroc

Trigger dataTrigger data• Spy ramSpy ram• NeighboursNeighbours• CablesCables

Calibration channelBCalibration channelB

L0L0

PRR PRR Mars 200Mars 20066

Final layout Final layout

• Thickness : 2.4 mm.Thickness : 2.4 mm.• 12 layers12 layers• Minimum isolation : 0.11mmMinimum isolation : 0.11mm• Via : width = 0.35 mmVia : width = 0.35 mm• Plating : Ni-Au for BGAsPlating : Ni-Au for BGAs

• 3062 components3062 components• 3581 nets3581 nets• 15800 pins 15800 pins • ~10000 connections~10000 connections• 6072 vias6072 vias• via/connection 0.64via/connection 0.64•Manhathan < + .1 % Man theoManhathan < + .1 % Man theo

PRR PRR Mars 200Mars 20066

Some layers … Some layers …

PRR PRR Mars 200Mars 20066

ProductionProduction

After tendering, three companies have been selected and their offers thoroughly studied.

We visited all of them for a whole day each. One of them has been chosen based on all the elements we had in

hand: Laudren in Lorient. We’re really satisfied with this company up to now. They have produced all the boards until now, so they have an

almost perfect knowledge of the product. The PCB is produced in France with a Ni/Au coating, compatible

with press-fit connectors and BGAs. All the components have already been delivered at the

manufacturer. The production flow and the in-factory tests will be presented by

Dominique.

PRR PRR Mars 200Mars 20066

Milestones before productionMilestones before production In the wake of Final Design Review: answer to the referees. 2 Prototypes (mid September)

Standalone Test. Two cards for a combined test (neighbours) and test with

Validation Card (cable and backplane) Test at CPO.

=> Modifications. 2 new Prototypes (December 5th): same as for the 2 former

prototypes 16 Boards (pre-series)

Test at CPO to validate the acquisition chain and launch the production of the FEPGA

16 boards in a Crate ( Wow ! ) Test with Validation Board (half a crate) Aging of 8 good boards to validate the aging process.

PRR PRR Mars 200Mars 20066

Production planning Production planning

Week 13 : - beginning of production preparation at Laudren Week 13 : - beginning of production preparation at Laudren - Launching of the programation of the Actel AX (FePGA and Launching of the programation of the Actel AX (FePGA and TrigPGA): TrigPGA): 4chips/hour, 12hours/day4chips/hour, 12hours/day

-> Test of one chip of each type ASAP. -> Test of one chip of each type ASAP.

Week 16 : beginning of the cabling of the 80 first PCBs.Week 16 : beginning of the cabling of the 80 first PCBs.Launching of the production of the remaining PCBs by batch of Launching of the production of the remaining PCBs by batch of 80.80.

Week 19 : reception of the first 16 boards.Week 19 : reception of the first 16 boards.

Week 23 : reception of the left-over of the first batch of 80 boards.Week 23 : reception of the left-over of the first batch of 80 boards.

Week 24 : beginning of delivery of the second batch with a frequency of Week 24 : beginning of delivery of the second batch with a frequency of 32 boards per week until end of week 28.32 boards per week until end of week 28.