Logic Design Sequential Logic (Chapter 3)bhagiweb/cs2461/lectures/logic4.pdf · Logic Design...

Transcript of Logic Design Sequential Logic (Chapter 3)bhagiweb/cs2461/lectures/logic4.pdf · Logic Design...

1

Based on slides © McGraw-HillAdditional material © 2004/2005/2006 Lewis/Martin

Additional material © 2008 Roth Additional material © 2010 TaylorAdditional material © 2013 Farmer

Additional material © 2018 Narahari

Logic Design Sequential Logic(Chapter 3)

So Far: Combinational Logic

Combinational Logic:• Always gives the same output for a given set of inputs• Aka “state-less” (i.e., no “state” or “memory”)

Sequential Logic:• Its output depends on its inputs & its last output!• Forms the basis for “state” or “memory” for a computer

Combinational vs. SequentialCombinational Circuit

• always gives the same output for a given set of inputs ex: adder always generates sum and carry,

regardless of previous inputs

Sequential Circuit• stores information• output depends on stored information (state) plus input

so a given input might produce different outputs,depending on the stored information

• example: elevator Current floor increases when you go up output depends on previous state and ‘inputs’ (request for current floor)

• useful for building “memory” elements and “state machines”

Example: A Vending Machine•Accept user input (coins), when total is at least 50 cents dispense output (soda)

•Input valid coins:• Q (25cents) D (10) or N (5)

• What should it keep track of ? •When it reaches 50 or more:

• Generate output

•States of the machine ?• At each instant in time, summarize the state of the machine

• Analogy: if you set a breakpoint in your program and print out the values of the variables ?

2

Describing behavior of Sequential Circuit: Finite State Machine Diagram

Machine transitions through sequence of states• Each state represents “current total”

Transition from one state to another depends on the value of the input

• If current total is 10 and input is 25 then next total is 35

Represent as a directed graph• Nodes represent the states• Edges are labelled with the input(s)

Design a Counter: counts from 0 to 7

Finite State Machine Representation of Counter

000

001

010

011

100

101

110

111

Reset

Bubbles represent all possible “states” for theMachine (the decimal equivalentof the label in each state is thevalue of the counter)

Arrows show movement fromone state to the next

Transitions occur at eachclock cycle

Counter from 0 to 3 (2-bit counter)

00

01

10

11

Reset Circuit has a “ON” switch (input)If ON=0 then machine goes to 00

ON=1ON=1

ON=1

ON=1

3

Circuit Design for a 2-bit Counter• count from 0 to 3

• 2 bit encoding A,B of states: 00, 01,10,11• Counts 00 01 10 11

• How can we apply our current knowledge of circuit design?• Recall process:

• Input variables, Output variables• Truth table• Boolean function from truth table .. Leads to circuit

•Input variables: ON and Current State, i.e., values of A,B•Output variables: Next State – i.e., new values of A,B•Now imagine we have a device that stores the state variables (bits) A,B functions:

• Circuit: Looks up current value of A,B and value of input ON, and Computes A*B* the next values of A,B to be stored into device

Circuit Design for a 2-bit Counter• Derive Truth table

• Using ON, A, B as inputs and A*, B* as outputs•functions:

• A,B current state• A*, B* next state• A* = ON.( (A’B) + (A B’)) = ON.( A XOR B)• B* = ON.( (A’B’) + (AB’)) = ON. B’

ON A B A* B*1 0 0 0 11 0 1 1 01 1 0 1 11 1 1 0 00 X X 0 0

Circuit Design for a 2-bit Counter• count from 0 to 3

• 2 bit encoding A,B of states: 00, 01,10,11• Counts 00 01 10 11

• functions:• A,B current state• A*, B* next state• A* = (A’B) + (A B’) = A XOR B• B* = (A’B’) + (AB’) = B’

A B A* B*

0 0 0 1

0 1 1 0

1 0 1 1

1 1 0 0

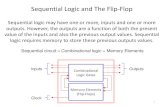

Finite State Machine – circuit designtype of sequential circuit

• Combines combinational logic with storage• “Remembers” state, and changes output (and state)

based on inputs and current state

State Machine

CombinationalLogic Circuit

StorageElements

Inputs Outputs

4

Finite State Machines•The behavior of sequential circuits can be expressed using characteristic tables or finite state machines (FSMs).

•Characteristic tables ~ truth tables, but include current and next state

• FSMs consist of a set of nodes that hold the states of the machine and a set of arcs that connect the states.

• Directed graph to represent a FSM

Moore and Mealy machines are two types of FSMs that are equivalent.• They differ only in how they express the outputs of the machine.• Moore machines place outputs on each node/state

Associate an output with each state

• Mealy machines present their outputs on the transitions.

Sequential Logic•Where do we start:•Build a device, using combinational logic devices, to store a value

• RS Latch (also called SR Latch)• concept of memory

•Build it using the devices we have thus far• How ? Use “feedback” circuit

•What is the methodology behind design of sequential logic circuits

• Finite State Machines• Example of Vending machine

•Combine sequential and combinational logic devices to “assemble” a simple processor!

Feedback CircuitsWhat happens if we feed the output of a combinational logic circuit to an input in the circuit ?This is the key to circuits that can store values!

Stable circuitOutput point of circuit retains value indefinitely

Unstable circuitState that remains constant only for a duration of a few gate delays

Feedback circuits• download Sequential Circuits: sequential1.cdl

• Open in Cedar Logic •Page 1 of Sequential Circuits: Example 1

• How do the two circuits on this page behave ?• Is the output value ‘stable’ or does it keep jumping between 0 and

1 ?

5

Feedback CircuitsTo retain their state values, sequential circuits rely on feedback.

Feedback in digital circuits occurs when an output is looped back to the input.A simple example of this concept is shown below.

If Q is 0 it will always be 0, if it is 1, it will always be 1. Why?

Latches and Flip-FlopsLatch: basic circuit for storage

• Operate on changes in Level (i.e., 1 or 0)Flip-flop:

• Sequential circuits take input from output of storage• Latches that work on change of level can lead to unstable sequential

circuitsAs level changes the outputs change --- inputs change!

• Flip-Flop circuits designed to operate properly when they are part of a sequential circuit

Most Basic Sequential Logic Circuit: R-S LatchMost fundamental unit for static memory

• Has the ability to “store” its last outputR-S Latch – Cross-Coupled NAND gates

• Output of each NAND gate serves as input to the other• Two inputs: S (SET) & R (RESET)• Two outputs: Q and NOT(Q) Recall: NOT(Q)= ~Q = Q’ = Q• Called a “Latch” because it can “Latch” onto data coming in

S

R

Q~Q

R-S Latch• The R-S latch is a bi-stable circuit which means that it can happily

exist in either of two stable states. Just like a see-saw.• You can push the latch from one state to another by setting or

resetting it with the S-R signals• The logic levels are maintained because of the feedback paths from

outputs to inputs.

6

Most Basic Sequential Logic Circuit: R-S LatchMost fundamental unit for static memory

• Has the ability to “store” its last outputR-S Latch – Cross-Coupled NAND gates

• Output of each NAND gate serves as input to the other• Two inputs: S (SET) & R (RESET)• Two outputs: Q and NOT(Q) Recall: NOT(Q)= ~Q = Q’ = Q• Called a “Latch” because it can “Latch” onto data coming in

S

R

Q~Q

Another common way of drawing the same circuit

RS Latch• Page 2 of Sequential Circuits: Example 1

• Figure on top of page (with one circuit)•First, set S=0, R=1

• What is the output Q ? (can also check complement Q’ )•Next, set S=1, R=1

• What is the output ?•Next, set R=0, S=1

• What is the output ?•Next, set R=1, S=1

• What is the output ?

Our first Sequential Logic Circuit: R-S LatchFirst, recall truth table for a NAND gate:

R-S Latch Operation:• Best place to start is S=1, R=0

3-23

S=1

R=0

Q~Q

A B C0 0 10 1 1

1 0 1

1 1 0

Next, look at top NAND gateIts inputs are: 1 and 1

Blue 1, comes from lower NANDProduces a 0 at its output

Therefore, when S=1, R=0The output of latch is: Q=0, ~Q=1

0X1

10

Truth Table for R-S Latch:

Called the “RESET” action, as Q is set to 0Also, notice: Q and ~Q opposite

….R-S Latch: RESET actiontruth table for a NAND gate:

R-S Latch Operation:

S=1

R=0

Q~Q

A B C0 0 10 1 1

1 0 1

1 1 0

ACTION S R Q ~Q0 00 1

RESET 1 0 0 1

1 1

01

RESET output to 0set S=1 R=0

7

…R-S Latch: HOLD actionTruth table for a NAND gate:

R-S Latch Operation:

3-25

A B C0 0 10 1 1

1 0 1

1 1 0

Truth Table for R-S Latch:

HOLD’s last value on its outputs!OUTPUT depends on input and last output

ACTION S R Q ~Q0 0

SET 0 1 1 0

RESET 1 0 0 1

HOLD 1 1 1 0

HOLD 1 1 0 1

0

1

S=1

R=1

Q~Q

HOLD previous valueof QSet S=R =1

…R-S Latch: SET actionTruth table for a NAND gate:

R-S Latch Operation:• Next input case is called the “SET”, when inputs are: S=0, R=1

S=0

R=1

Q~Q

A B C0 0 10 1 1

1 0 1

1 1 0

1st look at upper NAND gateIts inputs are: 0 and X (anything) Produces a 1 at its output

Lower NAND gate Inputs are: 1 and 1Produces a 0 at its output

0X

1

0

SET output to Q=1set S=0, R=1

R-S LatchTruth table for a NAND gate:

R-S Latch Operation:

3-27

S=0

R=1

Q~Q

A B C0 0 10 1 1

1 0 1

1 1 0

Truth Table for R-S Latch:

SETs LATCH to have a “1” at the output

ACTION S R Q ~Q0 0

SET 0 1 1 0

RESET 1 0 0 1

1 1

1

0

Upper NAND gateHas S=1 & former value of ~Q=0Produces a 1 at its output

(same ~Q as when it started)Lower NAND gate Inputs are: 1 and 1Produces a 0 at its output (same Q)

R-S Latch..HOLD

Truth table for a NAND gate:

R-S Latch Operation:• Last valid input case is the “HOLD” S=1, R=1

If we have just “SET” Latch, we will have Q=1, ~Q=0, already on outputs

S=1

R=1

Q~Q

A B C0 0 10 1 1

1 0 1

1 1 0

10

1

0

Next, set S=1, R=1It holds the value of Q=1

8

R-S Latch: holding/storing the previous valueTruth table for a NAND gate:

R-S Latch Operation:

3-29

S=1

R=1

Q~Q

A B C0 0 10 1 1

1 0 1

1 1 0

Truth Table for R-S Latch:

HOLD’s value we “SET” last

ACTION S R Q ~Q0 0

SET 0 1 1 0

RESET 1 0 0 1

HOLD 1 1 1 0

1

0

R-S Latch: Illegal setting

What happens with S=0 and R=0?• Short answer: confusion• Real circuits depend on both Q and ~Q• Strange things may happen if both are 1

D-Latches shows a way to preventthe RS Latch from ever getting S=R=0 as its input

S

R

Q1

0

0

1~Q

ACTION S R Q ~QILLEGAL 0 0 1 1

SET 0 1 1 0

RESET 1 0 0 1

HOLD 1 1 1 0

HOLD 1 1 0 1

Using multiple RS latches

•Figure on Page 3: Multiple latches. • What is this circuit doing ?• Stores 3 bit number!

• 1 bit in each latch

Storage - Cross-Coupled NANDs (R-S Latch)How does this device “store” data?

• Each latch can store 1-bit of information, 3 SR Latches, holds 3-bits• Let’s assume we wish to store the number 510 (1012 in binary):

SR

Q

SR

Q

SR

Q

0

1

1

0

0

1

1

0

1

SET

RESET

SET

510

“Setting” the data wewish to store

SR

Q

SR

Q

SR

Q

1

1

1

1

1

1

1

0

1

HOLD

HOLD

HOLD

510

“Holding” the data weset in the last phase

9

Gated D-Latch: Preventing “Illegal State” of RS LatchAdd logic to an R-S latch• Create a more convenient interface, prevent S=0 && R=0D-Latch stores 1 bit

Two inputs: D (data) and WE (write enable)• When WE = 1, latch is set to value of DS = NOT(D), R = D

0

1

10WED

Q

11

S

R

D=1 && WE=1So Q=1

What to do about the illegal inputs in RS latch…can we make the latch simpler?

• Page 4 •Place an input at D, set WE=1

• What happens to output

• set WE=0, set input at D• What happens to output

• We have a D latch – simplest way to store a bit• If Write Enable =1 then input is stored• IF write enable =0, previous value remains in ‘storage’

•Value of Q = the last value of D when WE=1• Latch Stores the last written value of variable D !

Gated D-Latch: Preventing “Illegal State” of RS LatchAdd logic to an R-S latch• Create a more convenient interface, prevent S=0 && R=0

Two inputs: D (data) and WE (write enable)• When WE = 1, latch is set to value of DS = NOT(D), R = D

• When WE = 0, latch continues to hold previous valueS = R = 1 (hold condition for SR latch)

• Extra logic does not allow S=0, R=0 case to occur

1

1

01WED

Q

00

S

R

0 was held fromlast state

Q no longer followsD, when WE=0

D-Latch Timing Diagram• The diagram below is called a “Timing” DiagramOur D-Latch is previous-state dependent

– We can think of this as a time dependency– Moving to the right on diagram, represents forward moving time

The inputs & outputs to our D-Latch are on left– Inputs/Outputs can be either “HIGH” (logic 1) or “LOW” (logic )

Think of this as a time-dependent truth table

WE

D

Logic level =1Logic level =0

time

Q

10

D-Latch Timing Diagram• When the WE signal is high the latch is said to be open and the

output signal, Q, follows the input signal, D.As in any combinational circuit there will be a small delay between

the time that the input changes and the time that the output follows suit.

WE

D

Q

open open

time

When latch is OPEN (WE=1): Notice, Q follows D

D-Latch Timing Diagram• When the WE signal is low the latch is closed and the output signal, Q

retains its value.

WE

D

Q

open open

time

When latch is CLOSED (WE=0): Notice, Q doesn’t follow D(Instead, Q has previous value)

closed

D-Latch Timing Diagram• Setup / Hold TimesThe input signal should (D) be stable a certain amount of time

before the WE signal is set to CLOSED (WE=0)– This is referred to as the SETUP time

In addition, the input signal (D) must be stable for a time after the WE is set to CLOSED (WE=0)

– This is referred to as HOLD time Why? Time must be given for inputs to propagate through NAND

gates! Gates are not instantaneous!

WE

D

Q

open openclosedLogic level =1Logic level =0

time

Next… Storage Devices•Ok…we now have a device ( D-Latch) that can store a bit

•Use this to build ‘real’ storage devices….•Temporary storage in a computer ?

• Where are variables stored before being sent to the arithmetic unit for operations on them?

•Register• Can we build an n-bit register using latches?

•What about “main” memory•Disk

• Later…

11

Page 5 of sequential1.cdl file• Use 4 D latches

•Set input (from keypad) and set WE=1• What gets stored

•Set WE=0, try entering inputs

•4-bit register

Multi–Bit D-Latch• A collection of D-latches, controlled by a common WE• When WE=1, n-bit value D is written to the outputs

D2Q2

D1Q1

D0Q0

D QD3 3

WE

WE

RegisterA register stores a multi-bit value.

• We use a collection of D-latches, all controlled by a common WE.• When WE=1, n-bit value D is written to register.

Recall: A Basic Model of a Computer

0 -20

1 10

2 -7

3 8

4 3

5 9

0 ADD 0, -20, $01 ADD 0, 10, $12 SUB $0, $1, $03 MPY $0, $4, $5

4 ADD $0, $5, $05 DIV $0, 5, $0

Memory CPU Instructions

2 PC

Essential Part of Computer!

Address Data

Basic Components: Address: Looks up dataNote: both are in binary

12

MemoryWe know how to store m-bit number in a registerHow about many m-bit numbers ?

• Bank of registers?How to fetch a specific m-bit number?

• addressing

MemoryNow that we know how to store bits, we can build a memory –a logical k by m array of stored bits

•••

k = 2n

locations

m bits

Address Space:number of locations(usually a power of 2)

Addressability:number of bits per location(e.g., byte-addressable)

Memory InterfaceThere are two basic operations on a memory

• Selecting one of the memory locations to read from• Selecting one of the memory locations to write to

Interface signals• A – n-bit address lines to select a location• Dout – Contents of selected location during read (m bits)• Din – Value to be stored during write (m bits)• WE – If WE = 1 – write operation, WE = 0, read operation

Memory(2n by m-bit)

An

Din

WE

Dout

m m

MemoryLooking from the outside, what do we need?

13

MemoryLooking from the outside, what do we need?

OUT

INADDR

WE

Memory

Address Spacen bits allow the addressing of 2n memory locations.

• Example: 24 bits can address 224 = 16,777,216 locations

(i.e. 16M locations).

• If each location holds 1 byte (= 8 bits) then the memory is 16MB.

• If each location holds one word (32 bits = 4 bytes) then it is 64 MB.

A large number of addressable fixed size locations

Memory Addressability

• Computers are either byte or word addressable - i.e. each memory location holds either 8 bits (1 byte), or a full standard word for that computer (16 bits for the LC-3, more typically 32 bits, though now many machines use 64 bit words).

• Normally, a whole word is written and read at a time: If the computer is word addressable, this is simply a single address location.

If the computer is byte addressable, and uses a multi-byte word, then the word address is conventionally either that of its most significant byte (big endian machines) or of its least significant byte (little endian machines).

MemoryGiven address, fetch contents at that address• Select or enable one of many locations

OUT

INADDR

WE

14

Page 6 of Sequential1.cdl•To store 4 different “values” we can use 4 different D-latches

• Each stores a 1 bit value• To read from memory, provide an address and read contents at that address:

• Each D-latch has an “address” and we read contents of this one D-latch

•If we want output to come from one of many ‘locations’ • Multiplexer

• Control lines to Multiplexer = Address• How about writing into one of many locations

• Enable one out of many ‘locations’• Decoder

•Control lines to Decoder = Address

Extend Design to: 22 by 3-bit memory

D0

3 3

D1

3 3

D2

3 3

D3

3 3

MU

X

3Dout

A2Read operation

22 or 4 registers

Selects “address” to read

But how do we select/enable ONEof the D-latches ?

Given 2 bit address,Select ONE latch

Recall : The Decodern inputs, 2n outputs• ONLY one AND gate outputs a 1 for each possible input pattern

2-bitdecoder

Think of it like this:put a binary # on AB,turns on the correspondingoutput wire!

Ex: AB=10, 3rd wire turns high, all the other are low

22 by 3-bit memory

D0

3 3

D1

3 3

D2

3 3

D3

3 3

MU

X

3Dout

A2Write operation

WE

3Din

Dec

oder

Limitation:You can only read

or write at any given time

15

address

An Efficient 22 by 3-bit Memory - Single Port

addressdecoder

word WEword select

writeenable

input bits

output bits mux

latch(not flip-flop)

What is different?

D-latchMakes this memory writeable

when clock is HIGH,

22 by 3-bit memory - Multiple “Ports”

D0

3 3

D1

3 3

D2

3 3

D3

3 3

MU

X

3DR

AR

2Independent Read/Write

WE

3DW

Dec

oder

AW 2

You can read from one address and write to

another with thisarrangement

(notice 1 address line for R1 address line for W)

22 by 3-bit memory - Multiple Read Ports

D0

3 3

D1

3 3

D2

3 3

D3

3 3

3DR2

AR2

2

WE

3DW

Dec

oder

AW

3DR1

AR12

2

Read from 2 locationsAt once,

Write to a third!(notice 3 address lines)

(We will use this laterIn something called the:

“register file” for the CPU)

More Memory DetailsThis is still not the way actual memory is implemented

• Real memory: fewer transistors, denser, relies on analog propertiesBut the logical structure is similar

• Address decoder• Word select line, word write enable• Bit line

Two basic kinds of RAM (Random Access Memory)Static RAM (SRAM) - 6 transistors per bit

• Fast, maintains data as long as power appliedDynamic RAM (DRAM) - 1 transistor per bit

• Denser but slower, relies on “capacitance” to store data, needs constant “refreshing” of data to hold charge on capacitor

Also, non-volatile memories: ROM, PROM, flash, …

16

Dynamic RAM• Information stored as charge

on capacitors.• Capacitors leak so values

have to be ‘refreshed’ continually

• As memory chips get larger, access times tend to increase. The processor spends more time waiting for data.This is a major issue limiting

computer systems performance

ExampleIntel Core i5 – Processor

• Clock rates approx 2.5GHz, Clock period approx 0.4 ns

DDR2-667 PC2-5300 SO-DIMM – 2 GB Memory• Can deliver at most 1 64-bit word every 1.5 ns

Mismatch between processor speed and memory speed

Memory Hierarchy• Modern computers try to mitigate memory delays by exploiting locality

of reference through caches. • Smaller, faster memory stores are placed closer to the CPU and bulk

transfers from slower memory are used

CPU

CacheMemories

Main Memory

DisksMagnetic, Flash etc.

Storage in MegaBytes, access times single clock cycles

Storage in GigaBytes, access time 10s of clock cycles

Storage in TeraBytes, access time 1000s of clock cycles

Memory Hierarchy

Will return to this at the end of the course….!

17

Are we ready to design sequential circuits and finite state machines ?

Is something missing ?

When do states change in a machine ?• Aynschronous (arbitrary) or synchronous

Do we let states change at arbitrary times ?Our discussion thus far seems to imply that states/inputs/outputs can change at any time – is this how it works in a computer? NO!

Things work in a synchronized manner – changes occur or are Recorded at specific instances in time….The different components are all marching to the same beat…..the CLOCK!

Clocked Circuits•Subsystem in a computer consists of a large number of combinational and sequential devices

• Each sequential device is like latch which is in one of two states• As machine executes its cycle, the states of all sequential devices

change with time•To control large collection of devices in an orderly (synchronized) fashion, machine maintains a clock

• Requires all devices to change their states at the same time• Clock generates sequence of pulses

• Much easier to design, debug, implement, and test

•How do we change latches so that they allow change in state synchronized with the clock ?

•Sequential logic circuits require a means by which events can be sequenced…..clock!

Introducing - The Clock!A clock controls when stored values are “updated”

• Electrical waveform – sends pulses through a circuit• Oscillating global signal with fixed period

The clock will act as the ‘heartbeat’ of our system• The number of cycles per second is the clock frequency measured in

cycles per second or Hertz (Hz)• The clock period refers to the duration of one clock cycle. The period

and frequency are inversely related.Typical clock frequency: 2.5GHz = 2.5 x109 HzSo corresponding clock period = 1/(2.5 x 109) = .4x10-9 sec

– That would be: 0.4 nanoseconds

“1”

“0”

timeOneCycle

Clock…Page 7

Input to D latch can be written only when clock is high

We can have Write enable (WE) and Clock• Input to D latch written only when WE=1 and Clock is high

18

Attaching Clock to D-Latch• Let’s attach CLOCK to the WE on D-Latch

• We create “windows” of time that we can store data into latchWhen the CLOCK is “HIGH” – D-latch is openWhen the CLOCK is “LOW” – D-latch is closed

• We have to prepare what we wish to store, right before latch closes

CLOCK

D

Q

open openclosed

time

D

WE clock

Let’s Try to Build a Counter using the D-Latch

3-bitD-latch

3 3WE

+13

clock

QD

What is a counter?Counter increments value by 1 at each cycle of clockExample: time = 0, counter = 000

time = 1, counter = 001time = 2, counter = 010

.

.

.

time = 7, counter = 111

Simple 2-bit Counter• count from 0 to 3

• 2 bit encoding A,B of states: 00, 01,10,11• Counts 00 01 10 11

• functions:• A,B current state• A*, B* next state• A* = (A’B) + (A B’) = A XOR B• B* = (A’B’) + (AB’) = B’

A B A* B*

0 0 0 1

0 1 1 0

1 0 1 1

1 1 0 0

Let’s Try to Build a Counter using the D-Latch

3-bitD-latch

3 3WE

+13

clock

QD

We can’t use a D-latch to build a counter Why not?

Let’s say at time=0, D-latch has: 000>This is the input to incrementer, so output = 001>Now 001 is input to the D-latch

Problem:>We can’t guarantee the clock will be low in time to store this new value into the D-latch

19

D Flip-Flop (or master-slave flip-flop)D Flip-Flop is a pair of D latches• Stupid name, but it stuck• Isolates next state from current state

Two phases:• Clock = 1: WE1 =0: Latch #1 closed, WE2 =1: Latch #2 open• Clock = 0: WE1 =1: Latch #1 open, WE2 =0: Latch #2 closed

D

Clock

QLatch #1

Latch #2

Qinter

WE1 WE2

D Flip-Flop timing Diagram

D

Qinter

Q

D

Clock

QLatch #1

Latch #2

Qinter

Clock L1-closedL2-open

L1-openL2-closed

L1-closedL2-open

L1-openL2-closed

WE1 WE2

D Flip-Flop vs. D-Latch

We refer to the D flip flop as an edge-triggered device. • D=Q ONLY when WE changes from 0 to 1

This differs from D latch, which is: level-triggered• D=Q anytime WE equals 1

3-75 3-75

D

Q

WE

Timing Diagram for DFF:

D Flip-Flop vs. D-Latch

We refer to the D flip flop as an edge-triggered device. • D=Q ONLY when WE changes from 0 to 1

This differs from D latch, which is: level-triggered• D=Q anytime WE equals 1

D

Q

WE

Timing Diagram for D-Latch:

20

D Flip-Flop• We can think of the D Flip-Flop as a 1 bit storage container with an

input, D, and an output, Q.• The D flip-flop takes a clock input (often denoted with a triangle)• A set of D flip-flops can be grouped together with common Clock and

WE inputs to form a register. A key component in our processor

D Q

Clock

Flip-Flop

Correct 2-bit counter implementationPage 9 of Sequential1.cdl

Using D-flip flops (and replacing D-latch with Master-Slave configuration)

Use a clocked register (made of D flip-flops)

D-ff3 3

+13

Clock

Working Counter• Incrementer (+1) computes the next value of the state register

D-ff3 3

+13

Clock

Counter Timing Diagram

D Q

Clock

D

Q 0 1 2 3 4 5

1 2 3 4 5 6

21

Finite State Machine Representation of Counter

000

001

010

011

100

101

110

111

Reset

Bubbles represent all possible “states” for themachine (aka your flip-flopbased circuit)

Arrows show movement fromone state to the next

Transitions occur at pulse of the clock

Truth Table Representation of Counter

Present State Next StateD2 (t) D1 (t) D0 (t) D2 (t+1) D2 (t+1) D0 (t+1)

0 0 0 0 0 10 0 1 0 1 00 1 0 0 1 10 1 1 1 0 01 0 0 1 0 11 0 1 1 1 01 1 0 1 1 11 1 1 0 0 0

Summary: 3 “Storage” Devices

D QD

WE

DFF QD

CLK

RSQ

S Q’R

RS Latch – Stores 1 Bit, Level-Triggered-1 “forbidden” input: S=0, R=0-Holds Data when RS=11

D-Latch – Stores 1 Bit, Level-Triggered-No “forbidden” inputs (fixes RS Latch)-D=Q when WE=1-Holds Data when WE=0

D-Flip-Flop – Stores 1 Bit, Edge-Triggered-No “forbidden” inputs-D=Q when WE (CLK) transitions from 0 to 1-Holds Data for WE=1 or WE=0

-Except when WE transitions from 0 to 1

Finite State Machine• The counter we designed is an example of a finite state machine.• In general a Finite State Machine consists ofAn n-bit register which stores the state of the machineA block of logic that computes the next state as a function of the

current state and the inputs, if anyA block of logic which computes the output based on the current

state.

StateRegister

NextState

Function

OutputFunction

ClockCombinationalLogic Blocks

InputsOutputs

22

One Last Thing…D Flip-Flop with Additional Write Enable

• From previous slides, we attached clock to WE of the D-flip-flop• Now, we add another WE line to the flip flopJust holds onto data already stored in DFF

• Give it the ability to “ignore” the clock!

D Q

Clock

Flip-Flop

WE

w/WE

01 D Q

Clock

DFF

WE

Next….• Procedure for designing Sequential circuits (to implement Finite State Machine)

• Storage Device to store state: D flip flop• Logic to implement next state: combinational gates/devices• How to derive the logic: truth tables