JONNY INGMAN, JONI JORMANAINEN, ELENA MENGOTTI … · 1/8/2018 · JONNY INGMAN, JONI JORMANAINEN,...

Transcript of JONNY INGMAN, JONI JORMANAINEN, ELENA MENGOTTI … · 1/8/2018 · JONNY INGMAN, JONI JORMANAINEN,...

—

—JONNY INGMAN, JONI JORMANAINEN, ELENA MENGOTTI

H3TRB-HVDC on SiCA relevant test for industrial applications

—Reliability

January 8, 2018 Slide 2

Definitions

Reliability versusQuality

• Quality is like a picture• Reliability is like a video• Reliability is quality from the

beginning to the end

Reliability versusRobustness

• Robustness is surviving thetest once

• Reliability is surviving thetest repetitively orcontinuously

• Robustness short term –reliability require time

Physics of Failure, PoF

• The use of science (physics, chemistry, etc.) to captureunderstanding of failuremechanisms and to evaluateuseful life under actualoperating conditions

Reliability is theprobability of a deviceor a system to perform

• Required function• Under stated conditions• Specified period of time

—

January 8, 2018 Slide 3

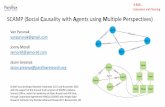

SiC ReliabilityA zoo of possible tests for reliability of semiconductors

HTRBHigh Temperature

Reverse BiasSCSOA

Short Circuit

BDCBody Diode

UIS – ARUnclamped InductiveSwitching Avalanche

RSCORepetitive Surge

Current Operation

HTGBHigh Temperature

Gate Bias

NBTINegative Bias

Threshold Instability

CRRCosmic Ray Robustness

DBCForward BiasDegradation

PC – IOLPower Cycling

DRBDynamic Reverse

Bias – Passive dVdt

THB Switched

H3TRB – HVDCHigh Temperature High

Humidity Reverse Bias HighVoltage Direct Current

No standard for SiC yet established. Up to now it is all based on Si experience…What is

important? What is less relevant? What is new compared to Si? What is more chip related and what is more package related? Where should

the focus be?

... And many more others....

Gate Voltage step test

—H3TRB – HVDC tester

January 8, 2018 Slide 4

Focus on passivation layer, chip edge termination and device package

ABB H3TRB – HVDC Test Specification

Temperature, T 85 °C

Relative humidity, r.H 85%

Voltage, V 80% of VN (rated voltage)

Gate voltage, VGS 0V

Time, h Min 1200h

Failure criteria 1, F1 IDS < 2 ∙ IDS_ref for 1200h

Failure criteria 2, F2 IDS < 10 ∙ IDS_ref from 1200h

Failure criteria 3, F3 Short

H3TRB-HVDC Humidity 85%, T=85° and 80%

rated voltage. Address the passivation layer, but also the chip edge termination and its underlying structures. Combination of high Voltage and Humidity is essential for field application. Important test that should become a standard.

HTRB The expected failure mode is a gradual

degradation of the chip breakdown strength due to the presence of polar/ionic contaminants disturbing the field termination structure. Passed no problem.

THB 80 Add humidity but max 80 V – limited

relevance for LV MV. Passed no problem.

—H3TRB – HVDC test setup

January 8, 2018 Slide 5

Main features

• Simultaneous online measurements of up to 132 DUTs

• DUTs of up to 3 different voltage levels can be tested simultaneously

• Sampling rate up to 100ms• Flexible setup for testing

different semiconductors (IGBTs, MOSFETs, Diodes, Thyristors)

• Leakage current constantly monitored (shunt R) and recorded with LabVIEW SW

• Backup of data to network drive • SMS, e-mail notification for EoL

failure• Remote monitoring • UPS support for SW• Variable shunt resistors (MUX

system) • No V=0 if one fails Relay board

—SiC Reliability

January 8, 2018

Slide 6

Analysis procedure

Failure occurrence

X-ray El. characterization

Aging of DUTs

Comparison with the pre aging

Sample pre

characterization

Package removal

Locating failure chip

Physical analysis of chip

For selected DUTs

Locating failure package

Physical analysis of package

For selected DUTs

LIT

SEM

optical

Estimation of failure mechanism

Investigation of failure

circumstances

DUTs status monitoring

Reliability analysis: pdf, time to

failure, suppliers comparison….

Failure

understanding - PoF

SiC know-how

Investigation of aging

effect

Confirm with other DUTs

tests comparison

Cross Section

SAM

SEM EDX

optical

In house

External

CT

X-ray

FIB

—Samples pre-characterization

January 8, 2018 Slide 7

TO package 1700 MOSFET

Termination 1700 V: A 90 µm vs. B 185 µm. Termination 1200 V: A 95 µm vs. B 160 µm.

Huge void percentage in the B solder (13% max measured).

Both positive T dependency.

Supplier Partnr.

Voltage[V]

Current[A]

Void[%]

Std Chip area[mm2]

Length[mm]

Width[mm]

Termination[µm]

Active area[mm2]

A 1700 0.88 0.48 1.6 1.45 1.11 90 1.38

B 1700 4.71 1.70 2.66 1.62 1.64 185 2.09

A

B

B A

BA

—

A

B

Test Results

January 8, 2018 Slide 8

Leakage current monitoring during the test

DUT A: Only 2 DUT failures (F1).

DUT B: All tested DUTs failed (F1 & F2). No short (F3) but high leakage increase in first 300 h. In total 5000 times initial Iref value (µA range).

DUT A termination width half of DUT B but still no aging.

—Post comparison

January 8, 2018 Slide 9

Electrical static measurements

DUT A: Minimal shift in electrical parameters.DUT B: ~10 000 time increase in drain to source leakage

current.~2 500 time increase in gate to source leakage

current.

A IDSS B IDSS

Confirmation of the behavior seen inside the chamber. Huge increase in DUT B also at room T after bake out. This huge variation is NOT shown in the datasheet (value still within the datasheet).

—H3TRB-HVDC

January 8, 2018 Slide 10

EoL cases on SiC devices not shown so far

RCA: Excessive step height/profile at the intersection of the Field Oxide and the Gate Oxide caused localized layer discontinuity/trapped contamination.

Diodes 1200 V: Burned trace between pin 2 and 3.

Field breakdown over the termination in less than 200h.

—

So far 710 DUTs have been tested.

About 75% are SiC MOSFETS and diodes,

the rest are Si IGBTs, diodes and thyristors.

Supplier benchmarking

January 8, 2018 Slide 11

0

10

20

30

40

50

60

70

80

90

100

0

5

10

15

20

25

A B C D E F G

FA

ILU

RE

RA

TE

%

NU

MB

ER

OF

SA

MP

LE

S

Supplier Benchmarking up to 1200hSiC MOSFET (Batch 1)

Number of Samples F1 Failure Rate % F2 Failure Rate % SC Failure Rate %

Failure Type Definition

Failure criteria 1, F1 IDS < 2 ∙ IDS_ref for 1200h

Failure criteria 2, F2 IDS < 10 ∙ IDS_ref from 1200h

Failure criteria 3, F3 Short

—

• Very powerful test combining humidity and reverse bias. EoL failures generated within 1200 h and corrective action to be taken by suppliers.

• Long term ruggedness of SiC-based semiconductors to industrial environmental conditions is assessed - Both chip level degradation as well as package related issues detected.

• Compare with Iref and not just to datasheet value. Failures according to IEC60749 standard (2x Iref) were generated during the 1200 h testing.

• Test is strongly recommended to be performed at the supplier site as a standard test (at 80% of nominal voltage).

• The initial phase of SiC R&D focused more on performance, reliability is being studied now more actively although standards and guidelines are still missing.

• Improvements are coming and no showstopper for SiC have been identified.

• Handling the diverse reliability aspect for the different application is the role of standards committees, including review of existing standards, modify them for SiC, introduce additional ones… not an easy task to get the voice heard.

H3TRB-HVDC

January 8, 2018 Slide 12

Conclusions and Outlook