Future HDI Project – Definition Stage HDPUG Meeting (Japan) – December 10-11, 2014 Chair: Ivan...

-

Upload

gervais-mason -

Category

Documents

-

view

216 -

download

0

Transcript of Future HDI Project – Definition Stage HDPUG Meeting (Japan) – December 10-11, 2014 Chair: Ivan...

Future HDI Project – Future HDI Project – Definition StageDefinition Stage

HDPUG Meeting (Japan) – December 10-11, 2014

Chair: Ivan Straznicky, Curtiss-Wright

Facilitator: Jack Fisher

BackgroundBackground

• BGA pitch is moving steadily downward.– 1mm and 0.8mm common in Telecom/Server, seeing 0.5mm

and 0.4mm

– Consumer electronics use Any Layer Via (ALV) HDI PCBs to support very fine pitch BGAs with large arrays

– These are typically very thin, 0.8mm or less → too thin for Telecom/Server and Aerospace/Defense

• Data transmission speeds continue to increase– E.g. 10G→40G →100G Ethernet

– Backdrilling of through hole vias is becoming common

– ALV allows “stub”-less designs (with exceptions like connectors)

• PCB routing/via density continues to increase.– More BGA pads in same area

ConceptConceptFeatures

Two “Any layer” outer sub “stack” constructions (Sintered Cu paste)

Internal conventional multilayer “core” with offset buried vias

Layers 1/2 and n/n-1 are plated Cu, not sintered paste

Layers 1/n PTH (e.g. for press-fit connectors)

Maximum of 4 laminations, 2 plating steps (3 with VIPPO)

Not to scale – top and bottom stacks are thinner (≤0.8mm) than the core (~1.4mm)

Performance & Reliability QuestionsPerformance & Reliability Questions

• Current carrying capability– What is the maximum current a stack of sintered Cu paste vias can

support? (Stack height/via size function)

• Lead-free survivability & IST reliability– What is the Pb-free survivability and IST thermal cycle reliability of a stack

of microvias in a thick composite board?

• CAF– Are the sintered Cu paste vias susceptible to CAF? (At what dimensions?)

• Component interconnect reliability– Will CTE mismatch strains cause failures in the ALV/stack?

• Material stability– How stable is the sintered Cu paste vs plated Cu (e.g. thermal aging)?

• Electrical performance– Related to material stability, what is the electrical performance of series of

sintered Cu paste vias?

Project DefinitionProject Definition

• Define/Design a test vehicle to answer the questions and serve as a development platform for PCB fabricators– 18” x 24” panel size with the following areas:

• IST & Delam coupons (PWB Interconnect Solutions)

• Current carrying capability coupons (Oracle)

• CAF coupons (PWB Interconnect Solutions)

• High strain part assembly daisy chain boards (UIC/AREA?)

• Impedance/TDR coupons (Polar Instruments?)

– Include 10 layer stacked ALV’s at 0.5mm, 0.4mm and 0.35mm pitch (at least for CAF coupons)

• Fabricate TVs at multiple fabricators. They choose the methods and materials.– 4 companies committed to support this: TTM Meadville, Viasystems,

Sanmina, Kyocera. Other are also interested (i3).

– Proposed minimum of 8 panels from each fabricator

Project Definition (2)Project Definition (2)

• Assemble and Reflow conditioning (6 x 260°C)– IST & Delam coupons (Curtiss-Wright or PWB Interconnect

Solutions)

– Current carrying capability coupons (Oracle)

– CAF coupons (PWB Interconnect Solutions?)

– High strain part assembly boards (UIC/AREA?)

– Impedance/TDR coupons (Polar Instruments?)

• Test– IST & Delam (PWB Interconnect Solutions)

– Current carrying capability (Oracle)

– CAF (PWB Interconnect Solutions or i3)

– ATC (Alcatel-Lucent)

– TDR/SET2DIL (Polar?)

Project Definition (3)Project Definition (3)

• Common and coupon-specific features– 10 layers ALV on top and bottom sides

– At least 4 layers in core (target 3mm total thickness of board)

– Core buried via size and pad (10 mil drill, 20 mil pad)

– Microvia sizes, pads, SM clearances, etc. being discussed

– Locations of planes (1 oz) and “signal” layers (1/2 oz) being discussed

– Stack heights/combinations for various coupons TBD

– Trace widths for various coupons TBD

– High strain daisy chain part – considering CBGA-483

– CAF: use MRT design but with ALV stacks

– CCC: 20C temp. rise max. and max. current

– TDR: impedance circuits with and w/o microvia stacks

Next StepsNext Steps

• Continue test vehicle definition (test panel design group)– Design team includes: Ivan, Bill B., Mike Freda, Polar Instruments, Joe

Smetana, AREA Consortium

• Continue resource definition and commitment

• Create project plan with schedule

• Move into Implementation stage by 1Q 2015

Thank youThank you

Questions?Questions?

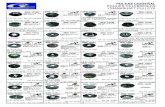

![INHALT - CONTENTS - MATIÈRE · RHZ(DW10ATED); (66kW-120kW) 1.6 HDi; 1.6 HDi 110; 1.6 HDi 110 FAP; 1.6 HDi 110 FAP [04]; 1.6 HDi 110FAP; 1.6 HDi 90; 1.6 HDi 90 [04]; 2.0 HDi; 2.0](https://static.fdocuments.in/doc/165x107/605cc6e9948bf00b8613e09d/inhalt-contents-matire-rhzdw10ated-66kw-120kw-16-hdi-16-hdi-110-16.jpg)