Fabrication Process

description

Transcript of Fabrication Process

1CONCORDIA

VLSI DESIGN LAB

Fabrication Process

•Crystal Growth

•Doping

•Deposition

•Patterning

•Lithography

•Oxidation

•Ion Implementation

2CONCORDIA

VLSI DESIGN LAB

Fabrication- CMOS Process

Starting Material Preparation

1. Produce Metallurgical Grade Silicon (MGS) SiO2 (sand) + C in Arc Furnace Si- liquid 98% pure

2. Produce Electronic Grade Silicon (EGS) HCl + Si (MGS) Successive purification by distillation Chemical Vapor Deposition (CVD)

3CONCORDIA

VLSI DESIGN LAB

Fabrication: Crystal Growth

Czochralski Method

Basic idea: dip seed crystal into liquid pool

Slowly pull out at a rate of 0.5mm/min

controlled amount of impurities added to melt

Speed of rotation and pulling rate determine diameter of the ingot

Ingot- 1to 2 meter long Diameter: 4”, 6”, 8”

4CONCORDIA

VLSI DESIGN LAB

Fabrication: Wafering

Finish ingot to precise

diameter Mill “ flats” Cut wafers by diamond

saw: Typical thickness

0.5mm Polish to give optically flat

surface

5CONCORDIA

VLSI DESIGN LAB

Fabrication: Oxidation

Silicon Dioxide has several uses:- mask against implant or diffusion- device isolation- gate oxide- isolation between layers

SiO2 could be thermally generated or through CVD

Oxidation consumes silicon

Wet or dry oxidation

Quartz Tube

Wafers

Quartz Carrier

Resistance Heater

O2 or Water Vapor

Pump

6CONCORDIA

VLSI DESIGN LAB

Fabrication: Diffusion Simultaneous creation of p-n

junction over the entire surface of wafer

Doesn’t offer precise control Good for heavy doping, deep

junctions Two steps:

Pre-depositionDopant mixed with inert gas introduced in to a furnace at 1000 oC.Atoms diffuse in a thin layer of Si surfaceDrive-inWafers heated without dopant

Resistance Heater

wafers

Temp: 1000

Dopant Gas

7CONCORDIA

VLSI DESIGN LAB

Fabrication: Ion Implantation

Precise control of dopant Good for shallow junctions and threshold adjust Dopant gas ionized and accelerated Ions strike silicon surface at high speed Depth of lodging is determined by accelerating field

8CONCORDIA

VLSI DESIGN LAB

Fabrication: Deposition

Reactant0.1 -1 Torr

Loader

Pump

Used to form thin film of Polysilicon, Silicon dioxide, Silicon Nitride, Al.

Applications: Polysilicon, interlayer oxide, LOCOS, metal.

Common technique: Low Pressure Chemical Vapor Deposition (CVD).

SiO2 and Polysilicon deposition at 300 to 1000 oC.

Aluminum deposition at lower temperature- different technique

9CONCORDIA

VLSI DESIGN LAB

Fabrication: Metallization Standard material is Aluminum

Low contact resistance to p-type and n-type

When deposited on SiO2, Al2O3 is formed: good adhesive

All wafer covered with Al

Deposition techniques: Vacuum Evaporation Electron Beam Evaporation RF Sputtering

Other materials used in conjunction with or replacement to Al

10CONCORDIA

VLSI DESIGN LAB

Fabrication: Etching

Wet Etching Etchants: hydrofluoric acid (HF), mixture of nitric acid and HF Good selectivity Problem: - under cut - acid waste disposal

Dry Etching Physical bombardment with atoms or ions good for small geometries. Various types exists such as: Planar Plasma Etching Reactive Ion Etching

Plasma Reactive species

RF

11CONCORDIA

VLSI DESIGN LAB

Fabrication: Lithography Mask making

Most critical part of lithography is conversion from layout to master mask

Masking plate has opaque geometrical shapes corresponding to the area on the wafer surface where certain photochemical reactions have to be prevented or taken place.

Masks uses photographic emulsion or hard surface

Two types: dark field or clear field

Maskmaking: optical or e-beam

12CONCORDIA

VLSI DESIGN LAB

Lithography: Mask making

Optical Mask Technique

1. Prepare Reticle Use projection like system: -Precise movable stage -Aperture of precisely rectangular size and angular orientation -Computer controlled UV light source directed to photographic plate After flashing, plate is developed yielding reticle

13CONCORDIA

VLSI DESIGN LAB

Fabrication: Lithography

Step & Repeat

Printing

Printing

14CONCORDIA

VLSI DESIGN LAB

Lithography: Mask making

Electron Beam Technique

Main problem with optical technique: light diffraction

System resembles a scanning electron microscope + beam blanking and computer controlled deflection

15CONCORDIA

VLSI DESIGN LAB

Patterning/ Printing

Process of transferring mask features to surface of the silicon wafer.

Optical or Electron-beam

Photo-resist material (negative or positive):synthetic rubber or polymer upon exposure to light becomes insoluble ( negative ) or volatile (positive)

Developer: typically organic solvant-e.g. Xylen

A common step in many processes is the creation and selective removal of Silicon Dioxide

16CONCORDIA

VLSI DESIGN LAB

Patterning: Pwell mask

17CONCORDIA

VLSI DESIGN LAB

Patterning/ Printing

substrate

SiO2

18CONCORDIA

VLSI DESIGN LAB

Fabrication Steps

Apply PR

Pre-bake

Printer align expose mask

Develop, rinse, dry

Post bake

Inspect, measure

Etch

Strip resist

Deposit or grow layer

19CONCORDIA

VLSI DESIGN LAB

Fabrication Steps

20CONCORDIA

VLSI DESIGN LAB

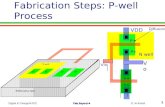

Fabrication Steps: P-well Process

Diffusion

VDD

Vo

P well

P+

P+

n+

n+

Vin

p+

P well

p+p+ p+n+ n+

Substrate n-type

21CONCORDIA

VLSI DESIGN LAB

Fabrication Steps: P-well Process

Diffusion

VDD

Vo

P well

P+

P+

n+

n+

Vin

p+

P well

p+p+ p+n+ n+

Substrate n-type

22CONCORDIA

VLSI DESIGN LAB

Fabrication Steps

n+n+

P well

p+ p+

Substrate n-type

P well

n+ n+p+ p+

23CONCORDIA

VLSI DESIGN LAB

Fabrication StepsOxidation

Substrate n-type

Patterning of P-well mask

Substrate n-type

oxide

24CONCORDIA

VLSI DESIGN LAB

Fabrication StepsDiffusion: p dopant,Removal of Oxide

Deposit Silicon Nitride

P-well

P-well

Si3N4

25CONCORDIA

VLSI DESIGN LAB

Fabrication StepsPatterning: Diffusion (active) mask

Oxidation

P-well

substrate

FOXFOX FOX

substrate