Clock, Slow Control and ECS signals distribution in the Calorimeter Front-end Crate

description

Transcript of Clock, Slow Control and ECS signals distribution in the Calorimeter Front-end Crate

Laboratoire de l’Accélérateur Linéaire (IN2P3-CNRS) Orsay, France

LHCb Calorimeter upgrade meeting Olivier Duarte

Clock, Slow Control and ECS signals distribution in the Calorimeter Front-end

CrateReminder Calorimeter Front-end Crate 3U and 6U Backplane Detail of each slot SLVS specification

Clock distribution in Calorimeter Front-end CrateSlow Control and Detector Command (ECS) distribution in

Calorimeter Front-end Crate Data

Olivier Duarte

Calorimeter front-end crate

2LHCb Calorimeter upgrade meeting

2 Backplanes (6U and 3U) 6U backplane

Neighbours L0 data Delatcheur command Crate Id

3U Backplane Power Supply Clock distribution TTC command (or Control

command) Slot Id SPEC distribution

Olivier Duarte

3U Backplane CROC Slot

3LHCb Calorimeter upgrade meeting

Connection between CROC and FEB Through 3U Backplanes

1 differential pair between each slot (FEB or TVB) and CROC (type point 2 point)

9 differentials pair common on all the slot inside the same crate (type bus)

Olivier Duarte

3U Backplane FEB Slot

4LHCb Calorimeter upgrade meeting

Connection between CROC and FEB Through 3U Backplanes

1 differential pair between each slot (FEB or TVB) and the CROC (type point 2 point)

9 differentials peer common on all the slot inside the same crate (type bus)

Olivier Duarte

6U Backplane slot organization

5LHCb Calorimeter upgrade meeting

Olivier Duarte

6U Backplane CROC Slot

6LHCb Calorimeter upgrade meeting

Connection between CROC and FEB Through 6U Backplanes 4 differentials pair between each slot (FEB or TVB) and the CROC

(type point 2 point)

Olivier Duarte

6U Backplane FEB slot

7

E-Port

LHCb Calorimeter upgrade meeting

Connection between CROC and FEB Through 6U Backplanes 4 differentials pair between each slot (FEB or TVB) and the CROC

(type point 2 point)

Olivier Duarte

6U Backplane Validation slot

8

E-Port

LHCb Calorimeter upgrade meeting

Connection between CROC and FEB Through 6U Backplanes 4 differentials pair between each slot (FEB or TVB) and the CROC

(type point 2 point)

Olivier Duarte

SLVS specification

SLVS (Scalable Low Voltage Standard) JEDEC standard: JESD8-13 Differential voltage based signaling protocol.

Voltage levels compatible with deep submicron processes. Typical link length runs of 30cm over PCB at 1Gbps. Low Power, Low EMI

Application in data links for Flat Panel displays in mobile devices. Mobile Pixel Link, MPL-2 (National semi.)

Kostas Kloukinas’s slide

9

SLVS specifications brief

2 mA Differential maxLine impedance: 100 OhmSignal: +- 200 mVCommon mode ref voltage: 0.2V0.2V

1.2V400mV

200mV

LVDS

SLVS

LHCb Calorimeter upgrade meeting

Olivier Duarte

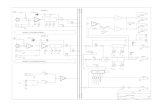

Clock distribution in Calorimeter Front-end Crate through 3U Backplane

GBT on board On new CROC board

2 GBTX chip with bidirectional optical fiber

1 SCA chip (CROC Ctrl/Cmd) On the new Calorimeter FEB

4 GBTX chip (one way) 1 SCA chip (FEB Ctrl/Cmd)

10

New CROC

New FEB

Clk managerClk[7:0]In Ref

Down-link

Uplink

General Ctrl

GBTX

E-Port

E-Port

E-Port

E-Port

2 GBTX

E-Port SCA

Network Controller

User Buses :

{I2C, //, SPI, JTAG, 12bADC,…}

1 SCA

One GBTX master SLVS-LVDS

translator

Buffer

Clk[0]

3U Backplane CROC Slot

2 bidir link

3U Backplane FEB Slot

Clk managerClk[7:0]In Ref

Down-link

Uplink

General Ctrl

GBTX

E-Port

E-Port

E-Port

E-Port

AC

TEL

FPG

A (A

3PE1

500)

LVS-SLVS translator

4 GBTX (One way) Ana

log

FE p

art

(8 C

hann

els)

E-Port SCA

Network Controller

User Buses :

{I2C, //, SPI, JTAG, 12bADC,…}

Clock_Feb(n)

17 E-Port SCA Max for 1 GBTX

Inside GBTX ??

One

way

link

LHCb Calorimeter upgrade meeting

Pending question Is it possible to use translator SLVS <-> LVDS ? Or inside GBT ? See CRT 758 data sheet

Olivier Duarte

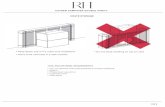

Slow Control distribution in Calorimeter Front-end Crate through 6U Backplane

11

New CROC

Clk managerClk[7:0]In Ref

Down-link

Uplink

General Ctrl

GBTX

E-Port

E-Port

E-Port

E-Port

2 GBTX

E-Port SCA

Network Controller

User Buses :

{I2C, //, SPI, JTAG, 12bADC,…}

1 SCA

SLVS-LVDS translator

Buffer

Clk[0]

2 bidir link

E-Port SCA_NewCROC

E-Port SCA_NewCROC

E-Port_FEBE-Port_TVB

x (18)

6U Backplane CROC Slot

4 pairs 1 free

TranslatorSLVS-LVDS

FPGA, Buffer, …

LHCb Calorimeter upgrade meeting

One GBTX master

Slow Control transmission Translator with FPGA ? 4 pairs available GBT E-Port 3 pairs used 1 pair free

Olivier Duarte

Slow Control distribution in Calorimeter Front-end Crate through 6U Backplane

12

New FEB

Clk managerClk[7:0]In Ref

Down-link

Uplink

General Ctrl

GBTX

E-Port

E-Port

E-Port

E-Port

AC

TEL

FPG

A (A

3PE1

500)

LVS-SLVS translator

4 GBTX (One way) Ana

log

FE p

art

(8 C

hann

els)

E-Port SCA

Network Controller

User Buses :

{I2C, //, SPI, JTAG, 12bADC,…}

6U Backplane FEB Slot

4 pairs 1 free

TranslatorSLVS-LVDS

FPGA, Buffer, …

LHCb Calorimeter upgrade meeting

Slow Control transmission Translator with FPGA ? 4 pairs available GBT E-Port 3 pairs used 1 pair free

Olivier Duarte

ECS commande (Channel B, Rst, …) distribution in Calorimeter Front-end Crate -

through 3U Backplane

13

New CROC

Clk managerClk[7:0]In Ref

Down-link

Uplink

General Ctrl

GBTX

E-Port

E-Port

E-Port

E-Port

2 GBTX

E-Port SCA

Network Controller

User Buses :

{I2C, //, SPI, JTAG, 12bADC,…}

1 SCA

?? SLVS-LVDS translator

Buffer

Clk[0]

2 bidir link

E-Port SCA_NewCROC

E-Port SCA_NewCROC

E-Port_FEBE-Port_TVB

x (18)

TranslatorSLVS-LVDSFPGA, Buffer, …

LHCb Calorimeter upgrade meeting

3U Backplane CROC Slot

3U Backplane FEB Slot

New FEB

Clk managerClk[7:0]In Ref

Down-link

Uplink

General Ctrl

GBTX

E-Port

E-Port

E-Port

E-Port

AC

TEL

FPG

A (A

3PE1

500)

LVS-SLVS translator

4 GBTX (One way) Ana

log

FE p

art

(8 C

hann

els)

E-Port SCA

Network Controller

User Buses :

{I2C, //, SPI, JTAG, 12bADC,…}

TranslatorSLVS-LVDS

FPGA, Buffer, …

ECS cmd transmission Used the same way (pins) as

currently !

Olivier Duarte

Data

14

New FEB

Clk managerClk[7:0]In Ref

Down-link

Uplink

General Ctrl

GBTX

E-Port

E-Port

E-Port

E-Port

AC

TEL

FPG

A (A

3PE1

500)

LVS-SLVS translator

4 GBTX (One way) Ana

log

FE p

art

(8 C

hann

els)

E-Port SCA

Network Controller

User Buses :

{I2C, //, SPI, JTAG, 12bADC,…}

TranslatorSLVS-LVDS

FPGA, Buffer, …

Readout Crate

TELL

40

TELL

40

TELL

40

TELL

40

TELL

40

TELL

40

4 One way link per FEB

16 FEB

LHCb Calorimeter upgrade meeting

On New Calorimeter FEB 4 GBTX chip (one way) 1 SCA chip

Olivier Duarte

Summary

LHCb Calorimeter upgrade meeting 15

On the new CROC Board, 2 GBTX chip with bidirectional optical fiber and one SCA Chip.

On the new Calorimeter FEB, 4 GBTX (one way) and one SCA chip.

For the Clock distribution we will use SLVS <-> LVDS translator to transmit LVDS signals on 3U Backplane. Or is it possible with FPGA ?

Slow control distribution, 1 pair free. (3 pair for each E-port, 4 pair on the 6U backplane !)

Transmission of the ECS command through the 3U backplane

Is it necessary to transmit SLVS on the backplane ??

Olivier Duarte

Spare

LHCb Calorimeter upgrade meeting 16

Olivier Duarte

CRT758 Data Sheet

17LHCb Calorimeter upgrade meeting

Olivier Duarte

CRT758 Data Sheet (2)

18LHCb Calorimeter upgrade meeting

Ken Wyllie, CERN LHCb electronics, 14th June 201219

FEModule

FEModule

Phase – Aligners + Ser/Des for E – Ports

FEModule

E – PortE – Port

E – Port

GBT – SCA

E – Port

Phase - Shifter

E – PortE – Port

E – PortE – Port

CDR

DEC/DSCR

SER

SCR/ENC

I2C MasterI2C Slave

Control Logic Configuration

Clock[7:0]

CLK Manager

CLK Reference/PLL

External clock reference

One 80 Mb/s port

I2CPort

I2C (light)

JTAG

JTAGPort

80, 160 and 320 Mb/s ports