CLK Jitter CrossTalk Skew VGood

-

Upload

umesh-parashar -

Category

Documents

-

view

20 -

download

0

description

Transcript of CLK Jitter CrossTalk Skew VGood

-

2002 Fairchild Semiconductor Corporation MS500736 www.fairchildsemi.com

March 2002Revised March 2002

Section 6 - N

oise

, Cro

ss

-talk, Jitte

r, Skew

, a

nd EM

I Backpla

ne

Designer

s G

uide

Section 6 - Noise, Cross-talk, Jitter, Skew, and EMIBackplane Designers Guide

This section discusses backplane signal integrity, focusing on the phenomena and effects that can disrupt clean signalsand high signal integrity. Enemies of signal integrity include noise, cross-talk, jitter, skew, and electromagnetic interference(EMI).All electronic systems contain some elements of these phenomena. The key to designing for high signal integrity is thereduction of these phenomena below levels that will adversely affect signal quality. This discussion will focus on whatcauses these phenomena, and what can be done during system design to reduce or eliminate the causes.As backplane frequencies increase, the effects of these phenomena become more pronounced. This, in turn, requirestighter control of layout and design to minimize detrimental effects on signal integrity. The result is an ever-tightening spiralthat creates a battle between the backplane designer and the phenomena that can ruin signal integrity. Poor signal integrity will limit backplane speed and adversely affect system reliability. Conversely, achieving a high level ofsignal integrity within the constraints of the design will result in a high-performing, reliable backplane design.

Section ReferenceThis section presents information covering: Noise (Ground Bounce, Ringing, and Reflections) Signal Cross-talk Jitter Skew Electromagnetic Interference (EMI)

Section Section Title Contents

1 Introduction Application demands, basic backplane considerations, and how to use this guide.

2 Backplane Protocols Descriptions of different backplane bus protocols, including PCI- and VME-based protocols.

3 Backplane ArchitectureTopics relevant to backplane configuration, including parallel versus serial configuration and different configuration topologies and timing architectures

4 Backplane Design ConsiderationsIssues relevant to backplane layout, including distributed capacitance, transmission line effect, stub length, termination, and throughput.

5 Backplane Signal Drivingand Conditioning

Signal driving and conditioning, including power consumption, rise/fall time, propagation delay, flight time, device drive, pin conditioning, live insertion, and incident wave switching.

6 Noise, Cross-talk, Jitter, Skew and EMIA review of the enemies of signal integrity and high frequency.

7 Transceiver Technologies Detailed information about the following technologies: TTL-based (ABT, FCT, and LVT); ECL; and GTLP.8 Mechanical Considerations Information about mechanical considerations such as backplane

chassis/cages and connectors.

9 Layout ConsiderationsPhysical layout of the receiver and driver cards plugged into the backplane, primarily focusing on construction of the physical layer and the configuration of the devices that comprise the cards.

-

www.fairchildsemi.com 2

NoiseMany factors generate noise in a system. The most signifi-cant noise-generating factors are ringing, cross-talk, andEMI. Ringing is the oscillations of the signal level after astate change. It is caused by three sources: device switch-ing noise, system switching noise, and transmission linereflections.Noise of all types has the single largest effect on system-signal integrity. Large amounts of noise will change theshape of signal edges, change edge placement in time,and induce voltage spikes and voltage droops (a voltagedroop is defined as a momentary reduction of the voltagelevel) onto static signals. These voltage transients affecthow the receivers sense the input signal. A change to signal edges affects the shape of the edge andthe time at which the edge arrives at the receiver. If voltagetransients cross device threshold levels, the receiver willchange states. The results are data corruption, and, if theproblem is serious enough, system failure. High levels of noise cause a significant reduction in systemreliability, speed, and overall performance. The systemdesigner can make choices that will control and limit noise. The I/O technology selection has a significant impact onnoise and overall system performance, because theamount of noise a system can tolerate is directly propor-tional to the noise tolerance of the I/O technology.

Device-Switching Noise Device-switching noise can add significantly to a systemsnoise level. By ensuring the best fit of I/O technology tosystem design needs, as well as proper layout, a back-plane designer can control the detrimental effects ofdevice-switching noise. I/O technologies contribute to system noise in the forms ofground bounce and dynamic threshold shift. How well a

technology rejects these and other noise transients is theI/Os noise rejection, which is measured as noise margin.

Noise MarginNoise margin is the amount of input noise a device can tol-erate and still maintain the integrity of the logic levels. Itcan be quantified by measuring input threshold levels.These levels are usually specified in the databook as Volt-age Input High Level (VIH) and Voltage Input Low Level(VIL). The ratings specify at what voltage level the inputgate will change state. In digital systems, one device output gate usually drivesanother device input gate. For example, an output gatewhose voltage output is HIGH (VOH) will drive an input gateto a high state when the input reaches its VIH thresholdlevel. The difference between the two, VOH - VIH, repre-sents the noise margin. The equation for voltage high noisemargin is:

The equation for voltage low noise margin is:

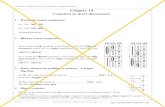

FIGURE 1. Typical Noise Margins for Single End Signal Backplane TechnologiesFigure 1 illustrates noise margins for several backplanetechnologies showing typical VIHL and VOHL performanceand noise margins. As an example, GTLP has a VIL of0.90V and input VOL of 0.65V and the noise margin is

0.35V. A voltage LOW-to-HIGH noise transient would needto rise above 0.90V to place the input in jeopardy of switch-ing states.

NMH = VOH - VIHWhere:NMH = High Noise Margin VoltageVOH = Output High VoltageVIH = Input High Voltage

NML = VOL - VILWhere:NML = Low Noise Margin VoltageVOL = Output Low VoltageVIL = Input Low Voltage

-

3 www.fairchildsemi.com

Noise (Continued)It is notable that noise margins for most technologies aresmaller for the VOL to VIL condition. This makes noise inthe lower voltage portion of the signal range a potentiallymore significant problem that requires tighter control thanis necessary for noise at the upper end of the signal level.Most single-ended technologies have a fixed Voltage Ref-erence level (VREF). For example, CMOS devices typicallyhave a VREF that is 0.5 * VCC (or VCC/2). GTLPs adjustable VREF gives it an additional advantageover most single-ended technologies. The GTLP VREFlevel is typically set between 0.7V and 1.3V and this allowsthe system designer to adjust the device threshold to amaximize noise margin for a specific application.Differential technologies do not have the noise margin con-cerns of single-ended technologies. This is due to commonmode rejection, which is the ability of the input to rejectnoise that appears coincident on both inputs. Although dif-ferential technologies are much better at rejecting inputnoise, they are not immune. Excessive noise is still anissue and can cause severe problems including edgedelays and distortion.

Ground BounceGround bounce of a digital electronic device is a measureof how the on-chip ground levels shift under dynamicswitching conditions. The I/C package leads are seen asinductive elements during dynamic switching. Figure 2illustrates a simplified model of a CMOS device in a pack-age. L1 represents the inductance of the ground lead, L2represents the VCC lead, and L3 the output lead. R1 repre-sents the impedance of the output structure during a dis-charge of the load. CL and RL represent the output load.

FIGURE 2. Package I/C Output Mode

To change the output load from HIGH-to-LOW, currentflows through the output structure to discharge the loadcapacitance. As the current changes, voltage is generated

across the inductances of the circuit. The formula for volt-age across an inductor is:

The inductance (L1) between system ground and internaldevice ground induces a voltage. This induced voltage cre-ates what is known as ground bounce. The voltage causesthe device ground to be at a different level than systemground. This phenomenon appears as a device groundbounce above system ground level, followed by a swingbelow system ground before returning to parity with thesystem ground.This same phenomenon occurs on the VCC rail. This is theinverse of ground bounce and occurs when the devicedrives the load from LOW-to-HIGH. The effects of ground bounce are seen both as outputnoise and as an internal shift of the input threshold regionof the device. Both the output noise and the input thresholdshift of a device can greatly reduce the effective usablenoise margin on the bus. In an extreme case, ground bounce can cause the falsetriggering of the switching device due to its moving internalthreshold. It can also cause false triggering of a receiverdevice due to the output noise generated by the driver. Theresult of this can be unwanted bit errors.Ground bounce is usually specified as VOLP (peak levelabove the device static VOL) and VOLV (valley or lowestvalue of the shift below VOL). Ground bounce phenomenaare affected by several contributing factors: the number ofoutputs switching, output edge rate, the location of the out-put pin, the VCC voltage, the load type and location, andthe device technology.The number of output pins switching in the same directioncoincident with one another will affect the amplitude of theground bounce pulse. Each output can be considered aresistive and inductive path in parallel with other outputs.As the number of output switching increases, the totaleffective resistance goes down. This generates moreground bounce. Sharper output edge rates create a larger induced voltageacross the inductive components in a shorter amount oftime. This results in large amplitude of bounce. The location of the output pin in relation to the ground andVCC pins also affects ground bounce. The farther the out-put pin is from ground, the higher the ground bounce ampli-tude. Because of the bounce phenomenon, devicemanufactures have included a high number of ground andVCC pins on high-drive and high-pin- count technologiesThe VCC voltage value affects the output voltage swing andthe amount of current available. Both of these have a directimpact on ground bounce.Load type and location also have a significant effect onground bounce. A lumped capacitive load is a worst-caseload for generating ground bounce. Conversely, a distrib-uted load reacts as an impedance, and the resulting edgerate generates much lower ground bounce effects.

VL = L (I/t)Where:VL = Generated VoltageL = InductanceI = Change in Currentt = Change in Time

-

www.fairchildsemi.com 4

Noise (Continued)The charging or discharging of a lumped load creates amuch greater change in current flow over time (I/t) thanthe charging or discharging of a distributed load. This factinduces a much greater voltage across the ground or VCClead inductance. Device technology and design play a large role in groundbounce generation. In simple terms, higher output drivedevices generate steeper edge rates, and steeper edgerates generate more bounce. However, there are many mit-igating factors. Technology plays a large role in device edge rate. PureCMOS devices, due to their design and behavior, turn onmore quickly abruptly than equivalent bipolar devices. Thisabrupt delay results in more ground bounce for equivalentdevices. Semiconductor vendors recognize this, anddesign in gradual turn-on (GTO) circuits and edge ratecontrol circuits to slow the edges and minimize bounce.BiCMOS designs combine some of the best features ofbipolar and CMOS, including less bounce than most equiv-alent pure CMOS designs. As mentioned earlier, the inclusion of multiple VCC andground pins helps minimize inductive lead effects. Sometechnologies such as GTLP take this a step further andinclude quiet grounds that separate the circuitry on the dieand further quiet the device.

Dynamic ThresholdDynamic threshold, the result of device ground bounce, isusually specified as Voltage Input Low Threshold Dynamic(VILD) and Voltage Input High Threshold Dynamic (VIHD).As noted in the section on ground bounce, a shift in thedevice ground and VCC also causes a shift in input thresh-old levels. Dynamic threshold problems arise when adynamic input threshold crosses through the static inputthreshold level. This will cause the device to switch gener-ating an unwanted change of state. Dynamic thresholdproblems usually occur only under the most severe circum-stances, for example, when all outputs are switching simul-taneously in the same direction into a lumped load. Adequate grounding and decoupling can eliminate or mini-mize dynamic threshold and ground bounce effects.

System Switching Noise The system power distribution network generates systemnoise. Current and voltage changes on ground and VCCplanes induce most of this noise. These changes are alsoseen on VCC and ground traces and vias. These changesare created by the power demands of devices switchingstate. High-speed and high-drive I/O technologies such as thoseused in backplanes require large amounts of current duringswitching. This is because large loads and high power ter-minations such as Thevenin and DC parallel designsrequire significant amounts of current. If the system powerdistribution network is not adequate for the current load,the voltage level on the supply planes can shift duringswitching. These voltage shifts are easily coupled through-out the system and are seen as voltage transients and ring-ing on the signals. A transient voltage drop to a device VCC also affects devicenoise margins adversely and reduces device output drive.These VCC droops also cause device propagation delay to

step out. As the VCC level droops and recovers, the propa-gation time varies, inducing jitter. A designer has more control over system-generated noisethan over device-generated noise. System layout anddesign directly affect system switching noise levels.

Power DistributionTo minimize the effects of switching noise, adequate low-impedance ground and VCC planes must be used. The lay-out and impedance of local supply traces and vias must besufficient for current requirements. Local supply traces andvias should also be kept as short as possible. To furtherisolate and minimize switching noise, the separation ofground and supply planes for low- and high- speed sec-tions of the system is recommended.

DecouplingLocal decoupling is also critical to eliminating voltagedroops. Decoupling capacitors connected to the VCC ofdevices will significantly reduce VCC transients. Thesecapacitors filter overshoots to ground and supply current todevice VCCs when the VCC line voltage level droops. The required capacitor values will vary with the system fre-quencies and the transients seen on the power planes. Useas many capacitors as needed to ensure adequate systemdecoupling, but a minimum of one decoupling capacitor forevery device VCC pin is recommended. In most applica-tions, two decoupling capacitors are used to cover the fre-quency ranges of transients seen on the power rails. Ifpossible, place the capacitors on the same side of the PCBas the device being decoupled, and minimize lead lengthsbetween the decoupling capacitors and the device powerpin.

Transmission Line ReflectionsTransmission line reflection can be a major source of sys-tem noise. If transmission lines are left unterminated or areimproperly terminated, the voltage level on the line will gen-erate signal reflections, which, in turn, generate voltageovershoots and undershoots on the signal line. On anunterminated line, overshoots and undershoots can con-tinue to propagate up and down the line repeatedly beforesettling to the quiescent voltage level. Terminating transmission lines into their own impedanceeliminates reflections. Section 4 of this BackplaneDesigners Guide covers the subject of transmission linesand termination options.

-

5 www.fairchildsemi.com

JitterJitter is movement of signal edges from their ideal positionin time. This movement can lead or lag the ideal positions,and, as system speeds increase, these edge deviationspresent a significant problem for system signal integrity,causing skew, race conditions, and other timing problems.Jitter is generally classified into three types: cycle-to-cyclejitter, period jitter, and phase jitter. The diagrams in Figure 3

illustrate these types. Cycle-to-cycle jitter is the change inan outputs transition in time in relation to the transition dur-ing the previous cycle. Period jitter is the maximum changein a signal transition from the ideal position in time. Phasejitter, also called long-term jitter, in the maximum change inan output signal transition from its ideal position over manycycles (typically 10 to 20 microseconds).

FIGURE 3. Three Types of Jitter

The causes of jitter are grouped into two general catego-ries: deterministic jitter and random jitter. Deterministic jitteris caused by power supply fluctuations, cross-talk, andduty cycle distortion (e.g., asymmetric rising and fallingedges). Random jitter is caused primarily by device thermalnoise. Although system designers have little control over thecauses of random jitter, they can reduce the effects ofdeterministic jitter by minimizing cross-talk and duty cycledistortion and by ensuring the power network is adequatefor system needs.

-

www.fairchildsemi.com 6

Cross-talk Cross-talk is the capacitive and inductive coupling of sig-nals from one signal line to another. As system perfor-mance and board densities increase, so does the problemof cross-talk. In the case of cross-talk, the line the signal iscoupled from is usually referred to as the active (or aggres-sor) line, and the signal line the signals are coupled onto iscalled the passive (or victim) line. The amplitude of the signal generated on the passive lineis directly related to the edge rate of the signal on theactive line, the proximity of the two lines, and distance thatthe two lines run adjacent to one another. Cross-talk noisecan cause false switching by crossing the thresholdregions of receivers on the passive line. Cross-talk coupling generates two types of effects: forwardcross-talk and reverse cross-talk.

Forward Cross-talkForward cross-talk is defined as the current coupled onto apassive line away from the active line driver, as shown inFigure 4. Forward cross-talk current is the result of capaci-tively coupled current (IC) minus the inductively coupledcurrent (IL): IC - IL. This is due to the inductively coupledcurrent traveling in the direction of the end of the passiveline away from the active line driver (point D in Figure 4).Forward cross-talk coupling occurs during the edge transi-tions on the active line and in opposite polarity. The pulseamplitude is a result of the difference in capacitive andinductive coupling. Due to the short duration and small amplitude of forwardcross-talk, the reflections of reverse cross-talk often hidethis generally small pulse.

Current through the Characteristic Inductance of Transmission Line = ILCapacitively Coupled Current = IC = -C VI/tMutually Induced Current = IM = mILForward Cross-talk Current = ICF = IC IL

FIGURE 4. Illustration of forward cross-talk in a set of transmission lines between the driver and the receiver. As the active signal VI propagates from A to B, a negative spike VF propagates from C to D, coincident with VI.

-

7 www.fairchildsemi.com

Cross-talk (Continued)Reverse Cross-talkReverse cross-talk is defined as the current coupled onto apassive line toward the active line driver, as shown in Fig-ure 5. Reverse cross-talk current is the result of capaci-tively coupled current (IC) plus the inductively coupled

current (IL): IC + IL. This is due to the inductive couplingresulting in a transformer action. Reverse cross-talk is directly proportional to line length andvelocity of propagation on the line. Reverse cross-talkincreases linearly with distance up to a certain length. Thislength is the distance that the signal can travel during itsrise or fall time.

Current through the Characteristic Inductance of Transmission Line = ILCapacitively Coupled Current = IC = -C VI/tMutually Induced Current = IM = mILReverse Cross-talk Current = ICR = IC + IL

FIGURE 5. Reverse cross-talk in a set of transmission lines between the driver and the receiver. For reverse cross-talk, the active signal VI propagates from A to B,

while a positive pulse appears at C for a duration twice the coupled line delay T.

As illustrated in Figure 5, reverse cross-talk coupling startsat point C simultaneously with the beginning of the transi-tion at point A. This coupling continues for the duration thatthe active line is switching. As the signal propagates downthe active line to point B (tB), the signal is coupled onto thepassive line and toward point C. The reverse cross-talkthen requires another flight time to reach point C. Thismakes the total reverse cross-talk waveform on the pas-sive line twice the distance of the active line or tC = 2tB.Depending on the termination of the passive line, a reflec-tion can be generated from the reverse cross-talk, and thisreflection will propagate to D and, depending upon theamplitude and duration, back to C.

Minimizing Cross-talkThe use of tight geometry in most systems can reducecross-talk significantly although it cannot eliminate itentirely. Some preventative design measures can be rec-ommended to minimize cross-talk. Use maximum allowable spacing between signal lines. Minimize spacing between signal and ground lines. Isolate clocks and other critical signals from other lines

(larger line spacing is recommended) or isolate withground traces.

In backplane or wire-wrap applications, use twisted pairfor sensitive applications such as clocks and asynchro-nous set or clear functions.When using ribbon or flat cable, make every other line aground line.

Terminate signal lines into their characteristic imped-ance.

-

www.fairchildsemi.com 8

SkewSkew is the variation of propagation delay differencesbetween output signals. Minimizing output skew is a keydesign criterion in todays high-speed clocked systems.Excessive skew, especially for clock signals, can causerace conditions and other timing errors that result in systemdata faults. At the very least, poor skew will force a slowermaximum system speed, and this, in turn, will limit systemperformance.

Matching trace lengths, trace impedances, and line loadingwill minimize system skew. Clock driving and I/O technol-ogy will also play a significant role in overall system skew. Fairchild Semiconductor has developed skew specifica-tions for interface devices. This section provides an over-view of skew types, their definitions, and examples, asshown in Figure 6. Without skew specifications, a designermust approximate timing uncertainties. Skew specificationshave been created to help clock designers define outputpropagation delay differences within a given device andduty cycle.

FIGURE 6. Clock driver showing output skew. If a signal appears at output #1 in 3ns and at output #5 in 4ns, the skew is 1ns.

Sources of Clock Skew Total system clock skew includes intrinsic and extrinsicskew. Intrinsic skew is defined as the differences in delaysbetween the outputs of devices. Extrinsic skew is definedas the differences in trace delays and loading conditions. Ifthe trace delays are poorly matched the result will be anincrease in signal-to-signal skew. A 50 MHz clock signal distribution on a PC board is givenas an illustration of intrinsic and extrinsic skew. A frequencyof 50 MHz with a 50% duty cycle produces 20ns clockcycles.Total system skew budget = 10% of clock cycle = 2nsIf extrinsic skew = 1nsDevice skew (intrinsic skew) must be less than 1ns

Clock Duty CycleClock duty cycle is a measure of the amount of time a sig-nal is HIGH or LOW in a given clock cycle. Clock skewaffects the duty cycle of a signal (duty cycle = tHIGH/tLOW * 100%). As an example, in many systems, tHIGH andtLOW are each 50% of the clock cycle; therefore, the clocksignal has a duty cycle of 50/50%. To ensure this require-ment, skew must be guaranteed less than 1ns at 50 MHz toachieve 55/45% duty cycle requirements of core silicon.

Common Edge Skew (tOSLH, tOSHL)Device output skew is usually specified as output skew forHIGH-to-LOW transitions (tOSHL) and output skew forLOW-to-HIGH transitions (tOSLH). These parameters

describe the delay from one driver to another on the samechip. This specification is the worst-case number of thedelta between the fastest to the slowest path on the samechip. An example of this critical parameter is the case ofthe cache controller and the CPU, where both units use thesame transition of the clock. In order for the CPU and thecontroller to be synchronized, tOSLH and tOSHL need to beminimized.The output edge skew specifications are calculated by sub-tracting the specified propagation minimum (tPMIN) from thepropagation maximum (tPMAX). Propagation delays aremeasured across all outputs of any single device.Definition:

tOSHL = | tPHLMAX tPHLMIN |Time of output edge skew edge HIGH-to-LOW = Time ofpropagation HIGH-to-LOW minimum minus time of prop-agation HIGH-to-LOW maximum

tOSLH = | tPLHMAX tPLHMIN |Time of output edge skew edge LOW-to-HIGH = Time ofpropagation LOW-to-HIGH minimum minus time of prop-agation LOW-to-HIGH maximum

Pin Skew or Transition SkewPin Skew or Transition Skew (tPS) describes opposite edgeskews, i.e., the difference between the delay of the LOW-to-HIGH transition and the HIGH-to-LOW transition on thesame pin.

-

9 www.fairchildsemi.com

Skew (Continued)Pin Skew is measured across all the outputs (drivers) onthe same device. The worst (largest delta) number is theguaranteed specification. Ideally, this number should be0ns. Effectively, 0ns means that there is no degradation ofthe input signals duty cycle.Many of todays microprocessors require a minimum of a45/55% duty cycle. System clock designers typicallyachieve this in one of two ways. The first method is with acrystal oscillator that meets the 45/55% duty cycle require-ment. The second approach is to use a less expensivecrystal oscillator and implement a divide-by-two function.Some microprocessors have addressed this by internallyperforming the divide-by-two.Since duty cycle is defined as a percentage, the room forerror becomes tighter as the system clock frequencyincreases. For example, in a 25 MHz system clock with a45/55% duty cycle requirement, tPS cannot exceed a maxi-mum of 4ns (tPLH of 18ns and tPLH of 22ns) and still meetthe duty cycle requirement. However, for a 50 MHz systemclock with a 45/55% duty cycle requirement, tPS cannotexceed a maximum of 2ns (tPLH of 9ns and tPHL of 11ns)and still meet the duty cycle requirement. This analysisassumes a perfect 50/50% duty cycle input signal.Definition:

tPS = | tPHL tPLH |Pin Skew or Transition Skew = Time pin HIGH-to-LOWminus time pin LOW-to-HIGH

Both HIGH-to-LOW and LOW-to-HIGH propagation delaysare measured at each output pin across the given device.For example, a 33 MHz, 50/50% duty cycle input signalwould be degraded by 2.6% due to a tPS = 0.8ns (Note:Output symmetry degradation also depends on input dutycycle).

Opposite Edge SkewOpposite Edge Skew (tOST) defines the difference betweenthe fastest and the slowest of both transitions within agiven device. Given a specific system with two compo-nents, one being positive-edge triggered and one beingnegative-edge triggered, tOST helps to calculate therequired delay elements if synchronization of the positive-and negative-clock edges is required.Definition:

tOST = | tP(m) tP(n) |Opposite edge skew = Time output pin m minus timeoutput pin n

Where:Any edge transition (HIGH-to-LOW and LOW-to-HIGH)measured between any two outputs (m or n) within anygiven device.

Part Variation Skew or Part-to-Part SkewPart Variation or Part-to-Part skew (tPV) defines the distri-bution of propagation delays between the outputs of anytwo devices. Part-to-part skew (tPV) becomes a criticalparameter as the driving scheme becomes more compli-cated. This usually applies to higher-end systems that gofrom single clock drivers to distributed clock trees in orderto increase fan out. In a distributed clock tree, part-to-partskew between clock drivers must be minimized to optimizesystem clock frequency. In the case of a clock tree in Fig-

ure 7, the total skew becomes a function of tOSLH/HL of U1plus tPV of U2 and U3.

FIGURE 7. A Clock Distribution Tree

Case 1: Single Clock DriverTotal Skew = common edge skew U1

= tOSLH or tOSHL of U1Case 2: Distributed Clock Tree

Total skew (U2, U3) = common edge skew (U1)+ part-to-part skew (U2, U3)= tOSLH or tOSHL of U1 of U2 and U3

Definition:tPV = | t Pu,v + t Px,y |tPV = common edge skew of driver plus

part-to-part skew of all driversWhere: tPV is any edge transition (HIGH-to-

LOW or LOW-to-HIGH) measured from the outputs of any two devices.

-

www.fairchildsemi.com 10

Electromagnetic InterferenceElectromagnetic Interference (EMI) consists of anyunwanted spurious, conducted and/or radiated signals ofelectrical origin that can cause interference and degrada-tion of system performance. This interference can result indata errors and system faults and can cause problems inline-to-line connections, inside the actual system, outsideon the systems cables, or in other nearby systems.EMI is directly related to system layout and noise level.EMI radiation sources include ICs, cables, connectors, andtraces. Overall board and system layout have a significanteffect on EMI radiation. Current flowing in a path within thesystem generates EMI. These paths can be VCC to groundplane loops or transmission lines. The current pulses cre-ate magnetic field energy, while the voltage drop across theloop creates electric field energy. The current path materialitself acts as an antenna either transmitting or receivingboth magnetic and electrical fields. EMI generation is a function of several major factors: signalfrequency, duty cycle, edge rate, and output voltage swing.Current spikes, power line noise, and output ringing alsocontribute to overall EMI radiation. In addition to the signalcomponents, circuit radiating area and the resultantantenna radiating efficiency also play an important role inEMI radiation.

Calculating Maximum Electric FieldAs noted, system EMI is in large part a function of currentloop area. Typically the largest loop areas in a system con-sist of backplane transmission lines and I/O cables. TheVCC to ground current loops on ICs are small in compari-son to the current loops in transmission lines and power toground plane loops. The formula for modeling the maximum electric field is:

EMI Design ConsiderationsDesigning a system with low EMI is critical to reliable sys-tem operation. Additionally, national and international

agencies regulate and test systems for maximum allowablelevels of EMI. The task of designing a low EMI radiationsystem is involved and covers almost every aspect of sys-tem operation and layout. To ensure low EMI radiation: Design a transmission line with the lowest possible

impedance to reduce the antenna effect. Long transmis-sion lines, such as those in clock-driver or bus-interfacecircuits, should be laid out in intermediate PCB layersrather than surface layers.

Use multilayer PCB boards that include full ground andpower planes. This provides impedances several ordersof magnitude lower than power and ground traces andreduces transient voltage drops in power distribution andreturn loops.

Use PCB shielding. Laying out transmission linesbetween PCB VCC and GND planes reduces character-istic impedance and horizontal polarization throughshielding with PCB copper planes. The metal stiffenersat the PCB edges shield against horizontal polarization.

Match the impedance of the drivers and the transmis-sion lines. Radiated emissions are high when transmit-ted signals exhibit overshoot, undershoot, and ringing.To minimize these effects, maintain careful impedancematches between drivers and transmission lines andbetween transmission lines and receivers.

Terminate transmission lines to reduce or eliminate ring-ing and reflections.

Minimize the number of simultaneously switching out-puts to moderate current pulse amplitude and outputringing.

Eliminate or minimize cross-talk. Ensure that the power supply network can supply suffi-

cient current under all operating conditions, that it is lowimpedance, and that it has adequate decoupling to sup-press power supply switching noise.

SummaryThe key to designing for high signal integrity is the reduc-tion of noise and interference phenomena below levels thatwill adversely affect signal quality. System interferenceincludes switching noise, cross-talk, jitter, skew, and elec-tromagnetic interference (EMI). All electronic systems contain some elements of interfer-ence. Knowing the causes of noise and interference leadsto an understanding of how they hinder performance andreliability as well as how they can be minimized or elimi-nated. The goal is to reduce noise below operational interferencelevels. The level of signal integrity required will be differentfor every system type. Cost, function, and operating speedall play a part in the amount of noise that can be in toler-ated in a design.

|E| Max =1.32 x 10 - 3 I A f2 [1 + ( D)2] V

D 2 mWhere

|E |Max = Maximum E-Field in the Plane of the LoopI = Current Amplitude in Milliamps

A = Antenna Area in Square cm = Wavelength at the Frequency of InterestD = Observation Distance in Metersf = Frequency in MHz

and the Loop Perimeter (P) is much less than the Wavelength ()

-

11 www.fairchildsemi.com

Section 6 - N

oise

, Cro

ss

-talk, Jitte

r, Skew

, a

nd EM

I Backpla

ne

Designer

s G

uide

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied andFairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORTDEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILDSEMICONDUCTOR CORPORATION. As used herein:1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to theuser.

2. A critical component in any component of a life supportdevice or system whose failure to perform can be rea-sonably expected to cause the failure of the life supportdevice or system, or to affect its safety or effectiveness.

www.fairchildsemi.com