A VoltagA Monitoring DiwicA -...

Transcript of A VoltagA Monitoring DiwicA -...

A VoltagA Monitoring DiwicA

by

David R, L''!Wis

SubmittPd in Partial Fulfill�Pnt of thA RP.quirAmP-nts for thP.

DAgl'.'PP of BachAlor of SciPnCP

at thP

MassachusPtts InstitutP ,-,f TAchnology

,July, 1979

SignaturP of Author DPpartmPnt nf Physics, 15 July, 1979

•• �:-•• ':1: : •• � � •• · ••••...••••••••••••••.•••••••••••••/"

Th Psis s11pPrvisor

................ �.(\.. .. � ..................... . Chairrnan, DApartrnr-rntal C0T"J11i ttPP. on ThASPS

)

................... ·-

FERMILAB-BACHELORS-1979-01

~\ \

I would lib~ to thank Prof,cissor Irwin PlPss fnr his support and

advicP, S,-:,ng Oh, my co-wnrkf>!· in this prnjP.ct, anrl Wayw=1 Hagman from

thP DApartJ'11=rnt of t;;lP.ctricel -C:nginP.P.ring for supplying MP. ·with thP

tr>chnical mannals ad for fmniliarizinrr 1'1""' with TTL anti CJ'.'OS

coJ11ponPnts,

(2)

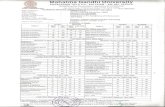

Ti tl~ Page ....... , .................. , ............. , ......... . 1

t e t t I l t .. I e t e t e t e • t t t ii t I t • I I I t I t I. I f I t t I I t t t I t • 2

TablP. of Contnnts ............................................ 3

Introduction ................................................. 4

SpAcifications .............................................. 6

DAsign •....• , ••••.••..••..•.•......... , ...........••••• s •••• 9·

I t t t I t t t t ._ t t t t f f t I t t I t I I t t t t t t I t t • I t I C I t • t t t I t t, a 27

Summary .............. t .................... t •••••••••••••••••• 30

App.mdix I (SchAmatic) ••••••••••••••••••••••••••••••••••••s• 31

AppAnnix II (Pin Configurations) .............................. 33

FigurAs:

Figure 1 .... . . . . . ... I I- • I 7 FigurA 2 I • I • ... . . . . . . . . . 10 FigurP 3 . . .. . .... . . . . . 11 FigurP 4 .. . . . . . . .. . . . . 12 Figure 5 t • ' • . . . . . . . . . . . . 13 FigurA 6 . . ... . .. . . . . . . . . 13 FigurP. 7 .. . . . . . . . . . . . . . . 14 'FigurP 8 .. . . . . . . . . . . . . . . 15 Figuro 9 .. . . . . . . . . . . . . . . 16 FigurP. 10 .. . . . . . . . . . ~ ... 17 FigurA 11 ... . . . . .. . . . . 19 FigurA 12 .. . . . . . . . . . . .. . . 20 FigurA 13 .... . . . . . . . . . . . 20 Figuro 14 ... . . . . . . . . . . . . 21 Figuro 15 ... . . . . . .. . . . . . . 21 FigurA 16 ... • • t • . . . . . . . . 22 FigurA 17 .... . . . . . . . . . 23 FigurA H3 ... . . . . . . . . . 24 FigurA 19 ... .. . . . . . . . . . . . 25 FignrA 20 ... . . . . . . . . . . . 26 Figure 21 .. . . . t • ~ .. . . . . . . 28

(3) 1;,7i!W·~ 7,P;f.~ - . ,

-;:c,

..... ,,-.1

'~ .• ,.,.,,,, ••. , -~ ~-'. ·:.: •'.!1 ,-, /,

Introouction

This voltagA monitoring dPvicA was ,i,:,signNi and constructPrl for

thP AFC group fnr USP in a SAriPs of P.Xp,=i:rimP.nts to bP. conrlnctP.d at

thP FA:rrd laboratory, ThASP PXpPrimn.nts will utilizA a 30" hybrid

proportional wirP chambArs (Plj/C) 1 a fast pa:rticlA irlAntifiAr (CRISIS)

0utgoin?: track t0 six mPtPrs, incrPasinl! thP acc,1:racy in path

ThA construction of th.-, voltag"' mrrnitor was motivat.,.rJ by thP. USP of

thP FGD. ThA FGD consists of a conv..,rtP:r, a VArtAX locator anrl an

absnrbPr, A ~ E=mtArs tbr-> conVPJ"tAr, fnu:r :rarliation lP.ngths of Pb

glass, and is convArtAd into a show"'r of A I s I fi' s and '(• s. ThA

Cn,:rn,nkov radiation produc"'<l by thA P. • s anri p°' s is rlAt"lctAd by a.n array

nf photo multipliAr tubP,s (PH), AftA:r thA convA:rtP.:r showP.:r is n"'lar

its maximum sizA it pass As through thP. VP:rtPX locator and into thA

inva:r:i.11.ncA nf th A Pl" tubPS' supplv v11l tarrAs rAs111t"'rl in th 0 c0n-

strnctinn nf thA vnltafP mnnit0r, r.lPca11s"' 0f th,-, largP. numb,.,r nf

vnlta.gn,s tn Tl"nnitor, it was not P.Connrnically fpasiblP. to buy a

commPrcial dAvicP fnr this function.

~ihile the dPvice was still in thp planning stage. it was decided

to expand its capability to 511 channels to accomodate any other

voltages that Might require monitoring,

The following are thP specifications.

(5)

.-

C "f' t' 1 ... i~ci. 1ca_10ns

ThP systAM will monitor np to 511 cnannAls with channPl ZA:ro

lAft unusPd, Bach channAl will monitor PithPr polarity. ThA systPm

will sound an alarm if thA voltagA monitorAd changAs by morP than

ThA input impP.dancP of thA systAM is 200 K~land thA input voltagA

for all channAls is±. 5v, Any usPrs with high voltagA sourcP.s should

stPp down his or hAr vol tag A to this valuP. (SP.0 fif; l 1 for rAcom-

mr.in<lAd circuit.) ThP USPrs' stPp rfown rPsistnr chains should nnt

drift mo.rP than 1/,. rrh,, rl,.,s:i rwl currP.nt to thP systPrn is :i.pprox-

ThP input im~d ancA tn th A Analog tn Digital ConvArtAr is 1 F J'L.

This is obtainPd by a buffpr systP~ bPforA thP ADC. '!'hA output of

thP ADC is Pight bit and 5v, will corrAspond to 200 binary. A 2~

changA in a monitorA<l voltRfP corrPsponds to a changP of four lPast

c0unts.

ThrAP modAs of opPration will bP. incorporatPd and consist of:

a. An initialization modP which will run onA full cyclA

(all 51.1 channAls )and rP.ad thA voltagAs to bP monitorAo

into mAmory, ThPSP. voltarAs a.rP. nrAsumPd to bP. corrAct

and will bP. nsAr! for all f11rth"'r comparisons. 8K of'

ranclam acc0ss m0morv (RAY) i.s 11sr>rl, This !'1nrl"' is cnntrolli:<l

by· a g1rnrrl"'rl switch to pr"'v"'nt. lat,,r. rlP.structinn of

rPcorrlPcl vnlur>s. ( 6)

1 l". ~] A.hy, D, Lnwi0 .i'c S, Oh, "SpPcifications of a Voltai:r"' Ynnitnring Dr>v.ioP," APC V.ng:i.nPnri.nr: Not"' 79-1, (F'Pb, 28, 1979)

b, A run morlP., which is continuous full cyclA monitoring.

This modA is intArruptA<i wh"'n a dAviation bP.tWAP.n thP.

monitorPd an<l rAcordA<l valuA AXCP.P.ds four lAast counts.

~·ihAn this occurs I an audio ann a visual alarm arA triggerA!i

and a display will rPad out:

i) sign bit

ii) scalA<i rPcordA<l voltagA

iii) sca.l"'d monitorAd voltaP'"'

iv) ch1mn"'l nuMbAr

c, A manual Mod A tl-iA.t a.llows singlA channP.l monitoring and

s:i.n~r,ln chnnn<>l cnrrP.ctil"lnS to rAcorrlAr'! valuPs in m"'rnn~r.

CorrActions to mm'lory must bP dnnP in thP manna1 rnndA so

nnly that channA1 is chanp:P.rl, ThArP a.rA two channAl

incrAmPnting switchAs, nnP. that advancAs channPls at a

ratA of 20 pAr SP.cond, and onA that incrPmAnts singly,

ThP.rR is also a channAl cnrrPct switch,

Th0 run mo<iA and initialization mod A opP.ratA at a minimum of 50 f'-5 pAr cha.nnPl, 26 ms minimum full opPrating cyclA, ThA actual

opAra.ting ratA is 2 ms pAr channAl.

ThArA is a rAmotA display and an alam in th,=, control romn,

AdjustmPnts hoWP.VP.r, can only b,=, marl"' at thP Main nann,=,l,

ThA systPm rPquirPs four onP.:rating vo1tar! 0 s, .1-5, -5, J..1_5 Anrl -15

volts. Th"' ry,wpr rlissinat.-hn ·is <1nn:rnxi_m,qtPl:V 500MW,

1".ach ch,'l!'lnPl is protPctPd by <!forlPs lir1iti11i:; thP input vnlta!,:P tn

+ 6 v. Lip.ht Al"li tting rlil)rlPs (LT~D) inrlicat<> imnropPr voltagAs.

(8)

A compL=itA schAmatic of thP. systP.m is inclndP.d as AopAndix I. ThA

first componAnt of thA dP.sign consistPrl of thA multiplAXAr. CVOS

componAnts WArA used sincP. thP.y allow dirP.ct transmission of analog

signals, bAing voltagP. controlJ.Ad dP.vicPs rathAr than curri:mt

controllAd dAvicP.s as arP TTL componPnts. Sincn thA volta~Ps to bA

monitorAd WArA not dAtArminatA, it was dAcicfad that thA voltagA stP.p

down to mPAt intArnal rP.quirPm""nts should b"' AX:tArnal to th"' systP.m.

F SP.rs would thfm b"' l"Aquir,v'l m stPp clown th Air own vol tag""s taking: into

account thP intPrnal imoP.dancP and s"'nd th"' systAm ~ 5 volts as

mAntionP.<1 in thP spPcifications. Th"' 1JsPr is thnn r 0 sprmsiblP. for

kAAPing track of his or hAr own scalini::r factor, ThP ~ 5 volt inuut

was thP.n stP.ppAd down intArnall:v to f- 2 v0lts w'hich corrPsponn"'rl to

an out put fro'f'11 th A ADC of 200 binary. 1 ;s, ¾ W rPsisto rs ,,u~r,::,, us Pd for

thA intArnal rAsistor chains. ThA int<>rnal rPsistor chains W<>rP

protP.ctAn by two dioclP.S pAggAd to thP voltagA limits and oVArloads trig-

gArP.d an L"S0, B'VAry 18 channP.ls wArA ti"',i togAthnr by thA diodP

protP.ctinn linPs, and thASP. linP.s wrmt to two Op-amps to AnsurA

sufficiimt current to rAn<lAr th"l LBD's visiblA. (S1=H~ fig. 2 and fig. 3)

ThA Op-amn will saturatA at approximatPly 2mV, ThA 1 K-'L rPsisto-r

AnsnrPd that thA curr,mt was sufficiAnt to drop this. ThP rliodPs

11sAd, U'.914' s, had a suffici 0 ntly ro1Jn,.,,,,, :t~iri.nf" mint to allow

t:-iis currAnt whAn thAy WArA forward bias,,,, i""l PXCPSS of .2 vnlts.

(9)

SAtting thA limiting voltagns at± 2,3 volts thAn pAgs thA intArnally

stAp:!)Ad rfown voltagn to ± 2. 5 volts and trigf;Ars thA um whAn thA

input voltagA AXCAAds 6.5 volts,

",~

.,..i

ito kJl. r 2.0 w...

r .• , .. 1 -1 6 ,_,_ l

"· -:- l ·-------· ----

-z,3"

(fig. 2)

(10) ·

2

(fig, 3)

ThA voltagp,s WArA rnnltinlAXAd usirw 32 CD 4067's, Ct"OS 16 to 1

mu.ltiplAXArs, anrl two CD 451.5's, 4 to 16 lin<> (1PC01Prs. ThP fact that

both positive an<l nPgativA voltagPs WPrP b,,,inR: transmitt"'d rAquirRd

thASP CHOS componAnts to bP. opAratP.d at +5 volts VDD and -5 volts VSS,

to l"lAAt thA opArating rAquirPwmts VDD >, V~ ), VSS anrl VDD. - VSS ~ 15v.

~ach of thA 32 CD l~067' s multiplAXAd 16 channPls an<l was onPratAo by

thP four loWASt bits of thA 9 bit addrASS. ThP, two 4-515' s WArP

to rmablP,

'l'hA outnnt of thP multinlPXPrs w11.s th<>n s,::,;1t to a cmrroarator tn

tP.st whPth"'r it was positivP or DA£UttivA, ~hA nutnut nf' thP cmnnarator

CD 4066, Q11ad Analog Switch, thA path for n<>e-ativP signals passing

through an inw~rt,er, ThP signal was buffnr-"d bPforP rAachinr: thn ADC

by an op-amp in a unity gain configuration,

( 11) 2'l'h"' LinPar IntPgratPd Circuits Data book, 'l'Axas Instri_UYIAnts 1976, p, 5-1.5,

Th8 choicP. of rAsistors 11sAd in thq invqrt<>r was dAtArminAd by thP.

frAqUAncy r,:,quir0rn..,,nts for 500 ens, 3

Vo V,

I .;.~ v,5" l I

VJS1,

I I I \:,-\ '{ b,h.

(fig, 4)

( 12) 3LinRar Int<>~ratArl Circuits lRta J0nk, Yairc~~l 4 ~Pmicnn~uctnr, 1976,

?• 12-~c3_5 ff.

i Sclw-d.. (}~\~ .

I""'\i,-\ lt) A. B c.. l) S.. :o > cJ \ ~~ "1

~---,-.~-----h--

" () 0 0 (:, s,

CJ n C) 0 I s..z.

0 0 0 l 0 S.:?,

0 0 0 I I S'-1

c;> 0 I 0 0 .:::.s-

0 () I 0 I s. !,

0 () I I 0 ':.7

0 0 I I I ss 0 l 0 0 0 s, 0 I 0 0 I -S,o

0 I {) I n S11

() I 0 i I s,z

0 I i 0 0 s.13

('.) I I 0 l SJ't

0 I I ( 0 s1!:

0 I I I I >I(.

X. I X jo.11~,,.1

l 1 }( )( ' _J '

' '

- I .j. L ) r A ' • " . S--1eckJ.. I LV\\..;,;,q i:: rt i B I c .., c .. k,.,1\~ ..

-· -f I . • \

~.--.. __ _Q ____________ o ___ + __ Q ____ ..... o .......... P .... ----;--------. C) , ___ Q_,<L~ __ __Q \ ; 2_ ··---------

0 • 3

-_; -=~~==r~==t==~+~ =-. ________ o_ _ ~-Q__ __ L..... . ... Q ____ ,.__L ____ -1, _____ --... _____ o __________ O _______ L _____ .. L....... JL ______ 7 ______ _

"- . 8

·--=--=~_;~=~-~-=~--~ -·----~-~-~=~-~~= ~~Q~~-=- q --. --... O ........ ---_ _L_ __Q ___ __Q__ .__ _ _\__ ___ ~ I 0

o ( 0 I __ _:___o ___ tt ______ _

· o --,-- ac.. ... --1-. ........!.l_-1--'--+--'-1. ___ _ --·--·--·- I I O O \ 3, ____ Q (:) /!/

0

0 0 0 I I I l If.

(13)

ThP. CD 4515 has a 4 bit strnbAd latch input, · allowini:: changPs whAn thA strobP. input is hi. gh, In this systAm, tho strobP. is h"'ln high.

(fiP:. 5)

(fig. 6)

ThP output fr0Jr1 th"' ADC was 10 bits f 11ll scalP.o against 10 v.

Th 0 2 v. ADC input thArPforP. corrP.sponriP:-1 tn 200 binary, and only

th"' first R bits WP.:r'P. 11sA0 from th"' ADC. '.'hP output frnm th0 ADC was

5 v0lts high anri O volts low, Sincn it was latPr nPCPssarv tn

th<> output nnchanp;P.0 A.Wl OPPra.tP +,ho )"' 0 J"'ai>"Jing cvns componPnts at +5

:m--1 0 vol ts.

V<>rt 0 rl alsn arldrASSP.n Pig ht 1K X 1 bit -q_p::_' s. :>incP thA CD 451. 5' s anri

(;') 4067' s .'J!'P opP.rA.tPrl at +- 5 volts tn aCC0!'"'"l-latP. bnth innut polaritiAs,

it is nACPSsar.v to convPrt thP +5 vnlt a!'ld O volt a.rklrPss b"'forP it is

8"'nt to thP. m111tiplPXin1; cnrnponPnts, Th 0 a::l~!'PSS is sr-mt tn an array

nf on-arms acting as cornx1.rators ae-ainst 2,5 volts. Th"' outnut of

th.., coMPR.rators is + Vsat,, _:t 15 volts, a>-J-l this is stP.pPPrl down by

a !'Psistor chai.n tn + 5 volts, Th"' an:-Jr 0 ss lin<>s to thP RAYs arA

,._ I\

(fig, 7) lJ,

Th"' .sl"'w ratA of thP Op-aT11ps is , 7 ,As f,.y. · This !'PquirAs approx-

(14)

.iJi n°11r IntP;rratPrl Ci:rc11i ts D.!ltr-i ?nnk, ?qi rchili 3Prnicnnrinctnr, 1976, p. \;;>-85 ff.

Al '¾ l\s A, I\, Ai KAM (,) cs

\) Q __ j-'vE

( fip;. 8)

Ti:nablA (W~) arA low, Data is J"Parl n11t i.r''";. 0 !: CS is low anri ~,J"' is high.

il'1pAdancP statP dnring CS high, As shn1''1'1 in fi;,mr,,, 8 ab(WP, Pach

R.aP1 contains onP. of thP Pir:ht data bits f0r 0 ach arldrP.ss, ThP 10th

a.rklrP.ss bit, not shown, is hAld lnw, Fig--,1rP 9 shows thP inb'lrconnAction

bAtWP.Fm thP countAr, ADC and RA}'s in th"' writ"'! mociA,

· ThA clock pulsP. to thA countAr. ir1crAr:"'r.ts thA channAl and

multiplPX<'>S a nPw voltagA to thP. A~C. Th"' clock nulsA also goPS to a

CD 4047, a 1,1onostablP/ AstablP r-iultivibrat0r, 'JS<>11 in this instancP. in

<'>!Jf'"P of thA clock nulsA, This ciPlay"lrl D11ls,., starts thP ADC cnnVArsirrn

stabl'izA, (This takAs into accmmt t1,.P slcw rat"' of thA 0n-a111ns,)

( 15)

v.... . I.'

M u., .. :n f'L,=:.x E.~ 'i,.'\"""' ,A~~ ,t ~

.:5_:;0V. +., ±sv. c;c,><,t~l':s.u:H\ -~

I I l ~1 I I h~ li"'1i

11111111? A < : ~-· i :,:a:ts:~

!I I I I If I I ~r,,.,.,__t ., .. J)

~-\\.~/ t,,? .. ~ c... ·tr - fo Ml I ,Jmc;, ----'- ¢ c.t> 4/QJ..io --...,/ -·h, RAM SC

-· ti'\~'1.t....(, 0 ,,

.t;;.,.\\."'.l~ er b,t ....1.U;;ss <f b,t eu:.Ut<S'.,. II i t I I I I I ! I I t I ' I I I

-~ ~Al-'\ (1) cs - . " e LI;.-,,;"' c,l a -J),

SL + t ~1.,. C.i> /1() 'i) o.t _, __

fu~cr~~l. <:n\

~\\.~ e.J.i . (fig. 9)

vihPn tho. Start CnnvPrt (SC) immt nf th"' ADC !"Acir.>vps thP :rising

Tho Data ;(Rnrly (DR) ontput is tiAd to thP. CS' s of thA RAl'-"s, and its

transition to high allows thA Fu\I'i: mPmory adrlrAss to chanp.:B. ThA ADC

:)it rAturns l()·w, ThR DH signal also goPs ti) a sAcnnr! monostablA,

-Th"" transiti0n of DH tn a lnw nntrntt thPrAf,,y,o rnils"'s thP ~-1"' :lrmuts

(16)

In the normal opArating mociA, thA sAcond !"'onostablP. is disconnPctP.d

and WE is hPld high, kAAping thP. RJ\J''s in a r"larl modA.

l<:- I Ms-··-'}1<--- \,....,,--> I

r _________ ..J L_. __ J _J ,~ sW.1<<·~1

-tS-De.lc,..rJ.. \".._\s<. -lo SC. 0-----· --. _____ I I __ _ I

:::t~(.($ . .-·+s - ,--'-i>R hc:.J.. {-o c.:s 0----- l

+s--l)e\o.y~ r,Jsc. -\o luE. (wt-1k l"\k enl7)*

0 _ _I

4'·iS'\i,,>~> -----lJ,-----.

( f'" _lg, 11))

rPquirPTriAnt of onA SP.conrl to chr->ck all channPls giVAS 2 ms. pAr channAl.

This allows hugA margins. OPP.ration on a nAW channAl commAncAs on thA

falling engA of ¢, 50/1...s for thA start c,..,nv,::,rt pulsA width would hav,=,

bP.An sufficirmt to accomorlatA thP. op-a)')'DS' slpw ratP. 500 JtS havA

been allocated, The convArsion timA is ind 0 rnmdAnt of thA circuitry •

• 5 j'-s would have sufficAd for thA wri tP n·1ls"). 150 ,µs have bm:.n

allocat<=>O t an,'1 1300 f'S 8T'P. still lPft nV 0 :t', fn,::, 0°layAO TI1l1SP Widths

Tw = 2,L1,8 RC, For Tw = 500f'-s, R = 1()0 Ll. anrl C = 2000 nf.5 Fhr

(17) 5 cos/:r·,OS Int<'lgratAo Circuits, RCA Corn,, 1974, n. 235

Tw = 150 µ.s, R= JO Kl an<l C = 2000 pf.

vJhfm thA circuit is in thP. nr)rmal onPratinG T'lOdP (wi;; hP.ld high),

thP output from thA ADC anrl thA ontymt fr0,.,.., thA ftAN is subtractPri

and comparP.('I with binary 3, thrAP. lAast c01E,ts, If th<> rPmainn<>r is

l<>ss than or Aqual to thrAP lAast counts, t½P n"'xt clnck nuls"' is

Rnabhid, If thP. rAmaindAr P.XCAP.'1S thr"'n l<=>ast counts, thP- following

clock pulsAs are inhibitPrl, ThA subtraction anrl comoa:rison involVPS

four CD 406J's (4 bit comparators), two CJ lJ.030's (Qmld AXclnsiv<>

or gat<>s), two CD L~008's (4 bit full aridPrs), and r:d!!;ht CD 4o66's

( Quad swi tch.os). Two CD 4063 's ancl th A Right CD 4066' s a.rA us<>d

to rlPtPrminA which of thA two 8 bit n11r0 b..,rs is largAr and loan the

largPr numbP.r into thP. X inputs of th0. Z-'! s,1btracting circuit to

a.voin nega.tivA valuAs, SAA figurA 11, T'.1° Y. input, (the sr1allAr

rrnrnbAr) is th1m complPr~PntAd by thA r,xcl11siv.., nr gatPs. This

complP.mfmt is th An arlnrvl to th,., X inp~.lt ,d t:: 1 car.ri..,d in to thP

lowAst bit, ThA opAration is thPr 0 fnrP Y i- X + 1 which is PquivalPnt

to X - y if X) y, 'tJhich WA haVP. Ansur 0 -i b:.r +.:1° loaning sch<>'fllP t SPA

figurP.s 12 and 13,

ThA output of thP. full arln..,r, X - Y, is th.Rn cnT11parAd. to thA

thrP.A lAast counts by two CD 4o6J's. Tho c0rrinarator has thrAA

ontpnts, X-Y l.. thrAA lAast counts, X - Y = th:r-0 .-, lPast counts, and

;{ - Y ) thrPA lnast counts, 'ThA first tw0 1:-,11t':.luts ar"' run through

an O :{ gatP. rArlttcing thA l()gical outn11ts t.0 X. - Y !:.. thrAA- lAast counts

or X - Y) thrPP lAAst co1mt.s.

( 18)

'(, Vi. ~ V l(, ·~ l )(3 t ! I

A A B

r C,

0

I ·-----

Q I

I .

Subtractor

(fip;. 12)

t Q

0 0

l \

0 I ~---.......--- -··..,.._-.~-- -·---

I

'fr 0

·-Yi,

(fig, 13)

(20)

--·-

Th<>sP two outputs arA fAd to thA PnablP i"'ln11ts nf half of a

CD 4066 (Quad switch). ThA X-Y~ J lr>ast counts ,=mablPs thP clock

pulsP to thP countAr, whilA thP X-Y> J lPast c011nts sPts thP cmmt .. ,n~'s

clock pulsP input to ground, ThP X-Y'> J lpast counts also triggArs

an L-r.:D and AnablPs thP thrAP <lisplays, chan".1°1 nuribAr, ADC output and

RJiJ!. output,

ThA cl0ck pulsA gpn,:,rator is half of a CJ L:.')11 (Quad NA1\JD !<;ab=~).

(.)) ¢

(fig:. 14)

ThP two rAHD v,atAs act as a multivib!"at0r, Tl-to voltagA wavPfo!'P'!S

...----T -----'>'

T

~ 2,2 H.C

f- ln (Vdrl - Vtr)l (2Vrirl - Vtr)J

. ·1 6 l·1axirnnrri variations in ''.:' aro l 0 ss than 5',v.

For 512 chann°ls pP.r soconrl, Rte c:: 500 IUL, anrl C = 2000nf, F'('):r

20 channAls pAr sPconn, Rte ~ 250 IUl an.-J C = , 1 /.tf.

A -··4----~-0

0

1

1

6

B C ____ .,., ----------- ~-·-0

1

0

1

0

0

()

1

(fi_g, 1t)

( ')' 2, .. )

C

5'.32

binary to HCD conVP.rtPrs, in thP followinR" config,1ration. 7

'""' v .... 8 bit Binary to BCD 9 bit Bi,;ary to BCD

(fig, 17)

drivArs, which rnn th A rlisplays.

and a 20 cps pulsA, th2.t ar0. usP.d in thP T"a>:·121 r,ociA. ThA 20 cps

pulsP. us0.s thP. samP configuration as thn 500 cps pulsP but with a

ilA'\JD g;atr>s in an S-R flip fln"? confi>1nrat~ r:r:, This avr}irls bnuncP

(23) 7Tho TTL L)9.tn b0ok for DAsig-n Dn";irtPPrs, "'oxas Instrurna.nts Inc., 1976 I, 1), 7-295

R/S Flip Flop & Trut:1 Ta.blA

?. s Q --··

0 0 RPtains last StatP

0 1 1

1 0 0

1 1 RAtains last, stat,,, • -r l.o prPVious SR statP was 01 or 10

(fit!. H3)

rnn modP., thA clock pulsr-, fails, ThA clnck rnlsA ar.d thP. X-Y :6. 3 lAast

crmnts a.rP. run thrnur;h bnff Prs anrl thPn t~ !'01-1,;h DP.ak folloi,mrs. Whi:m

AithAr of thPSP. inputs is hift.h, +-5 vnlts, t:'1"' niitrmt of th0 DAak

:ihAn Pi.thAr of thA innuts rlrnns tn r-rni:n~, t:.: 0 ,,,1trn1t nf th<"> fnllnv.rPr

• L L -t/rtC ,.Jill dPcay PY.nnnPntialy, ~. ~ r-o , i:5:v c,:,..,,...,sir.£" :tC rnnch l:.:irp;""r than

thP ari thrnPtic opAration, thP outp11t wtl1 ,..,...-l_v 'iron tn a lnvical low

if Pith*"'r input rlrops low fnr ~1 signific2::+:. t1-=<>, R. was chnsAn to bP

10() LJL nnd C to bP. 1 J"-f, giving a tirr1P c-:,,s"':.an+:. of .1 SAcrmd. SP0

fits'H'P 19, Th"' 01Jtput of th0 two pnak f0:_1'"'~·~0 rs is run through a.n

AiD i:;ntP, If <>ithPr inp11t nrnps low, th"' ,,,_,+,;)u1:. rif thP. AND gatA will

drop loH I ancl thP. fa.llinn: PdgA will cnI'1t:l 0 :" 0 r."", thr.> 0utnnts 01 a J-1'

flip flop USP.11 in R clnckr.>'1 onArat i.on 1"10<1<>. ::'h,:, alarri is firAcl by

(24)

the Q output of thA J-K flip flon, whilP th"' Q output in<licatAs that

thA systAm is running normally, ThP ala!'!"' can bP silAncAd by pulsing

thA clPar input of thA J-K flip flop lnw, ThA X-Y) 3 lPai:;t counts linP

will also triggAr an LT;,TJ, inclicating a voltagP flucna.tion in tJ1A

monitorAd voltage, and will remain on until thA voltagA is cnrrActPd.

ThP anrl gatA connecting the two peak folloWP!'S is automatically

disconnP.cte<l whAn thP. manual modA is nsecl, and the alarrn will only

triggAr if the. X-Y f:3 lMst counts drops low,

it:l'H4

4.Sv

!·--·C \

~i J K Q ',--\_~

,_ __ , ~ ~OC~\.

(fig, 1 q)

(25)

. ..L

X: = Don't Carn H = Hii?;h lPVAl L = Low l,wAl

J-E Flip Flnp 'l'ruth TablP *

ClAar_ Clock J L X X

H

H

H

.H

L

H

L

H

,l, = Fa.llinf'; AdfP of clock pulsP

(fir., 20)

(26)

[

X

L

L

H

H

q ___ Q

L H

RP.tains last stat~

H

L

L

H

* Without PrPsAt input

At thP nrAsPnt timf'l, construction of thP s1rstPrn is not yAt

not inclu<fod in this proto-tynP sine"' WP WPr0 r0t HblA to obtain

thP SN 74185' s, binary to BCD convArtArs, ThP ADC us Ad for thP

proto-typA was also <lAfActivA, om::, bit of tho rrntnut always rAmaining

low and anothPr always rAmaining high, A nPW AX a.net thA SN 74185' s

arA AXpACtA<l to arrivA in latA July,

A hAat tAst was conductArl on thA rAsist("l:r cb..ains and mnltiplAxing

componpnts with tho monitorwi voltages varyin? loss than .Lb. SincA

this is one t,mth of nnA lf'last significant bit, it nrAsr-nts no nroblem.

-maintain ;,;~ low throuQ'.hout thA ini.tializati0n rr:r)rlo. It was fonnrl,

hoWPVAr, that thP ADC' s output W()11lrl chango tn a hhr,h irr,nprfa.nco statP

approxirnatAly 10 ns bAforA thA DR outnut w;:::,r.t 'ligh. SincA thA DR

impPdancA output from thA ADC was thP last data writtAn into mAr.tory

prior to a rno:w ai!d:r.Ass t and this :t.'Asul tAd in PrrnnPOUS data bAing

triggPrAd by thA fall of DH. was usA<l tc.i ,,r;_ t"' -lat~ into J11Arrtory, and

th A pulsA width was li.td tnc:l to AnsurA tha-: t'.1° writP opAration was

co~pl 0 tAd prior to a n~w convPrsion,

(27)

It was a1sn originally ph.nnAd to 11sP C'.) 4066' s, quad analog'.

swi tchAs, to ,=mablP. th A display. It was found, how•vAr, that thP.SP.

switchAs arA VP.ry suscAptiblA to failur.A rAsultin§". from static

chA.rgAs, and their intArnal protAction was insufficiAnt. ThAy WArA

rPplacAd by AND gatAs. A sPriAs of th ASA s~d tchAs is still usAd

to load thA arithmAtic componAnts, :mrl this is probably thA WAakAst

wnuld prribably bP tn rPplacP thPsn by a S"'!'i 0 s of AND and OR vatAs,

d, t{>1> 1:>. dJ,b . I tz ~ u

I x.,

d, cl~t 1>; cl>'D

~ 9 w

I Y.

( fig, 21)

This w011lrl rAquirA nnly four morA chips. I1°nlacinq: all othPr C'FOS

componAnts othPr than thA rr.ultiPlAxing col"Cton°nts which J'l'lust rPmain

CJ10S, with th Air 'rTL AOlliVA.lnnt W01Jlrl prnb2.blv rPsult in a hardiPor

svstPrn. ThA only altArnativA to thA USA 0f a GOS MultiplAXAr is thA

USA of rAAcl switchPs controllPrl by dPcodPr/ rlrivors, This wouLi b""

PXDAnsiVA anrl bnlky, ThAs,., changPs WAro !"\')t !"Ji'1A sincA during thA

(28)

thA rAal systP.~ had alrAady bAAn nbtainPd,

ThP, only rP1:tl rliscrP,pAncy bi,,twMm :ratPri ann actual pp,rformancP

was found in thn clock pulsP, gAnic~rators. Th A CVOS manual snp;gAstA<l

using anothAr rAsistor bAtwMin Rte anrl thP inputs of thA first NAND

gatp, (SAA fi~urA 14), It was found, hoWPVPr, that this rAsultAd in

dampAd oscillation on thA rising AdgA of thA clock pulsA, oscillations

with a width of approximately 100 ns, da,~nAd to Zf~ro in about 1_µ.s.

This wa.s nliminatAd by not using thA rAsistor. SincA the rAsistor

was suggAstP.d only to dAcrAaSA varia.+,ior.s in frAqttAncy by onA to two

pP.rcP.nt, thArA wa.s no problem in Alir11inating it.

Finally; a low pass filter was added t'J the vieual alarm end display

enable lines. This was ner>essary sin-e du-'ing analog to digital

r>Onveri::-irin, the ADC' s output wa.s a high irrpedan1;e f'tate, and the ala~m

and enable line2 went high du"ing the ·')r;ve:rdon. · With the low pN:G

c·1.1te:r, the visual alaYm a.nd display ena~le line2 wey·e only af-re,~ted by-

a ,-eal dis~Ye-pen-'y in the monito-r·ea V'Jlte.:;e,

(29)

SumMarv ··-----... ~~

Th0 r.P.sistor ch.ains WArA mountAd on two ir.nut pannAls, 1 O½" x 19"

rack pannAls, ThP dindA chains and thA r"'JltinlAxing cmnpornmts WP.re

mountAd on two 12" x 19" fibPrglass boaros, All other componAnts

w~re mountAd on fivP VP.ctnr D, I. P. plm1 boar'is (3677's). All Ct~OS

on thP. back of thP card cagA allow accPss to all signals fnr niagnostic

pnrposAs.

ThP. construction of the voltac,:P rrnnit0::-- do<>s not Aasily allow

furthAr P.Xpansion. ThP countPr (CD 4040) is hoWPVAr a 12 bit countAr

rrnd furt.lv~r channels conld bA nbtainAd by :.:1° addition of CD 4067' s

(mnltiplPXArs) and anothAr CD 1+515 (4 tn 16 '1AcodPr/drivP.r) enablP.d

by th"'? 10th bit of thP. countAr, ThA Pnab;. 0 :.nnuts to the two original

thP. arlrlt'PSS disnlay, This cmilrl not ho -1,-,r: 0 sirml:.r,

(JO)

bP. to locat0 thP. sp0cial chann"'ls at th 0 <>n'1 0f t,hA array, ( thP- last

channAls), anrl to comparA thA arlrlrPss with thP channAl numbAr of thA

first spAcial channAl. ThP. lngical outn11t 0f thA opAratinn woulci

thAn bA usAd to loan thA X-Y cnMparat0r with thA riAsirAri nurr,b,-,r of

lAast counts.

ThA l'lnnitoring ratA can bA chang:Prl by r,..,nlacing thA rAsistors and

capacitors which control thA timP. consta,,.,t of th,.., clock pnlsA

gAnArator. HoWAVer, if fastAr monitorinq is rlAsirAd, thA rlPlayAd

pulsP.s nPACT to bA Rrl j11st,::,<l accorrlimr,ly,

Inrlivirlua.l componAnt spAcificatin'!'"ls can bP. frmnd in th~ C1'0S

and TTL manna.ls, ThP pin confir;urations of thP componf-mts usPn

haVP. bAAn inclndAd as AppAn"lix II tn fA.cilitato 11SA of t.h"' schPmatic,

In conclusinn, alth()llfl:h construction of thA ch:ivicP is nnt complc,tp,

tPsts of thP proto-typA, inrlivirlual corrr/m<=>nts and thosA portions of

thA actual dAvicA prASAntly corripl"'t"'d C"nfrirrn tn thA spPcifications on

pagA six, Th,.,. systmri doP.s )'l'lonitor 511 v0ltaqPs of PithAr polarity1

sounrling- crn audio anrl a visual alarm wh 0 n a r,,,·mj_torAd voltar:rA OAViatr->5

from its initial valuP. by fnur or mor0 loast c01mts. Th"' aurlio alarm

can bP. silrmcmi at thP. control pann,..,l, ThP systPm doP.s indicate thP.

addrAss of thP incorrpct voltagP, its val11°, and the initial valnA 1

and all channAls arA Moni torPn in onP SPCr:n-i. ThP ini tia)J_za.tion

l'lon"' is q11ick anrl acc11rA.tP, Th 0 corr"'cti0n t0 rriomory monP ha.s bPPn

tPstr->d ;,_nrl w0rks, ann thP 20 cos clock an."1 siYJfl'l"' p11lse gPnffrator wotl<-

thP d1wicA, it can bA stat""c'l safolv that t11° ,i,:,vi_c"' will function

(31)

___ - - ___ - - - _ - - - - Panel Mounted _ - - - __ _ V3 V4 V5 V6 V7 VS V9 VIO VII Vl2 Vl3 Vl4 Vl5 Vl6 Vl7 VIS Vl9 V20 V21 V22 V23 V 4 V25 v:

19 20 21 22 23 24 25. 26 lk!l

lk!l

t II 13 15 17 19 21 23 2!5 27 2931 33 M

I Ii Ii Ii Ii ITlili 'il'i lililililiIT 'ililr r •Te' 4>2",,i'77•1J1, , (2) I (3) II ·. (4) 11 (5) II (6) II (7) I D 4067 I) 10 II M t! 1' I

I I I I I I I I I• I I I I I I l I I I I f I I I I I I I I I I I I I I

I I I I I I I

I E2 E3 E4 E5 E6 E7

I I I I I I I

I CD 4067(17) I (18) I (19) 11

(20) II (21.) II (22) 11 (23) I I I I I I I I I I I I I I I I I I I I I I

I I I I I I I I I I I I I I I I [ I I I I

--·- --- --- ---- - --- ---- ---- - -E17 ,-----

AO Al .. .,

•• ., •• A7

01 o, •• .. Bi 07 ..

di .. .. .. " :, ..

1111 f Z340ttl0112 I

RAM l!li 7 14 I

I"'" ''""JWEICS I

EIS E19

11111 I RAM I

I I I

I

- _E~-- - E!_

I

vector 8 oord I (continued on page 2)

.

1111 RAM I

l I I

E22 E23_

1111 J RAM I RM

I I -r-r

n5• I 12 4 3 IO 12: 13 IOl

CD4063 7 6 5 9 ll ~ I

I I

- Panel Mounted - - - - - - - - - - - - -

CD 067's a CD 4515's : VDD • +5v, vss • -5v All other chips : VDD • +5 v • vss .. Ground

28 29 30 31 32 33 34 35 36

--:-, I I I I r I I I I

+-+-11-+-1-----"-t-t-t--t-t----'-t--t-t-t-t--"-+11-H-t---.L-++--+-tJ+-_._+-+-+-+-t---L.-.t-t-+-++--'-++++--t--~1-+-H--~'

I I I l I ---j--'-t------<--t-t---t-t----------t-t-t-t-----i--t-t--i---t---ri---r-i-i----~;---i-r1--~-+-+---t--~->-t-+-t-t--__.,-+-+-+-+---l--f-WI

---:-±--l-==-:=-==-=!-t-==---==-=::--:::::-t=-::=-=-:~=:_=tcttt.=='=b:i~===,-::-l::-t=---=-::=-=:::i=-==-=:-:::='"--t-=--==-::~---t=--=-==--==~-=1--1 _J E29 ___ ~ _ _E1.'.__ ____ Eg_ _

1

co 4071

D>1D$d

I I I I I I I I I I I I

I : ~~ I

D. L~wis G.R.

7•10·7? A VOLTAGE IIONITORING DEVICE

PAGE I D-6227-A 7790.9

.f

r I I I I I I I I I I I

I I_

01 D2D3 D4 D< d 01 d2d3 d4 D<dD5D6D708 D<d di d2 d3 d4 D>d DI D2D3 04 •• + + ,___j t+++----i •• + + ..----.-.i" + •• + ~ _+ + + -. ~ -~ -.-, -. r I'•• "t;!_j I CD406QJ I CD 4066:::JJ I CD 4066 I CD 4066 I I CD 4066 2 IC~ 4,g6i

I I I I I I I I '-

+5

I ii I 5 &151298 I CD 4030 5 4 II 10

•5 I ,., ........ "I

vector Boord 1 co 4008 10 II 12 15

( continued from page 1) r,,I I I 11

r---1 DI D2 D3 04

I I I I I I I I I I I I I I I I 3000

-12410 12 13 157:, CD 4063

3 9 II 14 I ,

J I 1. 11 •5 •5

D5D607D8

7 Segment Displays

-½

--i,-1 I I

l-1 I I

I I I I I 11 I I I I 11 I I 11 I I I I I I I I

I CD 4030J

111 r,. ....... J CD 4008 CD 4071

i'1'ii'i,~ 13 210 12 13 107]

CD 4063 +5 Manual 4 9 II 14 I ~ I Display

I I I I td 't'

Vector Boord 4 ---di d2 d3 d4

I 1...--~--~____.,...,.._......__._--L., I I

t - J I_~

Page 2

; o5 d6 d7 dB O>dos 060708 O>d

-~ .. ··~ • ... ~ -• l I C04066 I I co 4066 I I I I

LED

--2rT3oon

vector Boord 5

LED 3000

-1 I I I I I I I

•5 I t_..n I

I I

•2.5)

I I I I

__ J

Alarm

-15v

2000Pf

.....L

Run Single Channel

' .• J Jncrement

20 ch/sec

500k0

+5

IOOkO I

.-------.~~ I IOOkQ:

+5 I I I I I I

_________ _j

-····-. ----------------·-----1 ' . .lf'C·l,t'!~,J:{ ~·1P N11C1 Eol\k $(i;r,cr

l.!,l ,.,>· ... ,·.;_T!~ 11-lMif·JIE m ftLH ... ,:•!. 1 1'",'f ,:w;.10,u. "'"s.,

~:~~wi, ::: _ _:::~:- •7:10-79 --==-:=-. -l· A VOLTAGE.MONITORING DEVICE

, PAGE 2

.. . iC,\·.· ··.~ -~ o=e2·27~·9----~1~:=F~~

AppAndix II

,... Cg

•• ,5

•• ,;.

13 ., 3 .. 82 . •• $z

e, • ., ' .. c,c:r----------' CCARq-.,.,._:

CD 4040,

104011A

CD 4011, Quad Nand GatA

CD 4040, 12 Bit CountAr

(33)

I I, I

" J•A@B L•EE)F' K•C@D M•G(t)H

CD 4030, Quad W:xclusiVA Or GatA

'I

CT) 40L1,7, Ynnnstabl,,/ Ast11bl<> }Anltivibratnr

A ~ C•i

~ thii

!.{>! J•C

,o ~ J• 5

[ ~ K•E

F~t.•1

•cc-1 -•ss-•-t\lC, 13 NC •1& lo1

,_ C04049A.

A~ C•A .~ -----v- H•B

!..{>--! l•C

D~J•D

~ -----v--- K • E

, ~_f'....._1~ -----V--- L ,r •cc-'-•ss-•-,., •13 NC •16 Cit)

92CS~10il6

C04050A

CD 4050, HAX BnffP.r

CD 4066, Quad Analog Switch

A~G

B~H

cL{»-!-1 O~J

E~K

F~L

9ZCS-1l7l7fll

CD4069B FUNCTIONAL DIAGRAM

113 UcBlnt IA•Bl1N c.~a,v•

IA>lllour IA•9)QUT ,.,.eJour

"'ss

Voe Al 1l2 A2 Al Bl /,IJ BO

(TOP VIEW) 9ZCS•ZOZ:,.

TERMINAL ASSIGNMENT

CD 4063, l~ Bit Cnmpa.rator.

C0t.lM'C"4 OVTIIN

~--" ~ "=t

(34)

A 8

Vss TOP VIEW

CD4067B

CT) lrn67 , 16 ChannAl }~ul ti pl,c,xnr

FUNCTIONAL DIAGRAMS

CD 4071, Qnad Or GatP

INHIBIT ~·°"'t====-_j CD4514B, CD4515B FUNCTIONAL DIAGRAM

~D 4515, 4 to 16 LinA D"lcodAr

SN 71..J,46, BCD t0 7 SPgmPnt DPcodPr/DrivPr

SN 74185, Birw.rv to BCD ConvPrt,,r

(35)

SN5408 IJ, W) SN7408 IJ, N) SN54LS08 (J, W) SN74LS08 IJ, N) SNS4SOB IJ. W) SN74S08 IJ, N>

S:T 7408, Q1Jad And Ga.t<=,

1CK 1 1K Vee :ZCK % Cl.ff CLR

SN5473/SN747~(J, N. W)

SH 7473, ,J-:K Flip Fl0p

J OR N DUAL-IN-LfNi: PACKAGE ITO?VIEW)

I l. __________ ...,. SP 72723, PrPcisinn VoltagP ~g11lator

GROUND I. IV°

JOUTPIIT

IIAL•Wtt nRDIE

-Y-4 51.lLONCE.

TOP VIEW.

nr 311, Vnl+,a9:P CnMpa:rat0:r

14-LEAD DIP (TOP VIEW)

PACKAGE OUTLINE 6A, 9A

NC

NC

NC

V+

OUT

OFFSET NULL

NC

CONNECTION DIAGRAMS 14-LEAD DIP ITOPVIEW)

PACKAGE OUTLINE 7A 9A PACKAGE CODE O P

l

OFFSET 5

NULL 8

+IN 8

-IN B

pt.ft. 747 1

f

V<f-A .._

Dual Gp-Amp

('36)

![AeU Bachelors[2] (1)](https://static.fdocuments.in/doc/165x107/563dbb9a550346aa9aaea18c/aeu-bachelors2-1.jpg)