A PFC power supply with minimized energy storage ... · A PFC power supply with minimized energy...

Transcript of A PFC power supply with minimized energy storage ... · A PFC power supply with minimized energy...

A PFC power supply with minimized energy storagecomponents and a new control technique for cascaded

SMPS

by

Damien F. Frost

A thesis submitted in conformity with the requirements

for the degree of Master of Applied ScienceGraduate Department of Electrical and Computer Engineering

University of Toronto

Copyright c© 2009 by Damien F. Frost

Abstract

A PFC power supply with minimized energy storage components and a new control

technique for cascaded SMPS

Damien F. Frost

Master of Applied Science

Graduate Department of Electrical and Computer Engineering

University of Toronto

2009

This Master of Applied Science thesis proposes a new design of low power, power factor

corrected (PFC), power supplies. By lifting the hold up time restriction for devices that

have a battery built in, the energy storage elements of the converter can be reduced,

permitting a small and inexpensive power converter to be built. In addition, a new

control technique for controlling cascaded converters is presented, named duty mode

control (DMC). Its advantages are shown through simulations. The system was proven

using a prototype developed in the laboratory designed for a universal ac input voltage

(85 - 265VRMS at 50 - 60Hz) and a 40W output at 12V . It consisted of two interleaved

phases sensed and digitally controlled on the isolated side of the converter. The prototype

was able to achieve a power factor of greater than 0.98 for all operating conditions, and

input harmonic current distortion well below any set of standards.

ii

Acknowledgements

I would like to express my gratitude to both of my supervising professors, Professor Peter

Lehn and Professor Aleksandar Prodic, who gave me both the opportunity to study with

them and this exciting project for my thesis. Furthermore, their guidance and support

were invaluable assets that led to the completion of this work.

I also would like to thank all of the fellow students in the SMPS laboratory for their

insight and patience, especially Zdravko Lukic and Amir Parayandeh.

I would also like to acknowledge all of my friends and the members of The Attic for

their constant support and for all of the great memories I have from my graduate studies.

Finally, I would like to thank my family for their unconditional love and support

throughout all of my studies.

iv

Contents

1 Introduction and Background 1

1.1 Background . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

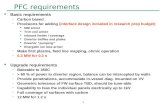

1.1.1 Simple active PFCs . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2 Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.3 Literary review . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.3.1 PFCs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.3.2 Control of cascaded SMPS . . . . . . . . . . . . . . . . . . . . . . 8

1.4 Objectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2 Proposed System 10

2.1 Energy storage in PFCs . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 New PFC design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3 Duty mode control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.4 Centralized digital control . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3 Capacitor Ripple Voltage and Steady State Analysis 15

3.1 Limitations on the capacitor voltage ripple . . . . . . . . . . . . . . . . . 15

3.2 Flyback in steady state . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.2.1 Differential equations of the converter . . . . . . . . . . . . . . . . 19

3.2.2 The flyback converter in steady state . . . . . . . . . . . . . . . . 20

3.2.3 Control for unity power factor operation . . . . . . . . . . . . . . 21

v

3.2.4 A comment on theory . . . . . . . . . . . . . . . . . . . . . . . . 23

4 System Modeling and Control 25

4.1 Duty mode control (DMC) . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.1.1 Advantages of DMC . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.1.2 Two stage DMC example . . . . . . . . . . . . . . . . . . . . . . . 27

4.1.3 DMC model with downstream PID compensator . . . . . . . . . . 30

4.1.4 State space model . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

4.1.5 Control to output transfer function . . . . . . . . . . . . . . . . . 33

4.1.6 DMC vs. conventional control . . . . . . . . . . . . . . . . . . . . 35

4.2 System models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

4.2.1 Lossy buck converter in state space . . . . . . . . . . . . . . . . . 38

4.2.2 Lossy flyback converter in state space . . . . . . . . . . . . . . . . 38

4.2.3 Additional parts of the system model . . . . . . . . . . . . . . . . 45

4.2.4 Complete system model in state space . . . . . . . . . . . . . . . 48

4.3 Controller design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.3.1 Voltage controller design for buck converter . . . . . . . . . . . . 54

4.3.2 Current controller design for the flyback converter . . . . . . . . . 56

4.3.3 DMC controller design for the flyback converter . . . . . . . . . . 58

5 Experimental Results 62

5.1 Flyback component selection . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.1.1 Flyback transformer . . . . . . . . . . . . . . . . . . . . . . . . . 62

5.1.2 Main energy storage capacitor . . . . . . . . . . . . . . . . . . . . 63

5.2 Converter specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.3 Steady state operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.4 Power factor and THD . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.5 Transient response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

vi

5.6 Energy storage comparison . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.7 Limitations of the proposed system . . . . . . . . . . . . . . . . . . . . . 71

5.7.1 Current measurement . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.7.2 Loss in main energy storage capacitor . . . . . . . . . . . . . . . . 72

5.7.3 Hold up time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6 Conclusions and Future Work 76

6.1 Conclusions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

6.2 Future work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.2.1 PFC supplies with minimized energy storage . . . . . . . . . . . . 77

6.2.2 DMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.2.3 On chip integration . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Appendices 80

A Circuit Schematic 80

A.1 Circuit schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

A.2 Bill of materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

B Measurement Devices 89

Bibliography 94

vii

List of Tables

3.1 Parameters of the flyback converter simulation . . . . . . . . . . . . . . . 23

4.1 Parameters used to compare DMC and conventional control. . . . . . . . 35

4.2 Parameters used in the buck converter developed in lab. . . . . . . . . . 55

4.3 Parameters used in the flyback converter developed in lab. . . . . . . . . 57

4.4 Parameters from the laboratory used in the complete system model. . . . 59

5.1 Technical specifications for the main energy storage capacitor. . . . . . . 63

5.2 Technical specifications of the main energy storage capacitor . . . . . . . 63

5.3 Performance specifications of the converter designed in the laboratory. . . 64

5.4 Technical specifications of each phase of the converter . . . . . . . . . . . 65

5.5 Voltage ripple on the main energy storage capacitor . . . . . . . . . . . . 67

5.6 Energy storage comparison . . . . . . . . . . . . . . . . . . . . . . . . . . 71

B.1 Table of measurement devices used. . . . . . . . . . . . . . . . . . . . . . 89

viii

List of Figures

1.1 The traditional diode bridge rectifier used as an ac to dc power supply. . 3

1.2 The voltage and current waveforms of the diode bridge rectifier . . . . . . 3

1.3 Topology of the flyback converter. . . . . . . . . . . . . . . . . . . . . . . 4

1.4 The averaged switch model of the flyback converter in DCM. . . . . . . . 4

2.1 A typical two stage PFC supply. . . . . . . . . . . . . . . . . . . . . . . . 12

2.2 Topology of the proposed system. . . . . . . . . . . . . . . . . . . . . . . 13

2.3 Block diagram depicting DMC. . . . . . . . . . . . . . . . . . . . . . . . 14

3.1 The ripple current in the capacitor . . . . . . . . . . . . . . . . . . . . . 16

3.2 The ac power absorbed by the storage capacitor . . . . . . . . . . . . . . 18

3.3 The flyback converter with the main switch, Q1, on. . . . . . . . . . . . . 19

3.4 The flyback converter with the main switch, Q1, off. . . . . . . . . . . . . 19

3.5 Flyback operating at unity power factor simulation . . . . . . . . . . . . 24

4.1 Block diagram depicting DMC. . . . . . . . . . . . . . . . . . . . . . . . 26

4.2 Converter used to illustrate DMC. . . . . . . . . . . . . . . . . . . . . . . 28

4.3 The linearized model of the buck converter with losses. . . . . . . . . . . 29

4.4 Complete model of two converters in series to show the properties of DMC. 31

4.5 Transfer functions of DMC vs. conventional control . . . . . . . . . . . . 36

4.6 Step response simulation of conventional control vs. DMC . . . . . . . . 37

4.7 The buck converter with losses and switching network shown. . . . . . . 38

ix

4.8 The flyback converter with losses. . . . . . . . . . . . . . . . . . . . . . . 39

4.9 A PI controller in state space. . . . . . . . . . . . . . . . . . . . . . . . . 48

4.10 The complete small signal model of the system. . . . . . . . . . . . . . . 48

4.11 Bode plot of GBvc (s) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.12 Compensated bode plot of GBvc (s) . . . . . . . . . . . . . . . . . . . . . . 56

4.13 Bode plot of GAic (s) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.14 Compensated bode plot of GAic (s) . . . . . . . . . . . . . . . . . . . . . . 59

4.15 Bode plot of DMC transfer function . . . . . . . . . . . . . . . . . . . . . 60

4.16 Compensated bode plot of DMC transfer function . . . . . . . . . . . . . 61

5.1 input voltage and current of prototype . . . . . . . . . . . . . . . . . . . 65

5.2 Voltage of energy storage capacitor while operating at full load . . . . . . 66

5.3 Comparing the theoretical and experimental duty cycles. . . . . . . . . . 67

5.4 The measured power factor of the converter developed in the laboratory. 68

5.5 The THD of the prototype converter . . . . . . . . . . . . . . . . . . . . 68

5.6 Harmonic current emissions from the prototype vs. IEC61000-3-2 . . . . 69

5.7 Transient response of the prototype - load increase . . . . . . . . . . . . . 70

5.8 Transient response of the prototype - load decrease . . . . . . . . . . . . 70

5.9 Current sensing waveform . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.10 The CBEMA Curve [1]. . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

5.11 Hold up time of the prototype . . . . . . . . . . . . . . . . . . . . . . . . 75

A.1 Overall circuit schematic of the converter built in the laboratory. . . . . . 81

A.2 Circuit schematic for the ADCs, ADC circuit.SchDoc. . . . . . . . . . . . 82

A.3 Circuit schematic for the linear regulators, LinearRegulator.SchDoc. . . . 83

A.4 Circuit schematic for the non inverting operational amplifier . . . . . . . 84

A.5 Circuit schematic for the power stage, PowerStage.SchDoc. . . . . . . . . 85

A.6 Circuit schematic of the gate drivers, GateDriver.SchDoc. . . . . . . . . . 86

x

A.7 Circuit schematic for the inverting operational amplifiers . . . . . . . . . 87

A.8 Bill of materials for one phase of the power stage. . . . . . . . . . . . . . 88

xi

List of Abbreviations

ac Alternating CurrentADC Analog to Digital Converter

CBEMA Computer and Business Equipment Manufacturers AssociationCCM Continuous Conduction Mode

dc Direct CurrentDCM Discontinuous Conduction ModeDMC Duty Mode Control

DPWM Digital Pulse Width ModulatorESR Equivalent Series ResistanceFFT Fast Fourier Transform

FPGA Field Programmable Gate ArrayIC Integrated Circuit

ICS Input Current ShaperIEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics EngineersIT Information Technology

ITIC Information Technology Information CouncilPF Power Factor

PFC Power Factor CorrectionPI Proportional Integral

PID Proportional Integral DifferentialRMS Root Mean Square

SMPS Switch Mode Power SupplyTHD Total Harmonic Distortion

xii

Notation

X (t), x (t) time dependent quantity〈x (t)〉Ts time averaged quantity over period Ts

x small signalX dc signal or constant quantityX constant matrix or vectorx vector of small signals

X (s) continuous time transfer functionx [n] discrete time quantity

xiii

Chapter 1

Introduction and Background

This chapter introduces the main topic of this work, low power, power factor corrected

(PFC), power supplies. In this area, two main foci will be addressed. First, the reduction

of the size of energy storage elements in PFC supplies and second, a new control method

to control cascaded switch-mode power supplies.

The size of energy storage elements in the converter is reduced by allowing a large

ripple voltage to appear on the main energy storage capacitor, greatly reducing the size

of this component. This ripple voltage is as much as 37% of the nominal value.

The new control method proposed utilizes the duty cycle of the downstream converter

to control the output voltage of the upstream stage. This reduces the number of sensors

required by one, and also provides a better transient response.

First a brief introduction to power factor correction is presented, followed by the

motivation of this work. A review of existing solutions is then presented and the chapter

concludes with the goals of this thesis.

The rest of the work is organized as follows:

Chapter 2 contains a description of the proposed system and describes its novel as-

pects.

Chapter 3 demonstrates how to use a capacitor in a PFC to its designed limits,

1

Chapter 1. Introduction and Background 2

utilizing its full energy storage capabilities.

Chapter 4 models the proposed system in state space and introduces a new control

method for cascaded converters, duty mode control (DMC). From this model, controllers

are designed for the proposed system that are verified in the laboratory.

Chapter 5 shows the results from the prototype converter built in the laboratory.

Chapter 6 summarizes the results from this work and suggests future directions that

can be investigated.

1.1 Background

Power factor is a measure of how effectively energy is transmitted between a source and

a load in a system. From [2] there are two different definitions for power factor and these

are shown in Equations (1.1) and (1.2). Equation (1.1) calculates the power factor in

the presence of harmonics in either the supply voltage or supply current. Equation (1.2)

calculates the power factor assuming the voltage and current are purely sinusoidal and

is only a function of the angle between the voltage phasor and current phasor, φ.

(power factor)1 =(average power)

(rms voltage) (rms current)(1.1)

(power factor)2 = cos (φ) (1.2)

For this work, Equation (1.1) will be used to calculate the power factor. Both equa-

tions stipulate that the power factor is a value between zero and one, and in order to

have the most efficient energy transmitting network, a power factor of one is necessary.

However, this only occurs when the load is a perfect resistor. Other loads such as reactive

and non linear loads introduce imaginary power and distortion into the system and will

cause current to flow from the source to the load and back again without doing any real

Chapter 1. Introduction and Background 3

Figure 1.1: The traditional diode bridge rectifier used as an ac to dc power supply.

0 0.005 0.01 0.015 0.02 0.025 0.03

Source Voltage

Time (s)V

olta

ge

0 0.005 0.01 0.015 0.02 0.025 0.03

Source Current

Time (s)

Cur

rent

Figure 1.2: The voltage and current waveforms of the diode bridge rectifier of Figure 1.1

work. This additional current requires all the components in the system to have higher

ratings and it also contributes to the heating of power transformers and transmission

lines. Therefore, it would be ideal if all loads had a power factor of one. For this reason,

many high power, and now low power, loads are required to meet government regula-

tions on current harmonic limits through standards set by the institute of Electrical and

Electronics Engineers (IEEE) and the International Electrotechnical Commission (IEC).

An example of such a non linear load is the traditional diode bridge rectifier, shown

in Figure 1.1, used as an ac to dc power supply. This circuit is highly non linear and the

current and voltage waveforms are shown in Figure 1.2. The power factor of this circuit

is typically around 0.55 to 0.65 [2].

The power factor of the diode bridge rectifier circuit can be improved either passively

or actively. A passive solution is to add a filter to the input of the diode bridge. This is

rarely done in practice, as the filter required would be large, expensive and would only

work for a certain input frequency. The second way to improve the power factor of this

circuit is to add a switching network after the diode bridge to regulate the input current.

Chapter 1. Introduction and Background 4

1:n

C1

Q1

D1

D

R

Figure 1.3: Topology of the flyback converter.

C1

D

RTnD

L22

2

p(t) T

Figure 1.4: The averaged switch model of the flyback converter in DCM.

This is commonly implemented and is discussed in greater detail in the next section.

1.1.1 Simple active PFCs

Simple active PFCs are circuits that emulate an ideal resistance when attached to an ac

system. The analysis of power converters based on average switch modeling [2], shows

that many common topologies are natural PFCs when operated in the discontinuous

conduction mode (DCM), without additional control. These converters include the buck-

boost, flyback, SEPIC and Cuk [2]. Therefore, using one of these converters as a PFC

is a simple choice. Figure 1.4 shows the averaged switch model of the flyback converter

of Figure 1.3. As shown, the input port of the converter is modeled as a lossless resistor

whose power is transferred over to the power source, connecting the load. The duty cycle

of the boost converter simply changes the value of the loss-less resistor to either increase

or decrease the input, and by consequence the output, power.

Although theoretically very effective, in a practical implementation of this system an

Chapter 1. Introduction and Background 5

electromagnetic interference (EMI) filter will be required to filter out the discontinuous

input current.

1.2 Motivation

Until recently, power factor correction has been limited to high power loads, through

standards like IEEE519 [3]. However in 2001 the European Union adopted the Inter-

national Electro-Technical Commission’s IEC61000-3-2 standard for electrical equipment

which puts harmonic current limits on all devices that draw up to 16A and consume more

than 75W in a 220V ac system [4]. Since then, Britain, China and Japan have adopted

similar standards [5].

These standards have yet to be adopted for North America, however one can assume

that they will be at least as strict as the IEC61000-3-2 in the near future. The inconsis-

tency in restrictions is due to the differences between the European and North American

distribution systems. North American distribution systems are predominantly a wye-wye

system and therefore, are more susceptible to triplen harmonics (3rd, 9th, 15th, etc.).

As a result, any limitations that might be imposed in North America will most likely be

very different from those set in the IEC61000-3-2 standard [6].

Furthermore, the restrictions are being applied to lower power devices most likely be-

cause there are an increasing number of highly non-linear loads being used by consumers

everyday, as seen in Canada [7], [8]. If all of the ac-dc power supplies found in an average

household were implemented with the diode bridge rectifier of Figure 1.1, the spikes in

the current generated by these circuits would not go unnoticed.

Finally, there are significant indications that there will be a market for inexpensive,

low power, PFC supplies. This work will fill this area by proposing a solution that

provides power factor correction with minimized energy storage elements, thus producing

lower cost, more compact power supplies.

Chapter 1. Introduction and Background 6

1.3 Literary review

1.3.1 PFCs

As shown in [9], PFC converters can be categorized into two main groups: sinusoidal line

current and non-sinusoidal line current. Converters with a non-sinusoidal line current

are the converters that meet harmonic specifications like the IEC61000-3-2, however

they may not be able to meet future harmonics specifications. Therefore, the discussion

here focuses on sinusoidal line current PFC converters.

1.3.1.1 The boost PFC

The boost topology operating in discontinuous conduction mode (DCM) is one of the

most natural PFC topologies. However, it has a few drawbacks, two of which are outlined

here. First, the energy storage capacitor must be able to handle voltages above the peak

line voltage of any input. Second, the input current harmonics are fairly high because

the current goes to zero after every switching cycle, putting more stress on the input

filter of the converter [10].

A reduction of voltage stresses on the main energy storage capacitor of the boost

converter has been achieved through a modified boost topology as presented in [11]. The

topology is called “The series inductance interval” and it is able to achieve a low voltage

on the storage capacitor as well as a low voltage swing depending on the input voltage.

A more detailed analysis of this converter and an improved version is presented in [12].

Many solutions to reduce the input current switching harmonics have also been pro-

posed and a common solution is to interleave many boost cells into a converter. By

using two cells one can reduce the switching harmonics by half [10] or eliminate them

completely with a slight modification to the boost topology as demonstrated in [13]. Fur-

thermore, [14] provides a solution to optimize the number of boost cells to use based on

the design specifications of the converter.

Chapter 1. Introduction and Background 7

Many variations of the topology have been developed in order to improve its perfor-

mance. Reference [15] provides a good survey of single stage PFC circuits with a boost

type input current shaper (ICS). In this review, many different topologies are examined

and are grouped into two categories of converters: converters with a two terminal ICS

cell and converters with a three terminal ICS cell. These two categories of ICSs are also

consistent with grouping of boost ICSs in [16].

1.3.1.2 The flyback PFC

As shown in [17] and [18], the flyback converter is one of the best topologies that is able to

achieve near unity power factor as well as direct power transfer to the load. Furthermore,

in comparison to the PFC boost, the flyback converter electrically isolates the ac and dc

sides. However, just like the boost converter, much research has been published analyzing

its performance [19], [20] and improving aspects of the converter. The flyback has also

been combined with other topologies to create novel single stage converters, as mentioned

in [15].

1.3.1.3 Digital control of PFC converters

Digital control of converters is becoming the preferred option for designers because it

allows for more flexible designs, shorter development times, the elimination of tuning

discrete components and increased reliability [21].

There have been many works published on the digital control of PFC converters like

the one shown in [22]. Therefore the digital control of PFC converters has been shown

to be successful.

To completely design a digital controller, an extremely useful resource is [23]. In

this work the authors give a complete overview of designing a digital controller. A good

complement to this work is [24], where three different digital control design techniques

are compared experimentally.

Chapter 1. Introduction and Background 8

1.3.1.4 Reducing the size of energy storage components

In the literature, all of the PFC topologies are designed such that they meet the hold up

time standard set by the Information Technology Industry Council (ITIC) [1]. However,

this hold up time was designed for devices that do not have a battery built in. Devices that

would benefit from a smaller PFC supply are those designed for portability, for example

laptops and battery chargers. Furthermore, one can expect these devices to be more

prevalent in the future considering for the first time in 2008, worldwide laptop sales have

outpaced those of desktop sales [25]. Devices such as laptops and battery chargers are

low power electronics that will likely have to abide by input current harmonic limits set

by governments. They are also devices that can withstand a temporary fault in the power

system quite easily because battery charging can be interrupted without consequence,

just as it can in a laptop since it contains a battery built in. Furthermore, smaller and

lighter power supplies are more desirable and usually must be taken along with the device

they power.

1.3.2 Control of cascaded SMPS

The discussion around the control and stability analysis of cascaded switch mode power

supplies (SMPS) has been largely limited to defining impedance criteria which the power

supplies must meet in order to preserve stability [26], [27], [28].

1.4 Objectives

The main goal of this work is to create a prototype of a low power, PFC supply, suitable

for portable electronic applications where the hold up time is not a necessity.

The objectives of this work are as follows:

• Reduce the size of energy storage components in the converter by increasing the

Chapter 1. Introduction and Background 9

switching frequency, allowing a large ripple voltage on the main energy storage

capacitor and creating an integrated design of the system.

• Introduce a new method for controlling cascaded SMPS and combine all the con-

trollers of the system into a single FPGA.

• Exploit low cost and low voltage components by appropriately designing the power

stages.

Chapter 2

Proposed System

This chapter introduces the proposed system. It consists of two parallel converter systems

operated with interleaved switching, to reduce input current switching harmonics. These

are referred to as interleaved phases. Each phase is rated for a 20W load and consists

of a flyback converter connected in series with a buck converter. The flyback acts as a

power factor corrector in the system, and its output capacitor is the main energy storage

component of the system. This capacitor is targeted for size reduction. As a consequence,

a large ripple voltage on this capacitor exists with a nominal value around 50V dc. The

buck converter acts as a constant power load on the flyback converter, outputting a

regulated 12V dc. The total output power of the system is rated for a 40W load. The

system was designed for low power PFC applications where hold up time is not critical.

However, being an interleaved system, more phases could be added to increase the output

power to the desired amount.

The rest of the chapter will introduce the main problem with unity power factor ac/dc

conversion, followed by the proposed converter topology. It will conclude by introducing

a novel control method for controlling cascaded converters.

10

Chapter 2. Proposed System 11

2.1 Energy storage in PFCs

One of the largest problems PFC supplies face when powering a dc load is dealing with

the second harmonic power ripple. The problem may be understood by studying the

power entering a PFC, as shown in Equation (2.1) below.

Pac (t) = Vg cos (ωt) Ig cos (ωt) =VgIg

2(1 + cos (2ωt)) (2.1)

From this equation it is clear that the input power into a PFC supply contains a

second harmonic ripple component. The output dc power is defined by the average value

of Equation (2.1) over a period, (VgIg) /2. During times when the input power is less

than the output power, the PFC must have sufficient energy storage to supply the dc

load. Providing this power is conventionally done with a large capacitor, and in the case

of a boost converter acting as a PFC operating in CCM, a large high voltage capacitor.

A capacitor of this type is very large, bulky and expensive. Moreover, its energy storage

capabilities are under utilized. In the proposed solution the capacitor will be reduced in

size so as to maximize the use of its energy storage capabilities. As a consequence, there

will be a large ripple voltage on the main energy storage capacitor of the system at twice

the frequency of the line voltage and this will introduce control challenges that have not

previously been addressed.

2.2 New PFC design

Traditional PFC supplies comprise of two stages [29] and require sensing and control on

the non-isolated, ac side as well as the isolated side for any downstream converter. An

example is shown in Figure 2.1.

The design of these power supplies is such that the output voltage of the PFC, the

voltage on capacitor C1 in Figure 2.1, remains relatively constant. This requires a large,

Chapter 2. Proposed System 12

T1

Vg LoadC2C1

Q2

Q3

Q1

D1

PFCController

VoltageController

Main EnergyStorage

Capacitor

Ig

Figure 2.1: A typical two stage PFC supply.

expensive, and in the case of boost converter acting as a PFC in CCM, a high volt-

age capacitor as the main storage element. The proposed PFC design eliminates these

requirements on the main energy storage capacitor.

The topology of the proposed system was chosen such that a few basic criteria could

be met:

• Galvanic isolation

• Universal input voltage (85 - 265Vrms at 50 − 60Hz)

• Convenient output voltage for household electronics (12V )

In addition, the topology was chosen such that other novel criteria could be met,

which would also reduce the cost and size of the converter:

• A small, low voltage energy storage capacitor

• A single, centralized controller

• Reduced voltages in the converter

Taking these points into account, a conventional topology of a series connection of a

flyback and buck converter was chosen as shown in Figure 2.2.

Both converters operate in continuous conduction mode (CCM) to reduce peak cur-

rents in the system. To decrease the switching harmonics, an interleaved, two phase PFC

stage was implemented.

Chapter 2. Proposed System 13

1:0.32

Vg LoadC2C1

Q2

Q3

Q1

D1

PFC and VoltageController

Main EnergyStorage Capacitor

Ig

Figure 2.2: Topology of the proposed system.

The turns ratio on the flyback transformer was chosen to provide a step down in

voltage. This allows the main energy storage capacitor of the system, C1 in Figure 2.2,

to be an inexpensive, low voltage component. The turns ratio chosen for the system was

1 : 0.32.

Isolation is maintained through the use of a single optical coupler to send a gating

pulse to the main switch, Q1.

Finally, a significant innovation in the proposed converter is the location of input

current and voltage sensors. Both sensors are placed on the secondary side of the trans-

former, allowing all sensing and control to be done on this side. Voltage sensing is

accomplished when the main switch Q1 is in the on state. During this time, the voltage

across the primary side of the transformer is reflected to the secondary side and thus can

be read by a sensor. Current sensing is accomplished when the main switch turns off,

forcing the magnetizing current of the flyback transformer to flow through the secondary

side, and therefore through the sensing resistor. In this way the controller can be com-

bined into a single chip, as shown in Figure 2.2. As shown in Chapter 4, this will allow

us to further reduce the size of the energy storage capacitor.

Chapter 2. Proposed System 14

2.3 Duty mode control

Combining both controllers for the PFC stage and the downstream converter on a single

chip allows a novel control technique to be developed, which will be referred to as duty

mode control (DMC). Similar to how voltage and current mode control operate, the

voltage on the main storage capacitor will be controlled such that the duty cycle of the

downstream converter is held at a reference value. System dynamic studies presented

in Chapter 4 show that this control method allows us to further reduce the size of the

main energy storage capacitor C1. A simplified block diagram of the controller is shown

in Figure 2.3.

Centralized DigitalController

1:0.32

Vg LoadC2C1

Q2

Q3

Q1

D1

VrefBuck VoltageCompensator

PWM

Duty ModeController

FlybackCurrent

CompensatorPWM

Dref

Ig

Figure 2.3: Block diagram depicting DMC.

2.4 Centralized digital control

The proposed centralized control method allows the entire controller to be implemented

on a single field programmable gate array (FPGA). Digital control permits the use of

control techniques that would be difficult or impossible to implement with standard

analog control. These include DMC and a self adjusting dead zone controller as described

in [30].

Chapter 3

Capacitor Ripple Voltage and

Steady State Analysis

This chapter begins by deriving an equation that allows one to use an energy storage

capacitor to its designed limits. Following this, the steady state analysis of the flyback

converter powering a dc load at unity power factor is carried out. In particular, the

consequences of allowing a large ripple voltage on its capacitor are studied.

3.1 Limitations on the capacitor voltage ripple

First, an expression for the ripple voltage on the capacitor is derived based on the rated

ripple current the capacitor can handle, Ir, which is measured in amps rms.

Figure 3.1 shows the ripple current in the capacitor. The shaded region is the amount

of charge, ΔQ, that is deposited onto the capacitor when the current is positive. This

charge is added to the charge residing on the capacitor when it is at its lowest voltage,

VMIN . Therefore the maximum voltage on the capacitor is given by Equation (3.1):

VMAX =QMIN + ΔQ

C(3.1)

15

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 16

Time (s)

Cur

rent

(A

)

Δ Q

Figure 3.1: The ripple current in the capacitor. The shaded region represents the chargedeposited on the capacitor after t = 0.

where QMIN is the charge on the capacitor initially at t = 0 and C is the capacitance.

Defining ΔVr = VMAX − VMIN we find that:

ΔVr =ΔQ

C. (3.2)

Integrating the current over one half cycle to obtain ΔQ yields:

ΔQ =

√2Ir

πfr, (3.3)

where fr is the frequency of the second harmonic of the system. Substituting Equation

(3.3) into Equation (3.2) the peak to peak ripple voltage on the capacitor is obtained in

Equation (3.4).

ΔVr =

√2Ir

πfrC(3.4)

Next, in an ideal PFC circuit, the current and voltage waveforms are sinusoidal and in

phase with each other. Therefore we can easily obtain an expression for the instantaneous

input power:

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 17

Pin (t) = Vg cos (ωt) Ig cos (ωt) =VgIg

2(1 + cos (2ωt)) (3.5)

where ω is the line frequency.

Equation (3.5) can be separated into a dc and ac component yielding:

Pin (t) = Pdc + Pac (t) (3.6)

where,

Pdc =VgIg

2(3.7)

and

Pac (t) =VgIg

2cos (2ωt) = Pdc cos (2ωt) . (3.8)

Assuming that the ac component of the input power is absorbed completely by the

storage capacitor, we can determine the ripple on the capacitor that will result in this

oscillating power. This assumption is valid as long as the magnetizing inductance and

current are small enough such that 0.5LmI2m << 0.5C1V

2C .

The shaded region in Figure 3.2 represents the energy absorbed by the capacitor for

one half cycle. This absorption of energy will increase the capacitor voltage according to

Equation (3.9). Let this energy be called ΔE.

ΔE =1

2C

(V 2

f − V 2i

)(3.9)

where Vf , Vi and C are the final capacitor voltage, initial capacitor voltage and the

capacitance, respectively.

Integrating the ac power over a half cycle to obtain ΔE yields:

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 18

Time (s)P

ower

(W

)

Δ E

PDC

Figure 3.2: The ac power absorbed by the storage capacitor. The shaded region representsthe energy absorbed by the capacitor during one half cycle.

ΔE =Pdc

ω. (3.10)

Now substitute Equation (3.10) into Equation (3.9) and let Vi = VMAX − ΔVr and

Vf = VMAX :

Pdc =1

2Cω

(2VMAXΔVr − ΔV 2

r

). (3.11)

Finally substituting Equation (3.4) into Equation (3.11) for ΔVr yields the final result:

Pdc =√

2VMAXIr − I2r

πfrC. (3.12)

Equation (3.12) is an expression for the maximum dc power one can draw from an ac

source at unity power factor while effectively filtering out the ac ripple power and using

the capacitor to its designed limits.

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 19

3.2 Flyback in steady state

This section goes through the analysis of the flyback converter, which is the first stage in

each phase. This converter will be considered in steady state when it provides constant

power for a dc load at unity power factor. First, the time averaged differential equations

for the converter are found and a solution for the duty cycle is solved for.

3.2.1 Differential equations of the converter

To find the time averaged differential equations of the converter in CCM, the converter

is analyzed in its two possible states, as shown in Figures 3.3 and 3.4.

1:n

CVg

Q1

D1Lm ilV

ig

icim

Figure 3.3: The flyback converter with the main switch, Q1, on.

1:n

CVg

Q1

D1Lm ilV

ig

icim

Figure 3.4: The flyback converter with the main switch, Q1, off.

When the transistor is on (depicted as an ideal switch Q1 in the figure) the voltage

across the magnetizing inductance is vg and its current is ig. The output capacitor current

is simply the load current, il. When the transistor is off, the diode (ideal switch D1 in the

figure) conducts and the voltage across the magnetizing inductance becomes −v/n. The

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 20

output capacitor current is the difference in the current in the magnetizing inductance

reflected to the secondary side minus the load current, im/n−il. The differential equations

representing the system become Equations (3.13) - (3.15).

Ldim (t)

dt=

⎧⎪⎨⎪⎩

vg (t)

−v(t)n

0 < t ≤ d (t) Tsw

d (t)Tsw < t ≤ Tsw

(3.13)

Cdv (t)

dt=

⎧⎪⎨⎪⎩

−il (t)

im(t)n

− il (t)

0 < t ≤ d (t) Tsw

d (t)Tsw < t ≤ Tsw

(3.14)

ig (t) =

⎧⎪⎨⎪⎩

im (t)

0

0 < t ≤ d (t) Tsw

d (t)Tsw < t ≤ Tsw

(3.15)

Averaging these equations over one period yields the large signal time averaged non-

linear differential equations of the flyback converter, shown below.

Ld 〈im (t)〉Ts

dt= d (t) 〈vg (t)〉Ts − (1 − d (t))

〈v (t)〉Ts

n(3.16)

Cd 〈v (t)〉Ts

dt= (1 − d (t))

〈im (t)〉Ts

n− 〈il (t)〉Ts (3.17)

〈ig (t)〉Ts = d (t) 〈im (t)〉Ts (3.18)

3.2.2 The flyback converter in steady state

To obtain the equations for the steady state operation of the flyback converter in CCM,

the small ripple approximation can be applied to Equation (3.16) and the principle of

charge balance to Equation (3.17). This yields the following relationships:

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 21

V

Vg= n

D

(1 − D), (3.19)

IM =nIl

(1 − D). (3.20)

Equation (3.19) can be solved for the duty cycle:

D =V

nVg + V. (3.21)

3.2.3 Control for unity power factor operation

The flyback converter will operate with unity power factor when the input current is in

phase with the input voltage. The duty cycle of the converter can be solved for using

this constraint.

3.2.3.1 Output voltage of the flyback

At unity power factor, the input power is:

Pin (t) = VgIg

(1 + cos (2ωt)

2

). (3.22)

Assuming that the flyback converter is ideal and the downstream converter is pow-

ering a dc load, the power delivered by the flyback is the dc component: VgIg/2. The

second, ac, term is the power that must be absorbed by the filtering elements of the fly-

back. Additionally by noticing that the capacitor has significantly more energy storage

capability than the inductor as shown in Equation (3.23), it will again be assumed that

all of the ac power will be absorbed by the capacitor. This is shown in Equation (3.24).

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 22

LI2L � CV 2 (3.23)

v (t) ic (t) =VgIg cos (2ωt)

2(3.24)

where ic is the current in the capacitor and can be replaced with the differential

equation which governs the behavior of a capacitor as shown in Equation (3.25).

v (t)dv (t)

dtC =

VgIg cos (2ωt)

2. (3.25)

Equation (3.25) is a separable differential equation and can be solved by integration,

resulting in Equation (3.28).

∫v (t) dv =

∫VgIg cos (2ωt)

2Cdt (3.26)

1

2v (t)2 =

VgIg sin (2ωt)

4ωC+

V 20

2(3.27)

v (t) =

√VgIg sin (2ωt)

2ωC+ V 2

0 (3.28)

where V0 is the constant of integration and is the voltage of the capacitor at t = 0.

Equation (3.28) defines the voltage that must exist on the output capacitor of the flyback

converter during unity power factor operation. This equation assumes that all the ac

power is absorbed by this capacitor and the flyback converter is powering a dc load.

3.2.3.2 Duty cycle of the flyback

Combining Equation (3.28) and Equation (3.21), we can find the duty cycle needed to

achieve unity power factor when operating in CCM. The result is shown in Equation

(3.29).

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 23

Dflyback (t) =

√VgIg sin(2ωt)

2ωC+ V 2

0

n |Vg cos (ωt)| +√

VgIg sin(2ωt)2ωC

+ V 20

(3.29)

Using this solution for the duty cycle, the system described by Equations (3.16)

- (3.18) was simulated with the parameters shown in Table 3.1. Note that a small

equivalent series resistance was added to the capacitor for numerical reasons.

Table 3.1: Parameters used to simulate the flyback converter operating at unity powerfactor.

Parameter Value Units

CB 150.00 μFRESR 0.05 ΩLB 7.00 μHfline 60.00 HzPout 25.00 W

The results of the simulation are shown in Figure 3.5 which shows an excellent input

current shape and a total harmonic distortion of 5.1% , validating the duty cycle of

Equation (3.29).

3.2.4 A comment on theory

The derivation in this section relies on Equation (3.21) which was found based on the

assumption that the input voltage and output voltage remain constant. However, this

equation will hold even though the input and output voltage will vary at twice the line

frequency due to the fact that the proposed converter will use a very high switching

frequency, at 400kHz. At this time scale, the input and output voltages will appear

constant to the controller over each switching cycle.

Chapter 3. Capacitor Ripple Voltage and Steady State Analysis 24

0 1/120 1/60

0.70.80.9

Theoretical flyback duty cycle

Time (s)

Dut

y

0 1/120 1/600

50

100Rectified input voltage

Time (s)

Vol

tage

(V

)

0 1/120 1/600

0.5

1Rectified input current

Time (s)

Cur

rent

(A

)

0 1/120 1/6045

50

55Output voltage

Time (s)

Vol

tage

(V

)

Figure 3.5: The simulation results of operating the flyback converter with the duty cyclecalculated in Equation (3.29).

Chapter 4

System Modeling and Control

This chapter investigates duty mode control and illustrates its advantages over conven-

tional control methods for cascaded converters. Following this, the proposed system

is analyzed dynamically and controllers are designed. Finally, some limitations of the

system are presented.

4.1 Duty mode control (DMC)

This section discusses the theory behind DMC. First an intuitive argument for DMC is

presented, and then a state space model of a system is derived. Using this model, DMC

is compared to conventional voltage control. Figure 2.3 shows the block diagram of the

proposed system with DMC, and it is repeated here in Figure 4.1 for convenience.

4.1.1 Advantages of DMC

DMC control is advantageous in two major ways. Firstly, since the duty cycle of the

downstream converter is being controlled instead of the midpoint voltage between the

two converters, a voltage sensor is not required. This will reduce the cost and footprint

of the converter.

25

Chapter 4. System Modeling and Control 26

Centralized DigitalController

1:0.32

Vg LoadC2C1

Q2

Q3

Q1

D1

VrefBuck VoltageCompensator

PWM

Duty ModeController

FlybackCurrent

CompensatorPWM

Dref

Ig

Figure 4.1: Block diagram depicting DMC.

Secondly, DMC control allows for smaller energy storage elements to be used. This

is shown with control theory later in this chapter. However, to motivate this discussion

consider a load step in a system with two converters connected in series. Conventionally,

this is the sequence of events during a load step increase:

1. Load step increase occurs.

2. Voltage on output capacitor drops.

3. Voltage controller of downstream converter compensates by increasing its duty

cycle.

4. Current into the downstream converter increases.

5. Midpoint voltage between converters drops.

6. Voltage controller of upstream converter compensates by increasing the duty cycle.

With DMC a similar load step yields this order of events:

1. Load step increase occurs.

2. Voltage on output capacitor drops.

Chapter 4. System Modeling and Control 27

3. Voltage controller of downstream converter compensates by increasing the duty

cycle.

6. Voltage controller of upstream converter compensates by increasing the duty cycle.

Therefore, the dynamics of the upstream converter (events 4 and 5) are bypassed.

This can be used to help reduce the size of the bulky energy storage capacitor in between

the two converters. This is also extremely advantageous because the upstream converter

will generally have a slower response than the downstream converter.

4.1.2 Two stage DMC example

To simplify the analysis of DMC, a model of two cascaded buck converters is used as

shown in Figure 4.2. In this model, the transistors are modeled with the same on resis-

tance of RAQ and RB

Q for the upstream and downstream converters respectively. This is

a valid assumption because in the prototype developed in the laboratory, the same tran-

sistor was used for the high and low side and each was driven by the same gate source

voltage. The inductors are modeled with internal resistances of RAL and RB

L .

First, a state space model is derived for one of the buck converters, in this case, the

downstream converter. This model is identical to the model for the upstream converter.

Using this model and a state space representation of the downstream controller, the

complete state space model of the system can be built. Equations (4.1) and (4.2) show

the definition of that state space model that is derived.

xB = ABx + BBuB (4.1)

yB = CBx + EBuB (4.2)

To derive the state space model, time averaged switch modeling is employed to lin-

Chapter 4. System Modeling and Control 28

Switching Network LB

RQB RL

B

RQB

CBv1 v2 vB

i1 i2

RBvgA

LA

RQA RL

ARQ

A

CA vA=vgB

iLB

iCB

Figure 4.2: Converter used to illustrate DMC.

earize the switching network as described in [2]. Using the network of Figure 4.2, the

equations for v1, v2, i1 and i2 averaged over one switching period are found, shown in

Equations (4.3) - (4.6).

〈v1 (t)〉Ts = 〈vBg (t)〉Ts (4.3)

〈v2 (t)〉Ts = dB (t)(〈vB

g (t)〉Ts − 〈iBL (t)〉TsRBQ

) − (1 − dB (t)

) (〈iBL (t)〉TsRBQ

)(4.4)

〈i1 (t)〉Ts = dB (t) 〈iBL (t)〉Ts (4.5)

〈i2 (t)〉Ts = 〈iBL (t)〉Ts (4.6)

Equation (4.3) and (4.6) are substituted into Equation (4.4) to get a voltage equation

in terms of switching network parameters only. Similarly, an equation for the input

current is found by dividing Equation (4.5) by (4.6). The results are shown in Equations

(4.7) and (4.8).

〈v2 (t)〉Ts = dB (t) 〈v1 (t)〉Ts − 〈i2 (t)〉TsRBQ (4.7)

〈i1 (t)〉Ts = dB (t) 〈i2 (t)〉Ts (4.8)

Perturbing the equations above yields the linearized equations that describe the con-

verter which is used to generate the state space model. To do so, let all the time varying

Chapter 4. System Modeling and Control 29

terms be represented as a sum of a dc term and an ac term, as shown in Equation (4.9).

The results are shown in Equations (4.10) and (4.11).

x (t) = X + x (4.9)

V2 + v2 = DB (V1 + v1) + dBV1 −(I2 + i2

)RB

Q (4.10)

I1 + i1 = DB(I2 + i2

)+ dBI2 (4.11)

A linearized dc and ac model of a lossy buck converter is built using Equations (4.10)

and (4.11), and is shown in Figure 4.3.

vgB(t)

LB

RQB + RL

B

CB vB(t)iLB(t)

1:DBVg

BBd

ILBBd

ioB(t)

RB

Bgi

Figure 4.3: The linearized model of the buck converter with losses.

From Figure 4.3 the small signal state equations for the inductor current and capacitor

voltage are derived. Setting all dc sources to zero and noting that at dc, V1 = V Bg , these

equations are shown below:

LB diBLdt

= DB vBg + dV B

g − iBL(RB

Q + RBL

) − vB (4.12)

CB dvB

dt= iBL − vB

RB(4.13)

The state space model can be built letting the states, inputs and output be defined

as shown in Equations (4.14), (4.15) and (4.16), respectively. Note that there are two

outputs of this converter. yB1 is the output voltage that is required to control the buck

Chapter 4. System Modeling and Control 30

converter, and yB2 is the input current into the buck converter, which is required in the

interconnection between this converter and the upstream converter in the final model.

The state matrices are shown in Equations (4.17) - (4.20).

xB =

⎡⎢⎣ xB

1

xB2

⎤⎥⎦ =

⎡⎢⎣ iBL

vB

⎤⎥⎦ (4.14)

uB =

⎡⎢⎢⎢⎢⎣

uB1

uB2

uB3

⎤⎥⎥⎥⎥⎦ =

⎡⎢⎢⎢⎢⎣

vBg

iBo

dB

⎤⎥⎥⎥⎥⎦ (4.15)

yB =

⎡⎢⎣ yB

1

yB2

⎤⎥⎦ =

⎡⎢⎣ vB

iBg

⎤⎥⎦ =

⎡⎢⎣ xB

2

dBIBL + iBLDB

⎤⎥⎦ (4.16)

AB =

⎡⎢⎣ −(RB

Q+RBL)

LB−1LB

1CB

−1CBRB

⎤⎥⎦ (4.17)

BB =

⎡⎢⎣

DB

LB 0V B

g

LB

0 −1CB 0

⎤⎥⎦ (4.18)

CB =

⎡⎢⎣ 0 1

DB 0

⎤⎥⎦ (4.19)

EB =

⎡⎢⎣ 0 0 0

0 0 IBL

⎤⎥⎦ (4.20)

4.1.3 DMC model with downstream PID compensator

Using the model developed in the previous section and setting all the loss resistances

(RAQ, RB

Q, RAL , RB

L ) to zero, the entire model to analyze DMC can be built. Figure 4.4

shows the lossless model of the system shown in Figure 4.2 with a PID compensator

added to the downstream converter.

Chapter 4. System Modeling and Control 31

DA

VgA

ILA

AsC1

AsL1

DB

VgB

ILB

BsL1

BsC1

KpB

KiB

KdB s

s1

Agv

AvAdA

oi

Agi

Bgv

BvBd

BoiB

gi

Brefv

5x

Figure 4.4: Complete model of two converters in series to show the properties of DMC.

4.1.4 State space model

The state space model of the system is built based on the linearized block diagram model

of Figure 4.4. The model is defined in Equations (4.21) and (4.22).

x = Ax + Bu (4.21)

y = CDMCx + EDMCu (4.22)

Chapter 4. System Modeling and Control 32

where x and u are the inputs and outputs of the system, respectively, defined by:

x =

⎡⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎣

x1

x2

x3

x4

x5

⎤⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎦

=

⎡⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎣

iAL

vA

iBL

vB

x5

⎤⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎦

(4.23)

u =

⎡⎢⎢⎢⎢⎢⎢⎢⎣

u1

u2

u3

u4

⎤⎥⎥⎥⎥⎥⎥⎥⎦

=

⎡⎢⎢⎢⎢⎢⎢⎢⎣

vAg

iBo

vBref

dA

⎤⎥⎥⎥⎥⎥⎥⎥⎦

(4.24)

Assuming that the derivative of input u3 is zero, the state equations can be found and

are shown in Equation (4.25). This assumption is valid because input u3 is the reference

signal for the downstream converter and is constant during operation.

x =

⎧⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩

−x21

LA + u1DA

LA + u4V A

g

LA

x11

CA + x3

(IBL KB

d

CACB − DB

CA

)+ x4

IBL KB

p

CA − x5KB

i IBL

CA − u2KB

d IBL

CACB − u3IBL KB

p

CA

x2DB

LB − x3KB

d V Bg

CBLB − x4

(1

LB +KB

p V Bg

LB

)+ x5

V Bg KB

i

LB + u2V B

g KBd

CBLB + u3KB

p V Bg

LB

x31

CB − u21

CB

−x4 + u3

(4.25)

For DMC control, the only output that is required is the duty cycle of the downstream

converter. Using y to denote the output of this model, it is found from Figure 4.4 to be:

y = x3−K−dB

CB − x4KBp + x5K

Bi + u2

KBd

CB − u4KBp (4.26)

Chapter 4. System Modeling and Control 33

Using Equations (4.25) and (4.26) the A, B, CDMC and EDMC matrices can be found,

shown in Equations (4.27) - (4.30).

A =

⎡⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎣

0 1LA 0 0 0

1CA 0

(IBL KB

d

CACB − DB

CA

)IBL KB

p

CA −KBi IB

L

CA

0 DB

LB −KBd V B

g

CBLB −(

1LB +

KBp V B

g

LB

)V B

g KBi

LB

0 0 1CB 0 0

0 0 0 −1 0

⎤⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎦

(4.27)

B =

⎡⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎢⎣

DA

LA 0 0V A

g

LA

0 −KBd IB

L

CACB − IBL KB

p

CA 0

0V B

g KBd

CBLB

KBp V B

g

LB 0

0 − 1CB 0 0

0 0 1 0

⎤⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎥⎦

(4.28)

CDMC =

[0 0

−KBd

CB −KBp KB

i

](4.29)

EDMC =

[0

KBd

CB KBp 0

](4.30)

4.1.5 Control to output transfer function

Using the results of the previous section, the control to output transfer function, GDMC ,

can be derived. Using Equation (4.31), GDMC is found and is shown in Equation (4.32).

GDMC (s) =(CDMC (sI − A)−1 B + EDMC

)

⎡⎢⎢⎢⎢⎢⎢⎢⎣

0

0

0

1

⎤⎥⎥⎥⎥⎥⎥⎥⎦

(4.31)

Chapter 4. System Modeling and Control 34

where I is the 5 × 5 identity matrix.

GDMC (s) =dB

dA=

−V Ag DBKB

d

CACBLALB

⎛⎝s2 + s

KBp

KBd

+KB

i

KBd

den (s)

⎞⎠ (4.32)

where,

den (s) = s5 +KB

d V Bg

CBLB s4 +CAV B

g LAKBp −LADBKB

d IBL +CBLA(DB)

2+CBLB+CALA

LACACBLB s3

+KB

d V Bg −IB

L LADBKBp +CAV B

g KBi LA

LACACBLB s2 +1−KB

i IBL LADB+KB

p V Bg

LACACBLB s +V B

g KBi

CALALBCB (4.33)

Comparing this transfer function to a conventional voltage control technique, the

control input remains the same (dA), however the output is the mid-point voltage of the

system, vA. Using the same A and B matrices, the output equation becomes that of

Equation (4.34). Therefore the new C and E matrices are shown in Equations (4.35)

and (4.36).

y = x2 (4.34)

Cc =

[0 1 0 0 0

](4.35)

Ec =

[0 0 0 0

](4.36)

Solving for the conventional transfer function yields:

Gc =vA

dA=

V Ag

CALA

⎛⎝s3 + s2 KB

d V Bg

CBLB + s(1+KB

p V Bg )

CBLB +V B

g KBi

CBLB

den (s)

⎞⎠ (4.37)

where the denominator is given by Equation (4.33).

Chapter 4. System Modeling and Control 35

4.1.6 DMC vs. conventional control

4.1.6.1 Control to output transfer functions

This section will compare the control to output transfer functions of a system using DMC

versus one using conventional output voltage control, as described by Equations (4.32)

and (4.37). Table 4.1 lists the parameters used to compare the two control methods.

The PID voltage controller for the downstream buck converter was designed using the

transfer function method. It was designed to be a fairly fast, but very robust controller

therefore the phase margin is 85.1◦ and the unity gain crossover frequency is 39.2kHz .

Table 4.1: Parameters used to compare DMC and conventional control.Parameter Value Units

CA 0.05 - 100.00 μFLA 0.70 mHDA 0.50V A

g 100.00 VV A 50.00 VCB 47.00 μFLB 4.70 μHDB 0.24V B

g 50.00 VV B 12.00 VKB

p 2.92 × 10−2

KBd 1.00 × 10−6

KiB 150.90

IBo 4.17 A

To illustrate the advantages of DMC, both control to output transfer functions are

plotted on the same graph with normalized dc gains, as shown in Figure 4.5(a). The plot

depicts the system with a large midpoint capacitance, of 100.0μF . As this capacitance

decreases, the normalized gain plot of the system changes dramatically, as shown in

Figure 4.5(b). The capacitance value in this case has been reduced to 0.05μF . The

transfer function representing the conventional control approach begins to develop a

large resonant peak at around 65kHz.

Chapter 4. System Modeling and Control 36

Application of the Nyquist criterion shows that instability will result if loop gain at

the secondary resonant frequency exceeds unity. This constrains controller design and

limits the available bandwidth. For this comparison, the DMC approach offers a 5.8dB

higher gain margin, thus allowing higher feedback gain and providing a faster response

to a disturbance.

101

102

103

104

105

106

−160

−140

−120

−100

−80

−60

−40

−20

0

20

40

Frequency (Hz)

Mag

nitu

de (

dB)

ConventionalDMC

(a) CA1 = 100µF

101

102

103

104

105

106

−100

−80

−60

−40

−20

0

20

Frequency (Hz)

Mag

nitu

de (

dB)

ConventionalDMC

(b) CA1 = 0.05µF

Figure 4.5: Gains of the control to output transfer functions of DMC and conventionalcontrol.

Another property of these transfer functions is the steeper slope at high frequencies,

seen in both Figures 4.5(a) and 4.5(b), that DMC exhibits. This makes the DMC system

more robust to noise.

4.1.6.2 Simulation results

Figure 4.6 shows the simulation results of a reference voltage step at the output of the

linearized state space model of two cascaded lossy buck converters using conventional

control and DMC. For both control methods, the same controller was used to control the

downstream converter and the size of the mid-point capacitor in between the converters

was 0.05μF . The upstream controllers were designed using the normalized bode plots of

the system, and both controllers had the same zero. Therefore, the compensated bode

plots of each system had the same dc gain.

Chapter 4. System Modeling and Control 37

0 0.05 0.1 0.15 0.2 0.25 0.30

0.2

0.4

0.6

0.8

1

1.2

1.4

Time (s)

Vol

tage

(V

)

ConventionalDMC

Figure 4.6: The output voltage of two cascaded converters in response to a voltage stepreference command controlled conventionally and with DMC.

As shown in Figure 4.6, the output voltage of the DMC system reaches the new

reference voltage more quickly than the system using conventional control. The DMC

system reached 63% of the new reference step 3.47 times faster than the conventionally

controlled system. These results are even better than might be predicted from the Bode

plot analysis. This is because the faster DMC response increases the mid-point voltage

and therefore increase the voltage across the inductor on the downstream stage, allowing

its voltage to increase more rapidly than the system under conventional control.

4.1.6.3 Discussion

This section has merely presented one example showing the benefits of DMC control

for cascaded converters. Although limited, the examples in Sections 4.1.6.1 and 4.1.6.2

illustrate its significant advantages for systems with both a small and large energy storage

capacitor. DMC has opened new avenues for high bandwidth two stage converters with

minimal energy storage. However, to fully explore DMC, a more general analysis should

be performed, which is out of the scope of this work.

Chapter 4. System Modeling and Control 38

4.2 System models

This section derives state space models of the proposed system. State space was chosen

to simplify the process of combining converter models together as controllers are designed

and added to the system. Using these models, the appropriate transfer functions will be

extracted and then controllers will be designed using the transfer function method as

described in [2] and direct digital redesign as described in [31].

4.2.1 Lossy buck converter in state space

Figure 4.7 shows the model of the lossy buck converter that is used for controller design.

Its state space model was derived in Section 4.1.2 and is described by Equations (4.17)

- (4.20).

Switching Network

VgB

LB

RQB RL

B

RQB

CBv1 v2 VB

i1 i2

RB

Figure 4.7: The buck converter with losses and switching network shown.

4.2.2 Lossy flyback converter in state space

A state space representation of a lossy flyback converter is derived based on Figure 4.8.

As shown in the figure, numerous losses are taken into account. RAQ is the on resistance

of the transistor Q1, RAL is the resistance of magnetizing inductance, RA

C is the equivalent

series resistance of the capacitor CA1 , RA

s is the sense resistor and V AD is the voltage drop

across the diode.

Chapter 4. System Modeling and Control 39

vgA

RLA

LA ioA

VDA

RQA

D1

Q1

1:n

RsA

RCA

CA

AoviL

A

igA

Figure 4.8: The flyback converter with losses.

Due to the complexity of the model, a different approach from the previous section will

be taken to obtain a linearized state space model. The state space averaging technique

will be employed as described in [2], [32]. This technique averages the entire circuit over

one switching cycle, not just the switching components, as it is in the time averaged

switch model.

To begin, let the states, inputs and outputs be defined by Equations (4.38), (4.39)

and (4.40), respectively.

Chapter 4. System Modeling and Control 40

xA =

⎡⎢⎣ xA

1

xA2

⎤⎥⎦ =

⎡⎢⎣ iAL

vA

⎤⎥⎦ (4.38)

uA =

⎡⎢⎢⎢⎢⎣

uA1

uA2

uA3

⎤⎥⎥⎥⎥⎦ =

⎡⎢⎢⎢⎢⎣

vAg

vAD

iAo

⎤⎥⎥⎥⎥⎦ (4.39)

yA =

⎡⎢⎢⎢⎢⎣

yA1

yA2

yA3

⎤⎥⎥⎥⎥⎦ =

⎡⎢⎢⎢⎢⎣

iAL

iAg

vAo

⎤⎥⎥⎥⎥⎦ (4.40)

Let matrices AA1 , BA

1 , CA1 and EA

1 represent the system during the first half of the

switching cycle, and matrices AA2 , BA

2 , CA2 and EA

2 represent the system during the

second half of the switching cycle. Averaging the circuit over one switching cycle yields

the non linear state equations:

⎡⎢⎣ LA 0

0 CA

⎤⎥⎦ dxA (t)

dt=

(AA

1 xA (t) + BA1 uA (t)

)dA (t)

+(AA

2 xA (t) + BA2 uA (t)

) (1 − dA (t)

)(4.41)

yA (t) =(CA

1 xA (t) + EA1 uA (t)

)dA (t) +

(CA

2 xA (t) + EA2 uA (t)

) (1 − dA (t)

)(4.42)

Define the matrix ZA by Equation (4.43) and replace each time dependent term in

Equations (4.41) and (4.42) with a dc component and an ac component as shown in

Equation (4.9). Eliminating second order terms yields the linearized state space model

Chapter 4. System Modeling and Control 41

of the system, shown in Equations (4.44) and (4.45).

ZA =

⎡⎢⎣ LA 0

0 CA

⎤⎥⎦ (4.43)

ZAdxA

dt= AAxA + BAuA + FAdA (4.44)

yA = CAxA + EAuA + GAdA (4.45)

where:

FA =((

AA1 −AA

2

)XA +

(BA

1 −BA2

)UA

)(4.46)

GA =((

CA1 −CA

2

)XA +

(EA

1 − EA2

)UA

)(4.47)

AA = DAAA1 +

(1 − DA

)AA

2 (4.48)

BA = DABA1 +

(1 − DA

)BA

2 (4.49)

CA = DACA1 +

(1 − DA

)CA

2 (4.50)

EA = DAEA1 +

(1 − DA

)EA

2 (4.51)

In the above equations (Equations (4.46) - (4.51)), vectors XA and UA represent the

dc states and inputs respectively.

It can be shown that the dc value of the states and outputs can be calculated using

Equations (4.52) and (4.53).

XA = − (AA

)−1BAUA (4.52)

YA =(−CA

(AA

)−1BA + EA

)UA (4.53)

Chapter 4. System Modeling and Control 42

where the dc inputs are defined by:

UA =

⎡⎢⎢⎢⎢⎣

V Ag

V AD

IAo

⎤⎥⎥⎥⎥⎦ . (4.54)

Using Figure 4.8, the state equations for both parts of the switching cycle can be

written. Beginning with the first part of the switching cycle when transistor Q1 is on,

the state and output equations are shown in Equations (4.55) - (4.59).

LA dxA1

dt= uA

1 − xA1

(RA

L + RAQ

)(4.55)

CA dxA2

dt= −uA

3 (4.56)

yA1 = xA

1 (4.57)

yA2 = xA

1 (4.58)

yA3 = xA

2 − uA3 RA

C (4.59)

From these equations, state matrices can be derived, and are shown in Equations

(4.60) - (4.63).

Chapter 4. System Modeling and Control 43

AA1 =

⎡⎢⎣ − (

RAL + RA

Q

)0

0 0

⎤⎥⎦ (4.60)

BA1 =

⎡⎢⎣ 1 0 0

0 0 −1

⎤⎥⎦ (4.61)

CA1 =

⎡⎢⎢⎢⎢⎣

1 0

1 0

0 1

⎤⎥⎥⎥⎥⎦ (4.62)

EA1 =

⎡⎢⎢⎢⎢⎣

0 0 0

0 0 0

0 0 −RAC

⎤⎥⎥⎥⎥⎦ (4.63)

For the second part of the switching cycle diode D1 conducts and the state and output

equations are shown in Equations (4.64) - (4.68).

LA dxA1

dt=

−1

n

(uA

2 +(

xA1

n− uA

3

)RA

C + xA2 +

xA1 RA

s

n

)− RA

LxA1 (4.64)

CAdxA

2

dt=

xA1

n− uA

3 (4.65)

yA1 = xA

1 (4.66)

yA2 = 0 (4.67)

yA3 = xA

2 +

(xA

1

n− uA

3

)RA

C (4.68)

The state matrices for the second part of the switching cycle can be written:

Chapter 4. System Modeling and Control 44

AA2 =

⎡⎢⎣

(−1n2

(RA

C + RAs

) − RAL

) −1n

1n

0

⎤⎥⎦ (4.69)

BA2 =

⎡⎢⎣ 0 −1

n

RAC

n2

0 0 −1

⎤⎥⎦ (4.70)

CA2 =

⎡⎢⎢⎢⎢⎣

1 0

0 0

RAC

n1

⎤⎥⎥⎥⎥⎦ (4.71)

EA2 =

⎡⎢⎢⎢⎢⎣

0 0 0

0 0 0

0 0 −RAC

⎤⎥⎥⎥⎥⎦ (4.72)

Using Equations (4.60) - (4.63) and (4.69) - (4.72), the matrices required for the ac

state space model of Equations (4.44) and (4.45) are found and shown in Equations (4.73)

- (4.78).

Chapter 4. System Modeling and Control 45

AA =

⎡⎢⎣ DA

(−RAL − RA

Q

)+

(1 − DA

) (−1n2

(RA

C + RAs

) − RAL

) −(1 − DA)/n

(1−DA)n

0

⎤⎥⎦ (4.73)

BA =

⎡⎢⎣ DA −(1−DA)

n

(1−DA)RAC

n2

0 0 −1

⎤⎥⎦ (4.74)

FA =

⎡⎢⎣

−(DAV Ag +IA

o RALn+nIA

o RAQ−V A

g )(−1+DA)2

1(−1+DA)IA

o

⎤⎥⎦ (4.75)

CA =

⎡⎢⎢⎢⎢⎣

1 0

DA 0

RAC

(1 − DA

)1

⎤⎥⎥⎥⎥⎦ (4.76)

EA =

⎡⎢⎢⎢⎢⎣

0 0 0

0 0 0

0 0 RAC

⎤⎥⎥⎥⎥⎦ (4.77)

GA =

⎡⎢⎢⎢⎢⎣

0

−n(−1+DA)IA

o

RACnIA

o

(−1+DA)

⎤⎥⎥⎥⎥⎦ (4.78)

4.2.3 Additional parts of the system model

In addition to state space models of the converters, transfer functions must be defined

to complete the system model. They are described below.

4.2.3.1 Additional gain in current loop

Since the flyback current controller will be acting as a PFC in this system, it must track

the input current. From the ideal large signal model of the flyback converter, the input

current and inductor current are related as shown in Equation (3.18), repeated below for

Chapter 4. System Modeling and Control 46

convenience:

⟨iAg (t)

⟩Ts

= d (t)⟨iAL (t)

⟩Ts

(4.79)

However, in the proposed system, the inductor current will be measured on the sec-

ondary side. Thus an additional factor of n from the turns ratio of the transformer must

also be added, resulting in Equation (4.80).

⟨iAg (t)

⟩Ts

= nd (t)⟨iAL (t)

⟩Ts

(4.80)

This gain will be incorporated into the loop gain of the current controller to deduce the

input current from the measured current. It is important to include this value (instead

of absorbing it into the controller) because while the converter is operating as a PFC,

the duty cycle will be varying considerably as shown in Section 3.2.3.

4.2.3.2 Additional components used in digital control

As stated in Section 2.4, digital techniques will be used to implement the controller.

Therefore, a digital pulse-width modulator (DPWM) block and an analog to digital

converter (ADC) block must be modeled in continuous time. Both of these models can

be found in [23], and are repeated below:

Gdpwm (s) =1

Ldpwme−sTdpwm (4.81)

Gadc (s) =

(1 − 2−nadc

Vmaxadc

)e−sTadc (4.82)

where Lpwm is the number of discrete steps in the DPWM, Tpwm is the period of the

DPWM, nadc is the number of bits of the ADC , Vmaxadcis the maximum input voltage

into the ADC and Tadc is the update period of the ADC.

Chapter 4. System Modeling and Control 47

However, since the dynamics of the system that we are interested in are much slower

than the switching period, the analog to digital converter and the digital pulse width

modulator will be approximated with gains as shown in Equations (4.83) and (4.84).

Gdpwm (s) ≈ 1

Ldpwm

= Kdpwm (4.83)

Gadc (s) ≈ 1 − 2−nadc

Vmaxadc

= Kadc (4.84)

4.2.3.3 Digital filter

To control the midpoint voltage of the converter, DMC control is implemented. However,

before the duty cycle of the buck converter can be fed into the voltage loop of the flyback

converter, it must be filtered. This is because a large ripple will appear on the duty cycle

as a consequence from the large ripple voltage on the midpoint capacitor. The filter

is implemented digitally as an eight point moving average filter, operating at 480Hz.

However, in continuous time it will be modeled as a second order filter for simplicity, as

shown in Equation (4.85).

Gf (s) =1

1 +Qf s

ωf+ s2

ω2f

, ωf = 2π30, Qf = 1 (4.85)

4.2.3.4 State space representation of controller

In order to combine the flyback and buck converter models to find an open loop transfer

function that can be used to design the DMC controller, the voltage and current con-

trollers of the buck and flyback converters are represented in state space to simplify the

integration process. The general form of a PI controller in state space is shown in Figure

4.9.

From this figure the state matrices can be found and are described in Equations (4.86)

- (4.88).

Chapter 4. System Modeling and Control 48

p

is1

Figure 4.9: A PI controller in state space.

API = [0] (4.86)

BPI = [1] (4.87)

CPI = [Ki] (4.88)

EPI = [Kp] (4.89)

4.2.4 Complete system model in state space

Using the models built in Sections 4.2.1, 4.2.2 and 4.2.3, the complete small signal system

model can be built, and it is shown in Figure 4.10.

ZAxA = AAxA + BAuA + FAdyA = CAxA + DAuA + GAd

Flyback ConverterxB = ABxB + BBuB

yB = CBxB + DBuB

Buck Converter

GvB(s)

GvA(s)Gi

A(s)

Agv

DBref

VBref

VgA

u1A

u3A

u1B

u2B

y3A

y1A

y1B

y2B

Kadc2

Kadc1

Kadc3

KdpwmA Kdpwm

B

Gf(s)

nDA

dA

kA dB

Figure 4.10: The complete small signal model of the system.

In order to be able to design a controller for DMC controller, the control to output

transfer function must be extracted from the model of Figure 4.10. To obtain this transfer

function, the ASYS, BSYS, CSYS and ESYS state matrices of the system are derived.

Chapter 4. System Modeling and Control 49

This uses the state space models of the lossy buck, lossy flyback and controllers already

created. Using Equation (4.31), the transfer function from input kA to output dB (as