176 String Recognizer Example n Recognize the string: 1011 n Input: 1 0 0 1 0 1 1 0 1 1 0 0 1 0 n...

-

Upload

lee-bennett -

Category

Documents

-

view

224 -

download

3

Transcript of 176 String Recognizer Example n Recognize the string: 1011 n Input: 1 0 0 1 0 1 1 0 1 1 0 0 1 0 n...

1

String Recognizer Example

Recognize the string: 1011

Input: 1 0 0 1 0 1 1 0 1 1 0 0 1 0 Output:

State Machine:

2

String Recognizer Example (cont.)

State Table:

3

String Recognizer Example (cont.)

Implementation:

4

FSMs & Flip Flops

Sometimes may be more efficient to implement FSM with other Flip Flops that Dff

Approach: Given state table & Flip Flop Excitation table,

determine how to use Flip Flop for this circuit

Present State Input Next State J K Output0 0 0 00 1 1 11 0 1 11 1 0 0

J-K Excitation Table:

5

Parity with J-K (cont.)

Implementation:

6

Parity with T

T Excitation Table:

Present State Input Next State T Output0 0 0 00 1 1 11 0 1 11 1 0 0

7

Vending Machine with J-K

J-K Excitation Table:

8

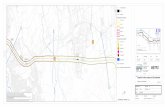

FSM Word Problem: Traffic Light ControllerA busy highway is intersected by a little used farmroad. DetectorsC sense the presence of cars waiting on the farmroad. With no caron farmroad, light remain green in highway direction. If vehicle on farmroad, highway lights go from Green to Yellow to Red, allowing the farmroad lights to become green. These stay green only as long as a farmroad car is detected but never longer than a set interval. When these are met, farm lights transition from Green to Yellow to Red, allowing highway to return to green. Even if farmroad vehicles are waiting, highway gets at least a set interval as green.

Assume you have an interval timer that generates a short time pulse(TS) and a long time pulse (TL) in response to a set (ST) signal. TSis to be used for timing yellow lights and TL for green lights.

9

Traffic Light Controller (cont.)Picture of Highway/Farmroad Intersection:

Highway

Highway

Farmroad

Farmroad

HL

HL

FL

FL

C

C

10

Traffic Light Controller (cont.)

• Tabulation of Inputs and Outputs:

Input SignalresetCTSTL

Output SignalHG, HY, HRFG, FY, FRST

Descriptionplace FSM in initial statedetect vehicle on farmroadshort time interval expiredlong time interval expired

Descriptionassert green/yellow/red highway lightsassert green/yellow/red farmroad lightsstart timing a short or long interval

• Tabulation of Unique States: Some light configuration imply others

StateS0S1S2S3

DescriptionHighway green (farmroad red)Highway yellow (farmroad red)Farmroad green (highway red)Farmroad yellow (highway red)

11

Traffic Light Controller (cont.)

State Diagram

12

Traffic Light Controller (cont.)

State Table using J-K Flip Flops

13

Registers

Storage unit. Can hold an n-bit value Composed of a group of n flip-flops

Each flip-flop stores 1 bit of information

Normally use D flip-flopsD Q

Dffclk

D QDffclk

D QDffclk

D QDffclk

14

Controlled RegisterReset Load Action0 0 Q = old Q1 0 Q = 00 1 Q = D

D QDffclk

D QDffclk

D QDffclk

D QDffclk

15

Shift Register

Register that shifts the binary values in one or both directions

D QDffclk

D QDffclk

D QDffclk

D QDffclk

In Out

Clock

16

Transfer of Data

2 modes of communication: Parallel vs. Serial Parallel: all bits transferred at the same time Serial: one bit transferred at a time

Shift register can be used for serial transfer

D QDffclk

D QDffclk

17

Shift Register w/Parallel LoadShift Load Action0 0 Q = old Q1 0 ShiftX 1 Parallel Load

D QDffclk

D QDffclk

D QDffclk

D QDffclk

18

Bidirectional Shift Register w/Parallel LoadShift Load Action0 0 Q = old Q0 1 Parallel Load1 0 Shift Up (V*2)1 1 Shift Down (V/2)

D QDffclk

D QDffclk

D QDffclk

D QDffclk

19

Conversion between Parallel & Serial

D3 Q34-bit

D2 Q2Shift

D1 Q1Reg.

D0 Q0Shift Load Clk

D3 Q34-bit

D2 Q2Shift

D1 Q1Reg.

D0 Q0Shift Load Clk

LSI LSI

20

Counters

A reg. that goes through a specific state sequence n-bit Binary Counter: counts from 0 to 2N-1 in binary Up Counter: Binary value increases by 1 Down Counter: Binary value decreases by 1 3-bit binary up counter state diagram:

21

Binary Up-Counter Imp. (D Flip-Flop)

22

Binary Up-Counter Imp. (T Flip-Flop)

23

Complex Binary CounterLoad Count Action0 0 Q = old Q0 1 Up Count1 0 Reset1 1 Load Parallel

24

Arbitrary Sequence Counters

Design a 3-bit count that goes through the sequence 000->010->100->101->111->110->001->011->000->...

25

Memory

Need method for storing large amounts of data Computer programs, data, pictures, etc.

RAM: Random Access Memory, Read/Write ROM: Read-only Memory

Address Data000000 00111110000001 01101011000010 01011101000011 01100011000100 00111110000101 00000000000110 11111111000111 01010101001000 10101010001001 00100001001010 11011010

64x8 RAM

A3 D7A2 D6A1 D5A0 D4 D3 D2 D1Write D0

26

8x4 RAM

000

001

010

011

100

101

110

111

3:8Decoder

Enable

S2 S1 S0

A2A1A0

In3 In2 In1 In0

Out3 Out2 Out1 Out0

Write

27

RAM Cell

Requirements: Store one bit of data Change data based on input when row is selected

S QR

Input

Row Select

28

RAM Expansion

Implement a big RAM from multiple small RAMSD15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0Address

0000000

0010000

0100000

0110000

1000000

1010000

1100000

1110000

29

RAM Expansion (cont)

Build a 16x16 RAM from 16x4 RAMs

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

30

RAM Expansion (cont)

Build a 32x16 RAM from 16x4 RAMs

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

16x4 RAMA3 DinA2 A1 DoutA0

Write

![Notas de Aula · n], 0 ≤ n ≤ M = 2 n d = N − 1 0, ... 1, 0 ≤ n ≤ M = N − 1 0, caso contrario Filtros Digitais tipo FIR 4 Resposta impulsiva - ... somat´oria do meio,](https://static.fdocuments.in/doc/165x107/5c5b9d7609d3f236368c090b/notas-de-aula-n-0-n-m-2-n-d-n-1-0-1-0-n-m-.jpg)

![Martin Ric - University of Cambridge · JK Flip Flop jkff(0, J, K, Q, Q). jkff(1, 0, Q, Q). jkff(1, 0, 1, Q, 0). jkff(1, 1, 0, Q, 1). jkff(1, 1, 0, 1). jkff(1, 1, 0). list(N, N, [N]).](https://static.fdocuments.in/doc/165x107/6001bff80d12250fcd4a288b/martin-ric-university-of-cambridge-jk-flip-flop-jkff0-j-k-q-q-jkff1-0.jpg)