Xilinx IEEE802-Compatible Viterbi Decoder v1 · PDF file• Viterbi Decoder, jointly ......

Transcript of Xilinx IEEE802-Compatible Viterbi Decoder v1 · PDF file• Viterbi Decoder, jointly ......

Features Viterbi Decoder, jointly

developed by L-3 Communications and Xilinx, reaches OC3 (155Mbps) data rates and higher

Available for all Virtex, Virtex-E, Virtex-II, Virtex-II Pro, Virtex-4, Spartan-II, Spartan-IIE, and Spartan-3 FPGAs

Industry-standard constraint length 7, (G0,G1)=(171,133) or (133,171) compatible with Q1900, DVB, IEEE802.11a, IEEE802.16a, HiperAccess, HiperMan, INTELSAT IESS-308/309

Adaptive rate change via puncturing interface

Best state logic in traceback reduces latency andimproves Bit Error Rate (BER) up to 0.65dB at rate7/8; necessary for TDMA burst modems using highcode rates.

Parameterizable options for soft data input, accumulated path metric, and best state widths

Fully synchronous one-clock version (Viterbi1x, see Figure 2) for adaptive traceback length up to 126

Fully synchronous 2x clock version (Viterbi2x, see Figure 2) for reduced latency, lower power dissipation, and half Block RAM size; with adaptive traceback length of 48 or 96

The Viterbi2x version has a 29 clock latency for IEEE802.11a PLCP header 24-bit SIGNAL symbol using zero-tail termination control signals

Normalization output for synchronization and indication of data link SNR

Viterbi2x supports BER monitor

Alternative branch metric inputs for Pragmatic Trellis Coded Modulation (PTCM)

Erasure capability of framing/synchronization patterns

VHDL source code or netlist distribution with VHDL channel model for BER simulation

Incorporates Xilinx Smart-IP technology for maximum performance

0

IEEE802-CompatibleViterbi Decoder v1.1

DS204 November 10, 2004 0 0 Product Specification

LogiCORE Facts

Core Specifics

Supported Device Family

Virtex, Virtex-E, Virtex-II, Virtex-II Pro, Virtex-4, Spartan-II, Spartan-IIE, Spartan-3

Resources Used See Table 9 and Table 9

Special Features RPM Core

Provided with Core

Documentation Product Specification

Design File Formats VHDL and EDIF

Constraints File UCF

Verification VHDL Testbench

Instantiation Template VHDL Wrapper

Reference Designs & application notes

None

Additional Items None

Design Tool Requirements

Xilinx Implementation Tools

ISE 6.1.03i or later

Verification ModelSim PE 5.4e

Simulation ModelSim PE 5.4e

Synthesis Synplify Pro 7.1

Support

Support provided by Xilinx, Inc.

DS204 November 10, 2004 www.xilinx.com 1Product Specification

2004 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at http://www.xilinx.com/legal.htm. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature, application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may require for your implemen-tation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties or representations that this imple-mentation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

www.xilinx.comhttp:www.xilinx.com/legal.htmhttp://www.xilinx.com/legal.htmhttp://www.xilinx.com/legal.htm

IEEE802-Compatible Viterbi Decoder v1.1

2

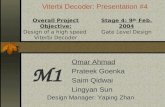

Figure Top x-ref 1

Figure 1: Virtex2x Decoder VHDL Interface Signals

Figure Top x-ref 2

Figure 2: Viterbi1x Decoder VHDL Interface Signals

xip2120

L16tcmidata(widthd-1:0)qdata(widthd-1:0)ieraseqeraseerasenbvs0_nvs1_ntbs0

hdenc0hdenc1h00_tcm(widthd:0)h01_tcm(widthd:0)h10_tcm(widthd:0)h11_tcm(widthd:0)secin[3:0]

resetceclkclk2

tbdoutenaout

nrmihard

qhard

secout[3:0]tbd1outtbqout

xip2119

tblength[6:0]tcmidata(widthd-1:0)qdata(widthd-1:0)ieraseqeraseerasenbvs0_nvs1_n

h00_tcm(widthd:0)h01_tcm(widthd:0)h10_tcm(widthd:0)h11_tcm(widthd:0)

resetceclk

tbdout

nrm

www.xilinx.com DS204 November 10, 2004Product Specification

www.xilinx.com

IEEE802-Compatible Viterbi Decoder v1.1

DS204 NovProduct Sp

Functional DescriptionThe core implements a Viterbi Decoder for decoding convolutionally encoded data. The basic architec-ture of a convolutional encoder is shown in Figure 6. In the convolutional encoder, the incoming data isbrought into the constraint register a bit at a time. The two required output bits are then generated bymodulo-2 addition of the required bits from the constraint register. The bits to be XORed are selected bythe convolutional codes as shown in Figure 6. The Viterbi core decodes the data generated by the con-volutional encoder that has a constraint length k=7 and the two generator polynomials G0=171 andG1=133 as shown in Figure 6. Simply swapping idata and qdata inputs allows the same Viterbi decodercore to decode data encoded with generator polynomials G0=133 and G1=171. The Viterbi core has afully parallel architecture, which provides fast data throughput. The core also supports puncturingrates n/(n+1) through an external interface that generates the signals vs0_n and vs1_n. Puncturinggives a large range of transmission rates and reduces the bandwidth requirement on the channel. Seethe Puncturing section. The decoder core consists of three main blocks as shown in Figure 7.

Branch Metric Calculation

The first block is the Branch Metric Unit (BMU). This module costs the incoming data using a Euclideanmetric. The incoming data is soft coded with a parameterizable bit width that can be set to any value.It is possible to bypass the BMU with external PTCM branch metrics. The data format of the Viterbi coreis offset binary. The conversion between offset two's complement and offset binary is shown in Table 1.For offset two's complement, the analog signal midpoint is between 000 and 111. For offset binary, theanalog signal midpoint is between 011 and 100. Even though the soft data representation is offset; thisdoes not imply the analog input signal should have any DC offsets. Any analog signal DC offset beforeconversion to soft data inputs will result in reduced BER and higher normalization rates, and thusshould be avoided.

Add Compare Select

The second block in the decoder is the Add Compare Select unit (ACS). This module selects the optimalpath to each state in the Viterbi trellis (survival path). Figure 8 shows one stage in the Viterbi trellis fora constraint length 3 decoder. The ACS module decodes for each state in the trellis, thus for a constraintlength 7 decoder that has 64 states there are 64 sub-blocks in the ACS block. See the section on CoreResource Utilization for further characterization of the decoder. The ACS has a Best State Calculation

Table 1: Data Format for Soft Width 3

Offset Twos Complement Offset Binary

Strongest 0 011 000

010 001

001 010

Weakest 0 000 011

Weakest 1 111 100

110 101

101 110

Strongest 1 100 111

ember 10, 2004 www.xilinx.com 3ecification

www.xilinx.com

IEEE802-Compatible Viterbi Decoder v1.1

4

(BSC) module which finds the state with the smallest accumulated path metric to start each tracebackblock.

The BSC module output, used in traceback, improves BER up to 0.65dB for rate 7/8 compared to Qual-comm Q1900 in continuous mode; improvement is greater for burst operation. Generic Viterbi decod-ers without a BSC module require longer traceback lengths to achieve equivalent BER performance.Increasing traceback lengths results in increased Viterbi decoder latency, which is unacceptable inmany burst/TDMA applications. In applications with high code rates, the BSC module again is funda-mental in reducing traceback length for any given BER and latency requirement. If latency and trace-back length are not critical requirements, the BSC module can be removed for substantial size savings,as described in the core utilization section.

For applications like IEEE802.11a with zero-tail packet termination, the input control signal tbs0 allowsthe user to bypass BSC output for the last block in the packet and substitute zero state address insteadof best state address. This combination of zero state for the last block and best state addresses for allother blocks in the packet reduces latency and provides higher BER performance for other blocks in thepacket.

Traceback

The third block in the decoder is the traceback module (see Figure 7). This module finds the optimalpath through the Viterbi trellis by tracing through a fixed number of ACS results. For the two-clock ver-sion, the recommended traceback length is 48 for non-punctured codes and 96 for punctured codes. Forthe one-clock version, the traceback length can be up to 126 for Virtex-II but is limited to 62 for non Vir-tex-II families. The traceback block is implemented in block RAM. For additional details, see the CoreResource Utilization section.

Figure Top x-ref 3

Figure 3: Convolutional Encoder of Constraint Length 7

www.xilinx.com DS204 November 10, 2004Product Specification

www.xilinx.com

IEEE802-Compatible Viterbi Decoder v1.1

DS204 NovProduct Sp

Puncturing

Data can be punctured prior to transmission. The convolutional encoder is always a rate encoder, 2bits output for every 1 bit input. After encoding, certain bits of the rate encoded data are punctured(or deleted) and not tr