Wafer Cut and Rotation to Improve the Compound yield for 3D Wafer-on-Wafer Stacking Bei Zhang

description

Transcript of Wafer Cut and Rotation to Improve the Compound yield for 3D Wafer-on-Wafer Stacking Bei Zhang

Wafer Cut and Rotation to Improve the Compound yield for 3D Wafer-

on-Wafer StackingBei Zhang

Department of Electrical and Computer EngineeringAuburn University, AL 36849 USA

Thesis Advisor: Dr. Vishwani D. AgrawalThesis Committee: Dr. Victor Nelson

Dr. Adit Singh Dr. Charles Stroud

Presentation Outline Introduction Problem Statement Previous efforts Our efforts

Proposed a hybrid wafer stacking procedure Proposed a new wafer manipulation method Exploited more defect models Die per sector calculator

Experimental results Future work

Pollution elimination Find the optimal number of cuts

Conclusion

Apr. 10, 2013 Bei’s General exam 2

3

Introduction

What’s 3D IC?

A chip in which two or more layers of active electronic components are integrated horizontally or vertically into

a single circuit.

Apr. 10, 2013 Bei’s General exam

Wikipedia: http://en.wikipedia.org/wiki/Three-dimensional_integrated_circuit

4

Introduction

3D IC basic structure:

Apr. 10, 2013 Bei’s General exam

Through silicon Via (TSV)

Introduction

3D Packaging?

3D transistor?

In 3D packaging, separate chips are stacked in a single package. However, these chips are not integrated into a single circuit.

Apr. 10, 2013 Bei’s General exam 5

Introduction

Why 3D IC?

TSV connect the planar wafer in the vertical direction. This reduces the need for long wires which in turn reduces the delay and power consumption.

Heterogeneous integration.

Reduced foot-print size, desirable in hand-held devices.

Apr. 10, 2013 Bei’s General exam 6

Introduction

3D IC fabrication methods:

Die on Die stacking (D2D) Die on Wafer stacking (D2W) Advantages : Higher yield, can stack only known good dies Disadvantages: 1) Hard to handle and stack, Process expensive

2) Low throughput 3) May not applicable to high-end systems Wafer on Wafer stacking (W2W) Advantages : 1) Highest throughput 2) Allows for highest TSV density Disadvantages: Low compound stacking yield

Apr. 10, 2013 Bei’s General exam 7

Introduction

Why compound yield loss in W2W stacking?

Bottom layer

Stack

Bad

Good

Bottom layer Top layer

Apr. 10, 2013 Bei’s General exam 8

Introduction

Wafers versus Layers in 3D W2W stacking

Bottom layer

M. Taouil, S. Hamdioui, J. Verbree, and E. Marinissen, “On Maximizing the compound yield for 3D wafer-to-wafer stacked IC," in Proc. International Test Conf., 2010, pp. 1-10.

Apr. 10, 2013 Bei’s General exam 9

Presentation Outline Introduction Problem Statement Previous efforts Our efforts

Proposed a hybrid wafer stacking procedure Proposed a new wafer manipulation method Exploited more defect models Die per sector calculator

Experimental results Future work

Pollution elimination Find the optimal number of cuts

Conclusion

Apr. 10, 2013 Bei’s General exam 10

Problem Statement

• Conditions:• N number of repositories each with K wafers • Fault maps for all wafers based on pre-bond testing• A production size of M 3D ICs

• Objective:• Maximize the overall compound yield OR• Maximize the overall number of good 3D ICs

Apr. 10, 2013 Bei’s General exam 11

Presentation Outline Introduction Problem Statement Previous efforts Our efforts

Proposed a hybrid wafer stacking procedure Proposed a new wafer manipulation method Exploited more defect models Die per sector calculator

Experimental results Future work

Pollution elimination Find the optimal number of cuts

Conclusion

Apr. 10, 2013 Bei’s General exam 12

Previous Efforts

Exploiting different repository replenishment schemes

Exploiting various matching algorithms

Exploiting different matching criteria

Exploiting more practical defect models

Specifically design wafers for matching

Apr. 10, 2013 Bei’s General exam 13

Repository replenish schemes can be: Static Repository

• None of the repositories will be replenished until they run out of wafers.

Running Repository• Each repository is immediately replenished with a new

wafer each time a wafer is selected.

Different Repository Schemes

M. Taouil, S. Hamdioui, J. Verbree, and E. J. Marinissen, “On Maximizing the compound yield for 3D wafer-to-wafer stacked IC," in Proc. International Test Conf., 2010, pp. 1-10.

Apr. 10, 2013 Bei’s General exam 14

15

Matching algorithms based on Static repository:

Matching Algorithms

S. Reda, G. Smith, and L. Smith, “Maximizing the Functional Yield of Wafer-to-Wafer 3-D Integration,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 17, no. 9, pp. 1357–1362, Sept. 2009.

Globally greedy matching

Iterative matching heuristic

Integer linear programming

Iterative greedy

16

Matching algorithms based on Running repository:

Matching Algorithms

First in First out 1 (FIFO1)

First in First out n (FIFOn)

Best Pair (BP)

A general W2W matching framework can be found in Taouil’s ITC paper, 2010

17

Matching criteria:

Matching Criteria

Maximize matching good dies

Maximizing matching bad dies

Minimize matching between good and bad dies (UF)

,( ) max( , ( ))i j i jMax MG G F F

,( ) max( , ( ))i j i jMax UF G F F

,( ) max( , ( ))i j i jMax MF G F F

( ),

i iG F Number of good dies in wafer with fault map Fi j Index of wafers in repository

18

Illustration of two different kinds of wafer maps:

More Practical Wafer Maps

Uniform Clustered

19

Wafers fabricated with rotational symmetry:

Specifically Designed Wafers

B. Zhang, B. Li, V. D. Agrawal, “Wafer cut and rotation to improve the compound yield for 3D Wafer-on-Wafer stacking,“ Proc. International Test Conf., 2013, submitted.

E. Singh, “Exploiting Rtational Symmetries for Improved Stacked Yields in W2W 3D-SICs,” in Proc. IEEE 29th VLSI Test Symposium (VTS), 2011, pp. 32–37.

Double rotation Fourfold rotation

Presentation Outline Introduction Problem Statement Previous efforts Our efforts

Proposed a hybrid wafer stacking procedure Proposed a new wafer manipulation method Exploited more defect models Die per sector calculator

Experimental results Future work

Pollution elimination Find the optimal number of cuts

Conclusion

Apr. 10, 2013 Bei’s General exam 20

21

A hybrid stacking procedure and a new wafer manipulation method:

Illustration of Our Efforts

B. Zhang, B. Li, V. D. Agrawal, “Wafer cut and rotation to improve the compound yield for 3D Wafer-on-Wafer stacking,“ Proc. International Test Conf., 2013, submitted.

Defect Distribution Models

Wafer Manipulations

Repository Replenishment Schemes

Matching Algorithms

Uni

form

Clu

ster

ed

None

Rotation None

Stati

c

Running

StaticStatic

[14] [22] [16] [17][24]

Gree

dy, I

MH,

ILP Iterative Greedy

FIFO, B

est-pair

Iterative Greedy

Iterative Greedy

Publication year (2009 - )

Wafer-on-w

afer stacking procedure

Rot

atio

n

Cut&Rotation

Running

Running

Best-pair

Best-pair

Cut&RotationHybrid

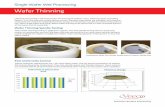

Common wafer cut into sectors

Wafer Cut and Rotation

Cut

Apr. 10, 2013 Bei’s General exam 22

Cut rotationally symmetric wafer to sectors:

Wafer Cut and Rotation

Cut

Apr. 10, 2013 Bei’s General exam 23

Sub-wafers rotation:

Wafer Cut and Rotation

Rotate

Apr. 10, 2013 Bei’s General exam 24

Discussion on the number of cuts:

Wafer Cut and Rotation

Places where no die can be placed

Illustration of Die loss on a wafer

Apr. 10, 2013 Bei’s General exam 25

Process FlowBack-up wafer with rotational

symmetry

Back-up wafer with rotational

symmetry

Back-up wafer with rotational

symmetry

Pre-bond test Pre-bond test Pre-bond test

Cut & rotate Cut & rotate Cut & rotate

Runningrepository consists

of subwafers

Best-pair match

Best-one match

Stack of two subwafers

Final stack for post-bond processing

Runningrepository consists

of subwafers

Runningrepository consists

of subwafers

Apr. 10, 2013 Bei’s General exam 26

SummaryDifferent wafer manipulation methods:

Names ExplanationsBasic Two wafers are matched directly

Rotation4 Two wafers can be matched in 4different ways due to rotational symmetry

Rotation2 Two wafers can be matched in 2different ways due to rotational symmetry

Cut and Rotation4 (CR4)

Each wafer is cut to 4 sectorsand with each sector rotated for matching

Cut and Rotation2 (CR2)

Each wafer is cut to 2 sectorsand with each sector rotated for matching

Apr. 10, 2013 Bei’s General exam 27

Presentation Outline Introduction Problem Statement Previous efforts Our efforts

Proposed a hybrid wafer stacking procedure Proposed a new wafer manipulation method Exploited more defect models Die per sector calculator

Experimental results Future work

Pollution elimination Find the optimal number of cuts

Conclusion

Apr. 10, 2013 Bei’s General exam 28

29

Experiments

We consider 200-mm wafers with edge clearance set as 5 mm.

Three types of chips with different die sizes:• Type1: 31.8 mm2, dies per wafer is 804, overall yield is 80.04%,• Type2: 63.4 mm2, dies per wafer is 436, overall yield is 61.27%• Type3: 131.6 mm2, dies per wafer is 184, overall yield is 50.97%

Experiment setup:

95 mm

100

mm

31.8 mm2

63.4 mm2131.6 mm2

Experiments

A production size of 100,000 3D ICs is targeted in all experiments for each type of chips.

The running repository based best-pair matching algorithm is utilized in the experiment.

Employ Heap structure to speed up the matching process

Experiment setup:

Apr. 10, 2013 Bei’s General exam 30

31

Normalized yield versus radius for three types of chips

Defect Model Used1) Uniform defect model2) Radial clustered degradation model:

0 20 40 60 80 1000

0.2

0.4

0.6

0.8

1

Radius (mm)

Nor

mal

ized

yie

ld

Type 1Type 2Type 3

11 exp( ( ))

Yieldr

Inner core yieldType1: 88%Type2: 80%Type3: 70%

D. Teets, “A Model for Radial Yield Degradation as a Function of Chip Size,” IEEE Transactions on Semiconductor Manufacturing, vol. 9, no. 3, pp. 467–471, 1996.

32

Comparison of Stacking Procedures on Uniform and Clustered Defect Models

Number of stacked layers: 2

Yield comparison between Basic, Rotation2, CR2 for type 3 chip

0 10 20 30 40 500.2

0.25

0.3

0.35

Repository size

Yie

ld

Cluster-CR2Cluster-Rotation2Uniform-CR2Uniform-Rotation2Uniform-Basic

33

Impact of Cut Number and Rotation Number on Compound Yield

Number of stacked layers: 3

Normalized yield versus repository size for type 3 chips

0 10 20 30 40 501

1.1

1.2

1.3

1.4

1.5

1.6

Repository size

Rel

ativ

e yi

eld

incr

ease

fact

or

CR4Rotation4 CR2Rotation2Basic

34

Impact of Total Number of Stacked Layers on Compound Yield

Repository size is set as 50

Normalized yield versus number of stacked layers for type 3 chip

2 3 4 5 6 71

1.2

1.4

1.6

1.8

2

Number of stacked layers

Rel

ativ

e yi

eld

incr

ease

fact

or

CR4CR2Rotation4 Rotation2

35

Impact of Wafer Yield on Compound Yield Repository size is set as 50

Normalized yield versus inner core wafer yield for type 3 chip

30% 40% 50% 60% 70% 80% 90%1

1.1

1.2

1.3

1.4

1.5

Inner core wafer yield

Rel

ativ

e yi

eld

incr

ease

fact

or

CR4CR2Rotation4Rotation2

36

Impact of Production Size on Compound Yield

Repository size : 25

Normalized yield versus production size for type 3 chip

0 200 400 600 800 10000.15

0.2

0.25

0.3

0.35

0.4

0.45

Production size

Yie

ld

CR4Rotation4CR2Basic

37

Exploit More Defect Models

The spatial probability functions usedto generate the simulated Wafers.

Gray levels correspond to failure probabilities ranging from 0 (white) to 1 (black)

Pattern 1 Pattern 2 Pattern 3

Pattern 4 Pattern 5 Pattern 6

Pattern 7 Pattern 8 Pattern 9

G. DeNicoao, E. Pasquinetti, G. Miraglia, and F. Piccinini, “Unsupervised spatial pattern classification of electrical fail-ures in semiconductor manufacturing,” in Artif. Neural Net-works Pattern Recognit. Workshop, 2003, pp. 125–131.

38

Yield Comparison Between Different Stacking Procedures

0 10 20 30 40 501

1.05

1.1

1.15

1.2

1.25

1.3

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.5

2

2.5

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.1

1.2

1.3

1.4

1.5

1.6

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.05

1.1

1.15

1.2

1.25

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.05

1.1

1.15

1.2

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.1

1.2

1.3

1.4

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.1

1.2

1.3

1.4

1.5

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.1

1.2

1.3

1.4

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 10 20 30 40 501

1.1

1.2

1.3

1.4

1.5

Repository size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

(b) Pattern 2 (c) Pattern 3(a) Pattern 1

(e) Pattern 5 (f) Pattern 6(d) Pattern 4

(h) Pattern 8 (i) Pattern 9(g) Pattern 7

Impact of Number of Stacked Layers on Compound Yield

2 3 4 5 6 71

1.1

1.2

1.3

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.5

2

2.5

3

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.1

1.2

1.3

1.4

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.05

1.1

1.15

1.2

1.25

1.3

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.05

1.1

1.15

1.2

1.25

1.3

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.1

1.2

1.3

1.4

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.1

1.2

1.3

1.4

1.5

1.6

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.1

1.2

1.3

1.4

1.5

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

2 3 4 5 6 71

1.1

1.2

1.3

1.4

Number of stacked layers

Nor

mal

ized

yie

ld

CR4CR2Rotation4Rotation2

(b) Pattern 2 (c) Pattern 3(a) Pattern 1

(e) Pattern 5 (f) Pattern 6(d) Pattern 4

(h) Pattern 8 (i) Pattern 9(g) Pattern 7 39

Impact of Production Size on Compound Yield

(b) Pattern 2 (c) Pattern 3(a) Pattern 1

(e) Pattern 5 (f) Pattern 6(d) Pattern 4

(h) Pattern 8 (i) Pattern 9(g) Pattern 7

0 200 400 600 800 10000.75

0.8

0.85

0.9

0.95

1

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 1000

0.6

0.7

0.8

0.9

1

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 10000.2

0.4

0.6

0.8

1

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 10000.65

0.7

0.75

0.8

0.85

0.9

0.95

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 10000.8

0.85

0.9

0.95

1

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 10000.5

0.6

0.7

0.8

0.9

1

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 10000.4

0.5

0.6

0.7

0.8

0.9

1

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 10000.5

0.6

0.7

0.8

0.9

1

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

0 200 400 600 800 10000.65

0.7

0.75

0.8

0.85

0.9

0.95

Production size

Nor

mal

ized

yie

ld

CR4Rotation4CR2Rotation2Basic

40

Presentation Outline Introduction Problem Statement Previous efforts Our efforts

Proposed a hybrid wafer stacking procedure Proposed a new wafer manipulation method Exploited more defect models Die per sector calculator

Experimental results Future work

Pollution elimination Find the optimal number of cuts

Conclusion

Apr. 10, 2013 Bei’s General exam 41

Repository Pollution(downside of running repository)

Phenomenon:• As the production size increases (large production volume), the

compound yield of 3D stacked IC decreases continuously.

Reasons:• Unattractive wafers remain in the repository for many iterations,

occupying space, and in effect reducing the size of the repository in the long run.

General solution:• Need a mechanism to force the unattractive wafers to leave the

repository in a timely manner.

M. Taouil, S. Hamdioui, J. Verbree, and E. J. Marinissen, “On Maximizing the compound yield for 3D wafer-to-wafer stacked IC," in Proc. International Test Conf., 2010, pp. 1-10.

Apr. 10, 2013 Bei’s General exam 42

Repository Pollution(downside of running repository)

Possible detailed solutions: Conduct running repository based matching and static repository based matching, alternatively.

Expunge poor wafers/quadrants from the repository if they have not been used after n tries, send them to a die stacking process to make some use of them

Exploiting a mechanism to force the unattractive wafer leave the repository at the same rate as they come in.

Utilize partial repository instead of running repository to reduce pollution and also enhance the compound yield.

Apr. 10, 2013 Bei’s General exam 43

Find Optimal Number of Cuts(Current research is exploring this aspect)

In case of more than 4 cuts, two methods of placement:

Placement method 1 Placement method 2

Apr. 10, 2013 Bei’s General exam 44

# of Dies Per Sector (DPS) Calculator

Placement method 1:

2tan( )L

L

H

cos( )2r

2tan( )Lr NH

cos2 2 tan 2(1) { }

Lr

N floorH

'2tan( )2(2) { }

Lr NH

N floorH

'

2 2

1

1

2 ( )2 tan 2

(3) {1 2( 1) tan( )}2

{ }

N

i

N

i

Lr NH iH

L

HDPS floor iL

floor

Apr. 10, 2013 Bei’s General exam 45

# of Dies Per Sector (DPS) Calculator

Placement method 2:

iH

sin( )r

L

Hsin( )(1) { }rN floor

H

2 2

1

( )tan(2) { }

N

i

r iH

L

iH

DPS floor

Apr. 10, 2013 Bei’s General exam 46

Relationship Between DPW and # of Cuts--- Case Study

# of Type 1 dies per wafer:

5 10 15 20600

650

700

750

800

850

Number of cuts

Tota

l num

ber o

f die

s pe

r waf

er

Method 1Method2

31.8 mm2

95 mm

100

mm

DPW V.S. number of cuts for placement method 1 and 2 47

Relationship Between DPW and # of Cuts--- Case Study

# of Type 2 dies per wafer:

95 mm

100

mm

5 10 15 20260

280

300

320

340

360

380

400

Number of cuts

Tota

l num

ber o

f die

s pe

r waf

er

Method 1Method2

63.4 mm2

48DPW V.S. number of cuts for placement method 1 and 2

Relationship Between DPW and # of Cuts--- Case Study

# of Type 3 dies per wafer:

95 mm

100

mm

5 10 15 20100

120

140

160

180

200

Number of cuts

Tota

l num

ber o

f die

s pe

r waf

er

Method 1Method2

131.6 mm2

49DPW V.S. number of cuts for placement method 1 and 2

Typical Die Size

http://www.geek.com/glossary/die-size/

Apr. 10, 2013 Bei’s General exam 50

Comparison Between Two Placement Methods – Case Studies

12-inch wafer (# of cuts range from 4 to 8):

0 5 10 15 20 250

5

10

15

20

25

Die height

Die

wid

th

The dots show the cases where method 1 outperforms method 2Apr. 10, 2013 Bei’s General exam 51

Comparison Between Two Placement Methods – Case Studies

18-inch wafer (# of cuts range from 4 to 8): :

0 5 10 15 20 250

5

10

15

20

25

Die height

Die

wid

th

The dots show the cases where method 1 outperforms method 2Apr. 10, 2013 Bei’s General exam 52

Presentation Outline Introduction Problem Statement Previous efforts Our efforts

Proposed a hybrid wafer stacking procedure Proposed a new wafer manipulation method Exploited more defect models Die per sector calculator

Experimental results Future work

Pollution elimination Find the optimal number of cuts

Conclusion

Apr. 10, 2013 Bei’s General exam 53

Conclusion

Apr. 10, 2013 Bei’s General exam 54

Deal with the problem of low compound yield in W2W stacking Proposes a hybrid W2W stacking scheme Proposes wafer Cut and Rotation manipulation method for yield

improvement Extensive experimental results validate the cut and rotation

method Develop the die per sector calculator Need to solve repository pollution Need to find the optimal number of cuts

55

References[1] R. Beica, C. Sharbono, and T. Ritzdorf, “Through Silicon Via Copper Electrodeposition

for 3D Integration,” in Proc. 58th Electronic Components and Technology Conference (ECTC), 2008, pp. 577–583.

[2] M. L. Bushnell and V. D. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits. Springer, 2000.

[3] W. R. Davis, J. Wilson, S. Mick, J. Xu, H. Hua, C. Mineo, A. M. Sule, M. Steer, and P. D. Franzon, “Demystifying 3D ICs: The Pros and Cons of Going Vertical,” IEEE Design & Test of Computers, vol. 22, no. 6, pp. 498–510, 2005.

[4] G. DeNicoao, E. Pasquinetti, G. Miraglia, and F. Piccinini, “Unsupervised spatial pattern classification of electrical fail-ures in semiconductor manufacturing,” in Artif. Neural Net-works Pattern Recognit. Workshop, 2003, pp. 125–131.

[5] X. Dong and Y. Xie, “System-Level Cost Analysis and Design Exploration for Three-Dimensional Integrated Circuits (3D ICs),” in Proc. Asia and South Pacific Design Automation Conference (ASP-DAC), 2009, pp. 234–241.

[6] J. Dukovic et al., “Through-Silicon-Via Technology for 3D Integration,” in Proc. IEEE International Memory Workshop (IMW), 2010, pp. 1–2.

[7] A. Gupta, W. A. Porter, and J. W. Lathrop, “Defect Analysis and Yield Degradation of Integrated Circuits,” IEEE Journal of Solid-State Circuits, vol. 9, no. 3, pp. 96–102, Mar. 1974.

56

References (contd..)[8] H.-H. S. Lee and K. Chak, “Test Challenges for 3D Integrated Circuits,” IEEE Design

& Test of Computers, vol. 26, no. 5, pp. 26–35, 2009.[9] H. Liao, M. Miao, X. Wan, Y. Jin, L. Zhao, B. Li, Y. Zhu, and X. Sun, “Microfabrication

of Through Silicon Vias (TSV) for 3D SiP,” in Proc. 9th International Conference on Solid-State and Integrated-Circuit Technology (ICSICT), 2008, pp. 1199–1202.

[10] E. J. Marinissen, “Challenges and Emerging Solutions in Testing TSV-Based 2 1/2D- and 3D-Stacked ICs,” in Proc. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2012, pp. 1277–1282.

[11] J. V. Olmen et al., “3D Stacked IC Demonstration Using a Through Silicon Via First Approach,” in Proc. IEEE International Electron Devices Meeting (IEDM), 2008, pp. 1–4.

[12] F. D. Palma, G. D. Nicolao, G. Miraglia, E. Pasquinetti, and F. Piccinini, “Unsupervised spatial pattern classification of electrical-wafer-sorting maps in semiconductor manufacturing,” Pattern Recogn. Lett., vol. 26, no. 12, pp. 1857–1865, Sept. 2005.

[13] M. Puech, J. M. Thevenoud, J. M. Gruffat, N. Launay, N. Arnal, and P. Godinat, “Fabrication of 3D Packaging TSV Using DRIE,” in Proc. Symposium on Design, Test, Integration and Packaging of MEMS/MOEMS, 2008, pp. 109–114.

57

References (contd..)[14] S. Reda, G. Smith, and L. Smith, “Maximizing the Functional Yield of Wafer-to-Wafer

3-D Integration,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 17, no. 9, pp. 1357–1362, Sept. 2009.

[15] A. Rogers, Statistical Analysis of Spatial Dispersions. United Kingdom: Pion Limited, 1974.

[16] E. Singh, “Exploiting Rtational Symmetries for Improved Stacked Yields in W2W 3D-SICs,” in Proc. IEEE 29th VLSI Test Symposium (VTS), 2011, pp. 32–37.

[17] E. Singh, “Impact of Radial Defect Clustering on 3D Stacked IC Yield from Wafer to Wafer Stacking,” in Proc. International Test Conference (ITC), 2012, pp. 1–7.

[18] L. Smith, G. Smith, S. Hosali, and S. Arkalgud, “Yield Considerations in the Choice of 3D Technology,” in Proc. International Symposium on Semiconductor Manufacturing (ISSM), 2007, pp. 1–3.

[19] C. H. Stapper, “On Yield, Fault Distributions, and Clustering of Particles,” IBM Journal of Research and Development, vol. 30, no. 3, pp. 326–338, 1986.

[20] C. H. Stapper, “Simulation of Spatial Fault Distributions for Integrated Circuit Yield Estimations,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 8, no. 12, pp. 1314–1318, Dec. 1989.

[21] M. Taouil and Hamdioui, “Yield Improvement for 3D Wafer-to-Wafer Stacked Memories,” Journal of Electronic Testing: Theory and Applications, vol. 28, no. 4, pp. 523–534, Aug. 2012.

References (contd..)[22] M. Taouil, S. Hamdioui, J. Verbree, and E. J. Marinissen, “On Maximizing the

Compound Yield for 3D Wafer-to-Wafer Stacked ICs,” in Proc. IEEE International Test Conference (ITC), 2010, pp. 1–10.

[23] D. Teets, “A Model for Radial Yield Degradation as a Function of Chip Size,” IEEE Transactions on Semiconductor Manufacturing, vol. 9, no. 3, pp. 467–471, 1996.

[24] J. Verbree, E. J. Marinissen, P. Roussel, and D. Velenis, “On the Cost-Effectiveness of Matching Repositories of Pre-Tested Wafers for Wafer-to-Wafer 3D Chip Stacking,” in Proc. 15th IEEE European Test Symposium (ETS), 2010, pp. 36–41.

[25] T. Yanagawa, “Influence of Epitaxial Mounds on the Yield of Integrated Circuits,” Proceedings of the IEEE, vol. 57, no. 9, pp. 1621–1628, Sept. 1969.

[26] T. Yanagawa, “Yield Degradation of Integrated Circuits Due to Spot Defects,” IEEE Transactions on Electron Devices, vol. 19, no. 2, pp. 190–197, 1972.

[27] B. Zhang, B. Li, V. D. Agrawal, “Wafer cut and rotation to improve the compound yield for 3D Wafer-on-Wafer stacking,“ Proc. International Test Conf., 2013, submitted.

[28] B. Zhang and V. D. Agrawal, “Wafer cut and rotation for compound yield improvement in 3D Wafer-on-Wafer stacking,” Proc. 22nd North Atlantic Test Workshop, 2013.

58

References for Some Figures Used[1]http://www.google.com/imgres?imgurl=http://i.i.com.com/cnwk.1d/i/tim/2011/05/04/intel-

trigate-22nm-transistor-small.jpg&imgrefurl=http://news.cnet.com/8301-13924_3-20059431-64.html&h=385&w=439&sz=60&tbnid=EE_RELtUe5YAnM:&tbnh=90&tbnw=103&prev=/search%3Fq%3D3D%2Btransistor%26tbm%3Disch%26tbo%3Du&zoom=1&q=3D+transistor&usg=__eiw39Fz1iYzP3WpUZgZZg7ILees=&docid=r1U7sbgV4MnNOM&hl=zh-CN&sa=X&ei=OT9jUbrUOITS9QTLk4CYBw&ved=0CDEQ9QEwAA&dur=294

[2] http://www.google.com/imgres?imgurl=http://www.process-evolution.com/images_3d-ics/rpi_bcb_3d-ic.png&imgrefurl=http://www.process-evolution.com/3d-ics_doe.html&h=675&w=970&sz=262&tbnid=Kk9qMm4OzVTiJM:&tbnh=85&tbnw=122&prev=/search%3Fq%3D3D%2BIC%26tbm%3Disch%26tbo%3Du&zoom=1&q=3D+IC&usg=__tCjabwl9UEVgdFUY57YsY4T6euM=&docid=4ieBYHE2oUKyMM&hl=zh-CN&sa=X&ei=ZD9jUeCxBoGY8gSSpIGABw&ved=0CDoQ9QEwAg&dur=44

59

Thank You!

60

Questions?