VT-SOM-6UL Datasheet...VT-SOM-6UL Datasheet Doc. Num: xxxyyyzzz Confidential Copyright © 2016...

Transcript of VT-SOM-6UL Datasheet...VT-SOM-6UL Datasheet Doc. Num: xxxyyyzzz Confidential Copyright © 2016...

VT-SOM-6UL - i.MX6 UltraLite based System-On-Module (SOM)

VT-SOM-6UL Datasheet

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 2

Copyright Info

The information contained in this document is the proprietary information of Volansys Technologies Pvt.,

Ltd. The contents are confidential and any disclosure to persons other than the officers, employees,

agents or subcontractors of the owner or license of this document, without the prior written consent of

Volansys, is strictly prohibited.

Further, no portion of this document may be reproduced, stored in a retrieval system, or transmitted in

any form or by any means, electronic or mechanical, including photocopying and recording, without the

prior written consent of Volansys, the copyright holder.

Volansys publishes this document without making any warranty as to the content contained herein.

Further Volansys reserves the right to make modifications, additions and deletions to this document due

to typographical errors, inaccurate information, or improvements to products mentioned in the document

at any time and without notice. Such changes will, nevertheless be incorporated into new editions of this

document.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 3

Table of Contents

1 REVISION HISTORY ....................................................................................................................................... 6

2 INTRODUCTION ............................................................................................................................................ 7

3 MAJOR ON BOARD COMPONENTS ............................................................................................................. 11

4 EMBEDDED INTERFACES ............................................................................................................................. 13

5 SYSTEM LOGIC ............................................................................................................................................ 46

6 OPERATIONAL CHARACTERISTICS ............................................................................................................... 49

7 MECHANICAL DIMENSIONS & SODIMM EDGE CONNECTOR ........................................................................ 50

8 ORDERING INFORMATION ......................................................................................................................... 52

9 SOM PIN INFORMATION ............................................................................................................................ 53

10 PIN MULTIPLEXING ..................................................................................................................................... 60

11 APPENDIX - A ............................................................................................................................................. 61

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 4

List of Figures

Figure 1 - VT-SOM-6UL Block Diagram ........................................................................................................ 8

Figure 2 - SW1 for Boot Mode Selection.................................................................................................... 48

Figure 3 - SOM board dimensions (TOP side)1,2 ......................................................................................... 50

Figure 4 - PCB edge finger connector dimension3 ..................................................................................... 50

Figure 5 - PCB edge finger connector (Top side) ........................................................................................ 51

Figure 6 – SOM Insertion ........................................................................................................................... 61

Figure 7 - Clip lock ...................................................................................................................................... 62

Figure 8 – Eject SOM .................................................................................................................................. 62

Figure 9 - Reference platform with supported modules ............................................................................ 63

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 5

List of Tables

Table 1 - Revision History ............................................................................................................................ 6

Table 2 – References ................................................................................................................................... 6

Table 3 - Ethernet interface signals ........................................................................................................... 14

Table 4 - Ethernet MAC interface signals ................................................................................................... 15

Table 5 - USB OTG interface signals ........................................................................................................... 17

Table 6 - LCD interface signals ................................................................................................................... 18

Table 7 - Camera interface signals ............................................................................................................. 20

Table 8 - I2C interface signals .................................................................................................................... 21

Table 9 - ECSPI interface signals ................................................................................................................ 23

Table 10 - QSPI interface signals ................................................................................................................ 24

Table 11 - UART interface signals .............................................................................................................. 26

Table 12 - SAI interface signals .................................................................................................................. 29

Table 13 - MQA interface signals ............................................................................................................... 29

Table 14 - PWM interface signals .............................................................................................................. 32

Table 15 - GPIO Signals .............................................................................................................................. 35

Table 16 - JTAG Interface signals ............................................................................................................... 37

Table 17 - SPDIF Interface Signals .............................................................................................................. 37

Table 18 - Analog Input Signals .................................................................................................................. 38

Table 19 - uSDHC Interface Signals ............................................................................................................ 42

Table 20 - CAN Interface Signals ................................................................................................................ 43

Table 21 - Keypad Interface signals ........................................................................................................... 44

Table 22 - SIM Interface signals ................................................................................................................. 45

Table 23 - Supported power supply ........................................................................................................... 46

Table 24 - Control & Power signals ............................................................................................................ 47

Table 25 - Reset signals .............................................................................................................................. 47

Table 26 - DIP switch Configuration ........................................................................................................... 47

Table 27 - Absolute Maximum Rating ........................................................................................................ 49

Table 28 - Recommended operating condition ......................................................................................... 49

Table 29 - DC Electrical Characteristic ....................................................................................................... 49

Table 30 - Product part number generator ................................................................................................ 52

Table 31 - SOM Pin Information ................................................................................................................ 59

Table 32 - Acronyms & abbreviations ........................................................................................................ 61

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 6

1 REVISION HISTORY

1.1 Revision History

Rev. Date Description Prepared By Reviewed By Approved By

0.1 09-Sep-16 Initial draft version released

Ritesh Patel Hitesh Gambhava

0.2 15-Sep-16 Updated Block diagram and Temperature range

Ritesh Patel Hitesh Gambhava

Table 1 - Revision History

Please check for an updated revision at http://www.volansys.com

1.2 References

Documents Revision

Datasheet i.MX6UL (IMX6ULCEC) 1.0

i.MX 6UltraLite Applications Processor Reference Manual 1.0

Table 2 – References

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 7

2 INTRODUCTION

2.1 About this document

This document is a datasheet providing necessary information to operate VT-SOM-6UL SOM from

Hardware perspective.

2.2 Overview

VT-SOM-6UL is an ARM Cortex-A7 platform based System-On-Module (SOM) in SODIMM form

factor. It incorporates ultra-efficient 528MHz iMX6 ultraLite processor from NXP.

VT-SOM-6UL provides a variety of different interface options. With superior price and performance

it is ideal for fast emerging applications such as Internet-of-Things (IoT), different embedded and

industrial products, portable devices and battery operated embedded systems.

It speed up the product development time by reducing time & cost required for development,

providing easy integration with application specific custom board and help to be quickly in the

market.

VT-Custom board (VT-SOM-6UL with base board) complements an attractive reference kit, which

can be used for customers’ evaluation, product development and or product mass production.

Contact Volansys support services for further information: [email protected]

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 8

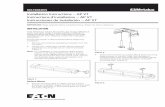

2.3 Block Diagram

Figure 1 - VT-SOM-6UL Block Diagram

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 9

2.4 VT-SOM-6UL Features

CPU Core – NXP i.MX 6UltraLite

- Power efficient 528MHz ARM Cortex-A7™

- Integrated security features

- 2D pixel acceleration engine (PxP)

- NEON SIMD and VFPv4

Memory and Storage

- 256MB DDR3L DRAM (Upgradable up to 1GB)

- 1GB NAND Flash memory (Upgradable up to 4GB)

- Optional 4GB eMMC memory (Upgradable up to 16GB)

- EEPROM for Device info and configuration storage

Display and Camera support

- Up to 24-bit Parallel LCD up to WXGA (1366 x 768)

- Up to 24-bit parallel camera interface

Communication & Networking

- 2x High Speed USB 2.0 OTG connectivity

- 1x 10/100Mbps Ethernet (w/o magnetics)

- 1x 10/100Mbps RMII MAC

Other I/O Interfaces - Up to 2x CAN

- Up to 2x SDIO

- Up to 3x SAI

- S/PDIF

- MQS

- Up to 4x I2C

- Up to 4x SPI

- QSPI

- Up to 8x UART

- Up to 2x Smart card interface

- Up to 8x PWM

- JTAG

- Keypad

- ADC

- GPIO

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 10

Power input - DC 3.3 to 5V

Operating Temperature - Commercial: 0 to + 70 °C

- Industrial: -40 to +85 °C

Form Factor - SO-DIMM 200 edge finger

Dimensions (L x W x H) - 67.6mm x 45.0mm x 4.5mm

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 11

3 MAJOR ON BOARD COMPONENTS This section describes the major hardware components of the VT-SOM-6UL.

3.1 i.MX6Ultralite processor

The i.MX 6UltraLite is a high performance, ultra-efficient processor family featuring NXP’s

advanced implementation of the single ARM Cortex®-A7 core, which operates at speeds up to 528 MHz.

i.MX 6UltraLite processor include:-

ARM Cortex-A7 MPCore (with TrustZone) with:

— 32 KBytes L1 Instruction Cache

— 32 KBytes L1 Data Cache

— Private Timer

— Cortex-A7 NEON Media Processing Engine (MPE) Co-processor

General Interrupt Controller (GIC) with 128 interrupts support

Global Timer

Snoop Control Unit (SCU)

128 KB unified I/D L2 cache (on G2 and G3 devices only)

Pixel processing pipeline (PxP)

Power management

3.2 Memory

3.2.1 DRAM memory

VT-SOM-6UL is equipped with up to 1GB of onboard DDR3L memory with density options of

256MB, 512 MB or 1GB.

3.2.2 Storage memory

VT-SOM-6UL is available with onboard SLC/MLC NAND or eMMC storage memory with density

options depending on board configuration. Please see ordering info for more details.

3.2.3 EEPROM memory

VT-SOM-6UL is equipped with 4kB EEPROM memory to save configuration data and board

information.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 12

3.3 PMIC

The PF3001 is a SMARTMOS Power Management Integrated Circuit (PMIC) designed specifically

for i.MX6UL application processor. With up to three buck converters, six linear regulators, RTC supply, and

coin-cell charger, the PF3001 can provide power for a complete system, including applications processors,

memory, and system peripherals.

3.4 Ethernet PHY

VT-SOM-6UL is available with on board 100Mbps Ethernet PHY KSZ8081. KSZ8081 is 10Base-

T/100Base-TX Ethernet physical layer transceiver for transmission and reception of data over standard

CAT-5 unshielded twisted pair (UTP) cable.

A 1:1 isolation transformer is required at the line interface. An isolation transformer with

integrated common-mode chokes is recommended. Recommended magnetics is J00-0045NL from Pulse

Electronics Corporation or equivalent.

Ethernet PHY is configured in RMII mode with Auto negotiation enabled. PHY address is set to

0x2h.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 13

4 EMBEDDED INTERFACES

This section describes all embedded hardware interfaces of the VT-SOM-6UL.

VT-SOM-6UL implements different peripheral interfaces through the SODIMM-200 connector.

Notes:-

1. All digital interfaces of VT-SOM-6UL operate at 3.3V voltage level, unless otherwise specified.

2. Depending on configuration options in ordering information some of the interfaces or signals may

or may not be available.

3. Some of the VT-SOM-6UL board interface pins are multifunctional. Multifunctional pins are

denoted with an (*) asterisk. For more detail, please refer chapter - 10

Signal Types:-

“AI” – Analog Input

“AO” – Analog Output

"AIO" – Analog Input/output

“I” – Digital Input

"O" – Digital Output

“IO” – Digital Input/output

“P” – Power

"PD" - Always pulled down on-board

"PU" - Always pulled up on-board

"OD" – Open Drain

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 14

4.1 Ethernet Interface

The VT-SOM-6UL incorporates a single full-featured 10/100 Ethernet PHY interfaced with RMII

Ethernet MAC.

Features supported on Ethernet interface:-

- 10Base-T/100Base-TX IEEE802.3 compliant Ethernet transceiver

- IEEE 802.3 Auto-Negotiation support

- Automatic MDI/MDI-X to reliably detect and correct straight-through and crossover cable

connection

- Supports 10/100 Mbit/s full-duplex and configurable half-duplex operation

- Power down and Power saving modes

- LinkMD TDR-based cable diagnostics to identify faulty copper cabling

- LED outputs for link, activity and speed status indications

Pin # Signal name Description Type SoC Pin #

25 ENET1_TXP Transmit data positive. 100Base-TX or 10Base-T differential transmit output positive to magnetics.

AO -

23 ENET1_TXM Transmit data negative. 100Base-TX or 10Base-T differential transmit output negative to magnetics.

AO -

21 ENET1_RXP Receive data positive. 100Base-TX or 10Base-T differential receive input positive to magnetics.

AI -

19 ENET1_RXM Receive data negative. 100Base-TX or 10Base-T differential receive input negative to magnetics.

AI -

20 ENET1_LED0 Link/Activity indicator LED output O -

22 ENET1_LED1 Speed indicator LED output O -

24 3V3_ENET Power to drive Status LED on carrier board only. NC if not used

P -

Table 3 - Ethernet interface signals

For Magnetic selection, refer section 3.4.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 15

4.2 10/100- Mbps Ethernet MAC (ENET)

The VT-SOM-6UL incorporates a 10/100Mbps Ethernet MAC compliant with the IEEE802.3-2002

standard. The MAC layer provides compatibility with half- or full duplex 10/100-Mbit/s Ethernet LANs.

Features supported on Ethernet MAC interface:-

- Implements the full 802.3 specification with preamble/SFD generation, frame padding

generation, CRC generation and checking

- Dynamically configurable to support 10/100-Mbit/s operation

- Supports 10/100 Mbit/s full-duplex and configurable half-duplex operation

- Supports VLAN-tagged frames according to IEEE 802.1Q

- Programmable MAC address: Insertion on transmit; discards frames with mismatching

destination address on receive (except broadcast and pause frames)

External Ethernet PHY can be interfaced using one of the following MII interface.

1. 4-bit Media Independent Interface (MII) operating at 2.5/25 MHz

2. 4-bit non-standard MII-Lite (MII without the CRS and COL signals) operating at 2.5/25 MHz

3. 2-bit Reduced MII (RMII) operating at 50 MHz

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 22 10/100-Mbps Ethernet MAC (ENET).

Pin # Signal name Description Type SoC Pin #

138* ENET2_TXCLK Transmit clock IO D17

169* ENET2_TXD0 Transmit data 0 O A15

140* ENET2_TXD1 Transmit data 1 O A16

87* ENET2_TXD2 Transmit data 2 O G17

93* ENET2_TXD3 Transmit data 3 O G16

161* ENET2_TXER Transmit error O G14

136* ENET2_TXEN Transmit enable O B15

163* ENET2_RXCLK Receive clock I H15

155* ENET2_RXD0 Receive data 0 I C17

157* ENET2_RXD1 Receive data 1 I C16

130* ENET2_RXD2 Receive data 2 I H17

132* ENET2_RXD3 Receive data 3 I H16

167* ENET2_CRS_DV Carrier sense/ Receive Data valid I B17

142* ENET2_RXER Receive error I D16

89* ENET2_CRS Carrier sense I F17

91* ENET2_COL Collision detect I G13

199* ENET2_MDIO Management Data input/output Interface Data

IO K17

200* ENET2_MDC Management Data input/output Interface Clock

O L16

Table 4 - Ethernet MAC interface signals

Note: - Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 16

4.3 USB interface

The USB controller block provides high performance USB functionality that conforms to the

Universal Serial Bus Specification, Rev. 2.0 and the On-The-Go and Embedded Host Supplement to the

USB Revision2.0 Specification.

The USB controller consists of two independent USB controller cores: 2 On-The-Go (OTG)

controller cores. Each controller core supports UTMI interface. Both the controller cores are single-port

cores.

Features supported on OTG controller cores:-

- High-Speed/Full-Speed/Low-Speed OTG core

- HS/FS/LS UTMI compliant interface

- High Speed, Full Speed and Low Speed operation in Host mode (with UTMI transceiver)

- High Speed, and Full Speed operation in Peripheral mode (with UTMI transceiver)

- Hardware support for OTG signaling, session request protocol, and host negotiation protocol

- Up to 8 bidirectional endpoints

The VT-SOM-6UL contains 2 integrated USB 2.0 PHY macrocells capable of connecting to USB

host/device systems at the USB low-speed (LS) rate of 1.5 Mbps, full-speed (FS) rate of 12 Mbps or at the

USB 2.0 high-speed (HS) rate of 480 Mbps. The integrated PHY provides a standard UTM interface. The

USB _DN and USB_DP pins connect directly to a USB connector.

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 54 Universal Serial Bus Controller (USB).

Pin # Signal name Description Type SoC Pin #

65* USB_OTG1_ID USB OTG1 ID signal I K13

130* USB_OTG1_ID USB OTG1 ID signal I H17

101* USB_OTG1_ID USB OTG1 ID signal I B3

77* USB_OTG1_OC USB OTG1 VBUS Over Current detection I L15

157* USB_OTG1_OC USB OTG1 VBUS Over Current detection I C16

97* USB_OTG1_OC USB OTG1 VBUS Over Current detection I C1

75* USB_OTG1_PWREN USB OTG1 VBUS Power Enable O M16

155* USB_OTG1_PWREN USB OTG1 VBUS Power Enable O C17

99* USB_OTG1_PWREN USB OTG1 VBUS Power Enable O C2

67 USB_OTG1_DP USB OTG1 Data Positive AIO U15

69 USB_OTG1_DN USB OTG1 Data Negative AIO T15

71 USB_OTG1_VBUS USB OTG1 VBUS detection P T12

55* USB_OTG2_ID USB OTG2 ID signal I M17

138* USB_OTG2_ID USB OTG2 ID signal I D17

107* USB_OTG2_ID USB OTG2 ID signal I A2

136* USB_OTG2_OC USB OTG2 VBUS Over Current detection I B15

105* USB_OTG2_OC USB OTG2 VBUS Over Current detection I B1

140* USB_OTG2_PWREN USB OTG2 VBUS Power Enable O A16

103* USB_OTG2_PWREN USB OTG2 VBUS Power Enable O B2

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 17

57 USB_OTG2_DP USB OTG2 Data Positive AIO U13

59 USB_OTG2_DN USB OTG2 Data Negative AIO T13

61 USB_OTG2_VBUS USB OTG2 VBUS detection P U12

Table 5 - USB OTG interface signals

Note:- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

4.4 Display interface

VT-SOM-6UL Display interface is derived from the i.MX6UL eLCDIF module. The eLCDIF is a general

purpose display controller used to drive a wide range of display devices varying in size and capability.

eLCDIF block supports following features:-

- Bus master interface to source frame buffer data for display refresh. This interface can also be

used to drive data for "Smart" displays.

- 8/16/18/24/32 bit LCD data bus support available depending on I/O mux options

- Programmable timing and parameters for MPU, VSYNC and DOTCLK LCD interfaces to support a

wide variety of displays

- ITU-R BT.656 mode (called Digital Video Interface or DVI mode here) including progressive-to-

interlace feature and RGB to YCbCr 4:2:2 color space conversion to support 525/60 and 625/50

operation.

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 32 Enhanced LCD Interface (eLCDIF).

Pin # Signal name Description Type SoC Pin #

104* LCD_PCLK LCD Interface Pixel Clock O A8

106* LCD_EN LCD Interface Data Enable O B8

92* LCD_HSYNC LCD Interface Horizontal Sync O D9

102* LCD_VSYNC LCD Interface Vertical Sync O C9

100* LCD_RST LCD Reset O E9

94*/** LCD_DATA0 LCD Interface Data 0 IO B9

98*/** LCD_DATA1 LCD Interface Data 1 IO A9

88*/** LCD_DATA2 LCD Interface Data 2 IO E10

90*/** LCD_DATA3 LCD Interface Data 3 IO D10

82*/** LCD_DATA4 LCD Interface Data 4 IO C10

80*/** LCD_DATA5 LCD Interface Data 5 IO B10

84*/** LCD_DATA6 LCD Interface Data 6 IO A10

86*/** LCD_DATA7 LCD Interface Data 7 IO D11

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 18

74*/** LCD_DATA8 LCD Interface Data 8 IO B11

78*/** LCD_DATA9 LCD Interface Data 9 IO A11

54*/** LCD_DATA10 LCD Interface Data 10 IO E12

64*/** LCD_DATA11 LCD Interface Data 11 IO D12

72*/** LCD_DATA12 LCD Interface Data 12 IO C12

70*/** LCD_DATA13 LCD Interface Data 13 IO B12

76*/** LCD_DATA14 LCD Interface Data 14 IO A12

48*/** LCD_DATA15 LCD Interface Data 15 IO D13

60*/** LCD_DATA16 LCD Interface Data 16 IO C13

62*/** LCD_DATA17 LCD Interface Data 17 IO B13

68*/** LCD_DATA18 LCD Interface Data 18 IO A13

50*/** LCD_DATA19 LCD Interface Data 19 IO D14

52*/** LCD_DATA20 LCD Interface Data 20 IO C14

58*/** LCD_DATA21 LCD Interface Data 21 IO B14

66*/** LCD_DATA22 LCD Interface Data 22 IO A14

56*/** LCD_DATA23 LCD Interface Data 23 IO B16

Table 6 - LCD interface signals

Note: -

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

- The LCD_DATA signals are used as a boot straps pins. Loading LCD_DATA pins result in wrong boot

or no SOM bootup. (**). Pull up and Pull down resistors will get altered based on another boot

configurations.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 19

4.5 Camera interface

VT-SOM-6UL camera interface is derived from CMOS sensor interface of iMX6UL.

The CSI enables the chip to connect directly to external CMOS image sensors. CMOS image sensors

are separated into two classes, dumb and smart. Dumb sensors are those that support only traditional

sensor timing (Vertical SYNC and Horizontal SYNC) and output only Bayer and statistics data, while smart

sensors support CCIR656 video decoder formats and perform additional processing of the image (for

example, image compression, image pre-filtering, and various data output formats).

CSI block supports following features:-

- Configurable interface logic to support most commonly available CMOS sensors

- Support for CCIR656 video interface as well as traditional sensor interface

- 8-bit / 16-bit / 24-bit data port for YCbCr, YUV, or RGB data input

- 8-bit / 10-bit / 16-bit data port for Bayer data input

- Full control of 8-bit/pixel, 10-bit/pixel or 16-bit / pixel data format to 64-bitreceive FIFO

packing.

- Supports TV Decoder (VADC) input.

VT-SOM-6UL can support connection with sensors as follow:-

- To connect with one 8-bit sensor, the sensor data interface should connect to CSI_DATA[9:2]

- To connect with one 10-bit sensor, the sensor data interface should connect to CSI_DATA[9:0]

- To connect with one 16-bit sensor, the sensor data interface should connect to CSI_DATA[15:0]

- To connect with one 24-bit data, either video pass-through or TV Decoder input, the sensor data

interface should connect to CSI_DATA[23:0]

- To connect with two 8-bit sensors, the sensor data interfaces should connect to CSI_DATA[7:0]

and CSI_DATA[15:8]

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 19 CMOS Sensor Interface (CSI).

Pin # Signal name Description Type SoC Pin #

132* csi.DATA[0] Data Sensor Signal 0 I H16

62*/** csi.DATA[0] Data Sensor Signal 0 I B13

130* csi.DATA[1] Data Sensor Signal 1 I H17

60*/** csi.DATA[1] Data Sensor Signal 1 I C13

110* csi.DATA[2] Data Sensor Signal 2 I K14

137* csi.DATA[2] Data Sensor Signal 2 I E4

112* csi.DATA[3] Data Sensor Signal 3 I K16

139* csi.DATA[3] Data Sensor Signal 3 I E3

114* csi.DATA[4] Data Sensor Signal 4 I K15

141* csi.DATA[4] Data Sensor Signal 4 I E2

116* csi.DATA[5] Data Sensor Signal 5 I J14

143* csi.DATA[5] Data Sensor Signal 5 I E1

120* csi.DATA[6] Data Sensor Signal 6 I J17

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 20

145* csi.DATA[6] Data Sensor Signal 6 I D4

122* csi.DATA[7] Data Sensor Signal 7 I J16

147* csi.DATA[7] Data Sensor Signal 7 I D3

124* csi.DATA[8] Data Sensor Signal 8 I J15

149* csi.DATA[8] Data Sensor Signal 8 I D2

126* csi.DATA[9] Data Sensor Signal 9 I H14

151* csi.DATA[9] Data Sensor Signal 9 I D1

163* csi.DATA[10] Data Sensor Signal 10 I H15

68*/** csi.DATA[10] Data Sensor Signal 10 I A13

157* csi.DATA[11] Data Sensor Signal 11 I G14

50*/** csi.DATA[11] Data Sensor Signal 11 I D14

140* csi.DATA[12] Data Sensor Signal 12 I G17

52*/** csi.DATA[12] Data Sensor Signal 12 I C14

142* csi.DATA[13] Data Sensor Signal 13 I G16

58*/** csi.DATA[13] Data Sensor Signal 13 I B14

136* csi.DATA[14] Data Sensor Signal 14 I F17

66*/** csi.DATA[14] Data Sensor Signal 14 I A14

138* csi.DATA[15] Data Sensor Signal 15 I G13

56*/** csi.DATA[15] Data Sensor Signal 15 I B16

74*/** csi.DATA[16] Data Sensor Signal 16 I B11

78*/** csi.DATA[17] Data Sensor Signal 17 I A11

54*/** csi.DATA[18] Data Sensor Signal 18 I E12

64*/** csi.DATA[19] Data Sensor Signal 19 I D12

72*/** csi.DATA[20] Data Sensor Signal 20 I C12

70*/** csi.DATA[21] Data Sensor Signal 21 I B12

76*/** csi.DATA[22] Data Sensor Signal 22 I A12

48*/** csi.DATA[23] Data Sensor Signal 23 I D13

199* csi.MCLK CMOS Sensor Master Clock O K17

133* csi.MCLK CMOS Sensor Master Clock O F5

200* csi.PIXCLK Pixel Clock I L16

131* csi.PIXCLK Pixel Clock I E5

83* csi.VSYNC Vertical Sync (Start Of Frame) I N17

127* csi.VSYNC Vertical Sync (Start Of Frame) I F2

85* csi.HSYNC Horizontal Sync (Blank Signal) I M15

129* csi.HSYNC Horizontal Sync (Blank Signal) I F3

Table 7 - Camera interface signals

Note: -

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 21

4.6 I2C Interface

VT-SOM-6UL supports four general purpose I2C interfaces with Standard and Fast mode of operation.

It has the following key features.

- Compatibility with I2C bus standard

- Multimaster operation

- Software programmability for one of 64 different serial clock frequencies

- Arbitration-lost interrupt with automatic mode switching from master to slave

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual chapter: 29 I2C Controller (I2C).

Pin # Signal name Description Type SoC Pin #

81 I2C1_SCL Serial Clock IO L14

87* I2C1_SCL Serial Clock IO G17

131* I2C1_SCL Serial Clock IO E5

79 I2C1_SDA Serial Data IO L17

93* I2C1_SDA Serial Data IO G16

133* I2C1_SDA Serial Data IO F5

65* I2C2_SCL Serial Clock IO K13

89* I2C2_SCL Serial Clock IO F17

129* I2C2_SCL Serial Clock IO F3

91* I2C2_SDA Serial Data IO G13

127* I2C2_SDA Serial Data IO F2

199* I2C2_SDA Serial Data IO L15

98*/** I2C3_SCL Serial Clock IO A9

110* I2C3_SCL Serial Clock IO K14

155* I2C3_SCL Serial Clock IO C17

94*/** I2C3_SDA Serial Data IO B9

112* I2C3_SDA Serial Data IO K16

157* I2C3_SDA Serial Data IO C16

90*/** I2C4_SCL Serial Clock IO D10

120* I2C4_SCL Serial Clock IO J17

167* I2C4_SCL Serial Clock IO B17

88*/** I2C4_SDA Serial Data IO E10

122* I2C4_SDA Serial Data IO J16

169* I2C4_SDA Serial Data IO A15

Table 8 - I2C interface signals

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 22

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

4.7 ECSPI Interface

VT-SOM-6UL supports four ECSPI interfaces. The Enhanced Configurable Serial Peripheral Interface

(ECSPI) is a full-duplex, synchronous, four-wire serial communication block.

It has the following key features.

- Full-duplex synchronous serial interface with data rate up to 52 Mbit/s

- Master/Slave configurable

- Four Chip Select (SS) signals to support multiple peripherals

- Transfer continuation function allows unlimited length data transfers

- 32-bit wide by 64-entry FIFO for both transmit and receive data

- Polarity and phase of the Chip Select (SS) and SPI Clock (SCLK) are configurable

- Direct Memory Access (DMA) support

- Max operation frequency up to the reference clock frequency

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual chapter: 20 ECSPI

Pin # Signal name Description Type SoC Pin #

145* ECXSPI1_SCLK Serial Clock IO D4

52*/** ECXSPI1_SCLK Serial Clock IO C14

66*/** ECSPI1_MOSI Master Out Slave In IO A14

149* ECSPI1_MOSI Master Out Slave In IO D2

56*/** ECSPI1_MISO Master In Slave Out IO B16

151* ECSPI1_MISO Master In Slave Out IO D1

58*/** ECSPI1_SS0 Slave Select zero IO B14

147* ECSPI1_SS0 Slave Select zero IO D3

80*/** ECSPI1_SS1 Slave Select one IO B10

84*/** ECSPI1_SS2 Slave Select two IO A10

86*/** ECSPI1-SS3 Slave Select three IO D11

72*/** ECSPI1_RDY Ready O C12

87* ECSPI2_SCLK Serial Clock IO G17

137* ECSPI2_SCLK Serial Clock IO E4

89* ECSPI2_MOSI Master Out Slave In IO F17

141* ECSPI2_MOSI Master Out Slave In IO E2

91* ECSPI2_MISO Master In Slave Out IO G13

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 23

143* ECSPI2_MISO Master In Slave Out IO E1

93* ECSPI2_SS0 Slave Select zero IO G16

139* ECSPI2_SS0 Slave Select zero IO E3

92* ECSPI2_SS1 Slave Select one IO D9

102* ECSPI2_SS2 Slave Select two IO C9

100* ECSPI2-SS3 Slave Select three IO E9

106* ECSPI2_RDY Ready O B8

122* ECSPI3_SCLK Serial Clock IO J16

162*/# ECSPI3_SCLK Serial Clock IO C5

124* ECSPI3_MOSI Master Out Slave In IO J15

164*/# ECSPI3_MOSI Master Out Slave In IO B5

126* ECSPI3_MISO Master In Slave Out IO H14

166*/# ECSPI3_MISO Master In Slave Out IO A4

120* ECSPI3_SS0 Slave Select zero IO J17

160*/# ECSPI3_SS0 Slave Select zero IO A3

158*/# ECSPI3_RDY Ready O D5

140* ECSPI4_SCLK Serial Clock IO A16

136* ECSPI4_MOSI Master Out Slave In IO B15

138* ECSPI4_MISO Master In Slave Out IO D17

142* ECSPI4_SS0 Slave Select zero IO D16

Table 9 - ECSPI interface signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

- Pins denoted by (#) can only be accessible with eMMC flash configuration on SOM board.

4.8 QuadSPI

The Quad Serial Peripheral Interface (QuadSPI) block acts as an interface to external serial flash

device.

Note: - QSPI interface can only be accessible with eMMC flash configuration on SOM board.

It has the following key features

- Flexible sequence engine to support various flash vendor devices. - Single, dual, quad mode of operation.

- DDR/DTR mode wherein the data is generated on every edge of the serial flash clock.

- Memory mapped read access to connected flash devices.

- Programmable sequence engine to cater to future command/protocol changes and able to

support all existing vendor commands and operations.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 24

- Supports 3-byte and 4-byte addressing.

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual Chapter: 40 Quad Serial Peripheral Interface

Pin # Signal name Description Type SoC Pin #

158*/# QSPI_A_SCLK Serial clock output 1 to serial flash O D5

173*/# QSPI_A_SS0_B Chip select 1 port 0 for serial flash device A O E6

160*/# QSPI_A_DATA 0 I/O data signal 1 port 0 for serial flash device A IO A3

162*/# QSPI_A_DATA 1 I/O data signal 1 port 1 for serial flash device A IO C5

164*/# QSPI_A_DATA 2 I/O data signal 1 port 2 for serial flash device A IO B5

166*/# QSPI_A_DATA 3 I/O data signal 1 port 3 for serial flash device A IO A4

Table 10 - QSPI interface signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of this

document.

- Pins denoted by (#) can only be accessible with eMMC flash configuration on SOM board.

4.9 UART Interface

The VT-SOM-6UL has 8 UART (Universal Asynchronous Transmitter/Receiver) Interface. This

Interface has a Capability to communicate with external devices through a level converter and an RS-232

cable or through use of external circuitry that converts infrared signals to electrical signals (for reception)

or transforms electrical signals to signals that drive an infrared LED (for transmission) to provide low speed

IrDA compatibility.

It has the following key features.

- 9-bit or Multidrop mode (RS-485) support (automatic slave address detection)

- Serial IR interface low-speed, IrDA-compatible (up to 115.2 Kbit/s)

- 7 or 8 data bits for RS-232 characters, or 9 bit RS-485 format

- 1 or 2 stop bits

- Programmable parity (even, odd, and no parity)

- Hardware flow control support for request to send (RTS_B) and clear to send (CTS_B) signals

- RX_DATA input and TX_DATA output can be inverted respectively in RS-232/ RS-485 mode

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual Chapter: 53 Universal Asynchronous Receiver /Transmitter (UART).

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 25

Pin # Signal name Description Type SoC Pin #

110* UART1_TxD Serial / Infrared Data Transmit (Debug port)

I K14

112* UART1_RxD Serial /Infrared Data Receive (Debug port)

O K16

114* UART1_CTS Clear to send I K15

199 UART1_CTS Clear to send I K17

116* UART1_RTS Request to send O J14

200* UART1_RTS Request to send O L16

120* UART2_TxD Serial / Infrared Data Transmit I J17

122* UART2_RxD Serial /Infrared Data Receive O J16

124* UART2_CTS Clear to send I J15

130* UART2_CTS Clear to send I H17

126* UART2_RTS Request to send O H14

132* UART2_RTS Request to send O H16

130 UART3_TxD Serial / Infrared Data Transmit I H17

160*/# UART3_TxD Serial / Infrared Data Transmit I A3

132* UART3_RxD Serial / Infrared Data Receive I H16

162*/# UART3_RxD Serial /Infrared Data Receive O C5

163* UART3_CTS Clear to send I H15

164*/# UART3_CTS Clear to send I B5

161* UART3_RTS Request to send O G14

166*/# UART3_RTS Request to send O A4

87* UART4_TxD Serial / Infrared Data Transmit I G17

104* UART4_TxD Serial / Infrared Data Transmit I A8

93* UART4_RxD Serial / Infrared Data Receive O G16

106* UART4_RxD Serial /Infrared Data Receive O B8

92* UART4_CTS Clear to send I D9

102* UART4_RTS Request to send O C9

89* UART5_TxD Serial / Infrared Data Transmit I F17

137 UART5_TxD Serial / Infrared Data Transmit I E4

75* UART5_TxD Serial / Infrared Data Transmit I M16

91* UART5_RxD Serial / Infrared Data Receive O G13

139* UART5_RxD Serial /Infrared Data Receive O E3

55* UART5_RxD Serial /Infrared Data Receive O M17

141* UART5_CTS Clear to send I E2

85* UART5_CTS Clear to send I M15

83* UART5_RTS Request to send O N17

143* UART5_RTS Request to send O E1

133* UART6_TxD Serial / Infrared Data Transmit I F5

155* UART6_TxD Serial / Infrared Data Transmit I C17

131* UART6_RxD Serial / Infrared Data Receive O E5

157* UART6_RxD Serial /Infrared Data Receive O C16

129* UART6_CTS Clear to send I F3

127* UART6_RTS Request to send O F2

167* UART7_TxD Serial / Infrared Data Transmit I B17

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 26

60*/** UART7_TxD Serial / Infrared Data Transmit I C13

169* UART7_RxD Serial / Infrared Data Receive O A15

62*/** UART7_RxD Serial /Infrared Data Receive O B13

84*/** UART7_CTS Clear to send I A10

86*/** UART7_RTS Request to send O D11

52*/** UART8_TxD Serial / Infrared Data Transmit I C14

140* UART8_TxD Serial / Infrared Data Transmit I A16

58*/** UART8_RxD Serial /Infrared Data Receive O B14

136* UART8_RxD Serial /Infrared Data Receive O B15

138* UART8_CTS Clear to send I D17

82*/** UART8_CTS Clear to send I C10

142* UART8_RTS Request to send O D16

80*/** UART8_RTS Request to send O B10

Table 11 - UART interface signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of this

document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

- Pins denoted by (#) can only be accessible with eMMC flash configuration on SOM board.

4.10 SAI Interface

VT-SOM-6UL supports three SAI interfaces. The synchronous audio interface (SAI) supports full-

duplex serial interfaces with frame synchronization such as I2S, AC97, TDM, and codec/DSP interfaces.

It has the following key features.

- Transmitter with independent bit clock and frame sync supporting 1 data line

- Receiver with independent bit clock and frame sync supporting 1 data line

- Maximum Frame Size of 32 words

- Word size of between 8-bits and 32-bits

- Word size configured separately for first word and remaining words in frame

Note that some of the features are not supported across all SAI instances. For more detailed

information, please refer to the i.MX6UL Applications Processor Reference Manual chapter: 42

Synchronous Audio Interface (SAI).

Pin # Signal name Description Type SoC Pin #

94*/** SAI1_MCLK Audio Master Clock. The master clock is an input when externally generated and an output when internally generated.

IO B9

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 27

139* SAI1_MCLK Audio Master Clock. The master clock is an input when externally generated and an output when internally generated.

IO E3

147* SAI1_TX_BCLK Transmit Bit Clock. The bit clock is an input when externally generated and an output when internally generated.

IO D3

88*/** SAI1_TX_BCLK Transmit Bit Clock. The bit clock is an input when externally generated and an output when internally generated

IO E10

143*

SAI1_RX_BCLK Receive Bit Clock. The bit clock is an input when externally generated and an output when internally generated.

IO E1

145* SAI1_TX_SYNC Transmit Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated.

IO D4

98*/** SAI1_TX_SYNC Transmit Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated.

IO A9

141* SAI1_RX_SYNC Receive Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated.

IO E2

151* SAI1_TX_DATA Transmit Data. The transmit data is generated synchronously by the bit clock and is tristated whenever not transmitting a word.

O D1

82*/** SAI1_TX_DATA Transmit Data. The transmit data is generated synchronously by the bit clock and is tristated whenever not transmitting a word.

O C10

149* SAI1_RX_DATA Receive Data. The receive data is sampled synchronously by the bit clock.

I D2

90*/** SAI1_RX_DATA Receive Data. The receive data is sampled synchronously by the bit clock.

I D10

178* SAI2_MCLK Audio Master Clock. The master clock is an input when externally generated and an output when internally generated.

IO P14

97* SAI2_MCLK Audio Master Clock. The master clock is an input when externally generated and an output when internally generated.

IO C1

103* SAI2_TX_BCLK Transmit Bit Clock. The bit clock is an input when externally generated and an output when internally generated

IO B2

172* SAI2_TX_BCLK Transmit Bit Clock. The bit clock is an input when externally generated and an output when internally generated

IO N16

101* SAI2_TX_SYNC Transmit Frame Sync. The frame sync is an input sampled synchronously by the bit clock when

IO B3

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 28

externally generated and an output generated synchronously by the bit clock when internally generated.

170* SAI2_TX_SYNC Transmit Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated.

IO N15

99* SAI2_RX_SYNC Receive Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated

IO C2

176* SAI2_TX_DATA Transmit Data. The transmit data is generated synchronously by the bit clock and is tristated whenever not transmitting a word.

O N14

107* SAI2_TX_DATA Transmit Data. The transmit data is generated synchronously by the bit clock and is tristated whenever not transmitting a word.

O A2

174* SAI2_RX_DATA Receive Data. The receive data is sampled synchronously by the bit clock.

I M14

105* SAI2_RX_DATA Receive Data. The receive data is sampled synchronously by the bit clock.

I B1

104*

SAI3_MCLK Audio Master Clock. The master clock is an input when externally generated and an output when internally generated.

IO A8

78*/** SAI3_MCLK Audio Master Clock. The master clock is an input when externally generated and an output when internally generated.

IO A11

92* SAI3_TX_BCLK Transmit Bit Clock. The bit clock is an input when externally generated and an output when internally generated

IO D9

70*/** SAI3_TX_BCLK Transmit Bit Clock. The bit clock is an input when externally generated and an output when internally generated

IO B12

64*/** SAI3_RX_BCLK Receive Bit Clock. The bit clock is an input when externally generated and an output when internally generated

IO D12

106* SAI3_TX_SYNC Transmit Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated.

IO B8

72*/** SAI3_TX_SYNC Transmit Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated.

IO C12

54*/** SAI3_RX_SYNC Receive Frame Sync. The frame sync is an input sampled synchronously by the bit clock when externally generated and an output generated synchronously by the bit clock when internally generated.

IO E12

100* SAI3_TX_DATA Transmit Data. The transmit data is generated synchronously by the bit clock and is tristated whenever not transmitting a word.

O E9

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 29

48*/** SAI3_TX_DATA Transmit Data. The transmit data is generated synchronously by the bit clock and is tristated whenever not transmitting a word.

O D13

102* SAI3_RX_DATA Receive Data. The receive data is sampled synchronously by the bit clock.

I C9

76*/** SAI3_RX_DATA Receive Data. The receive data is sampled synchronously by the bit clock.

I A12

Table 12 - SAI interface signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of this

document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

4.11 MQS Interface

Medium quality sound (MQS) is used to generate medium quality audio. It is allowing the user to

connect stereo speakers or headphones to a power amplifier without an additional DAC chip. MQS accepts

2-channel, LSB-valid 16bit, MSB shift-out first; frame sync asserting with the first bit of the frame, data

shifted with the pos edge of bit clock, 44.1 kHz or 48 kHz signals from SAI1 in left justified format; and it

provides the SNR target as no more than 20dB for the signals below 10 kHz. The signals above 10 kHz will

have worse THD+N values.

MQS provides only simple audio reproduction. No internal pop, click or distortion artifact

reduction methods are provided.

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter : 34 Medium Quality Sound

Pin # Signal name Description Type SoC Pin #

172* MQS_LEFT Left Signal Output O N16

77* MQS_LEFT Left Signal Output O L15

56*/** MQS_LEFT Left Signal Output O B16

170* MQS_RIGHT Right Signal Output O N15

65* MQS_RIGHT Right Signal Output O K13

66*/** MQS_RIGHT Right Signal Output O A14

Table 13 - MQA interface signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of this

document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 30

4.12 PWM Interface

The Pulse Width Modulation (PWM) has a 16-bit counter, and is optimized to generate sound

from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4 x 16 data

FIFO.

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 38 Pulse Width Modulation

Pin # Signal name Description Type SoC Pin #

83* PWM1_OUT This is the PWM1 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O N17

94*/** PWM1_OUT This is the PWM1 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O B9

98*/** PWM2_OUT This is the PWM2 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O A9

85* PWM2_OUT This is the PWM2 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O M15

75* PWM3_OUT This is the PWM3 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O M16

88*/** PWM3_OUT This is the PWM3 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O E10

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 31

55* PWM4_OUT This is the PWM4 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O M17

90*/** PWM4_OUT This is the PWM4 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O D10

158*/# PWM4_OUT This is the PWM4 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O D5

68*/** PWM5_OUT This is the PWM5 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O A13

173*/# PWM5_OUT This is the PWM5 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O E6

172* PWM6_OUT This is the PWM6 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O N16

50*/** PWM6_OUT This is the PWM6 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O D14

127* PWM7_OUT This is the PWM6 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle

O F2

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 32

can be varied with different settings of the cycle of 50%.

174* PWM7_OUT This is the PWM6 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O M14

129* PWM8_OUT This is the PWM6 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O F3

176* PWM8_OUT This is the PWM6 functional output of the PWM. A modulated signal of the block is observed at this pin. It can be viewed as a clock signal whose period and duty cycle can be varied with different settings of the cycle of 50%.

O N14

Table 14 - PWM interface signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of this

document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

- Pins denoted by (#) can only be accessible with eMMC flash configuration on SOM board.

4.13 GPIO Interface

The GPIO (General-purpose input/output peripheral) provides dedicated general-purpose pins that

can be configured as either inputs or outputs.

The GPIO functionality is provided through eight registers, an edge-detect circuit, interrupt

generation logic.

GPIO includes the following features:

- General purpose input/output logic capabilities:

- Drives specific data to output using the data register

- Controls the direction of the signal using the GPIO direction register

- Enables the core to sample the status of the corresponding inputs by reading the pad

sample register

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 33

- GPIO interrupt capabilities:

- Supports up to 32 interrupts

- Identifies interrupt edges

- Generates three active-high interrupts to the SoC interrupt controller

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

Chapter 26: General Purpose Input/output (GPIO).

Pin # Signal name Description Type SoC Pin #

65* GPIO1_IO[0] General purpose Input output 1 Signal 0 IO K13

77* GPIO1_IO[1] General purpose Input output 1 Signal 1 IO L15

75* GPIO1_IO[4] General purpose Input output 1 Signal 4 IO M16

55* GPIO1_IO[5] General purpose Input output 1 Signal 5 IO M17

199* GPIO1_IO[6] General purpose Input output 1 Signal 6 IO K17

200* GPIO1_IO[7] General purpose Input output 1 Signal 7 IO L16

83* GPIO1_IO[8] General purpose Input output 1 Signal 8 IO N17

85* GPIO1_IO[9] General purpose Input output 1 Signal 9 IO M15

171* GPIO1_IO[10] General purpose Input output 1 Signal 10 IO P15

178* GPIO1_IO[11] General purpose Input output 1 Signal 11 IO P14

170* GPIO1_IO[12] General purpose Input output 1 Signal 12 IO N15

172* GPIO1_IO[13] General purpose Input output 1 Signal 13 IO N16

174* GPIO1_IO[14] General purpose Input output 1 Signal 14 IO M14

176* GPIO1_IO[15] General purpose Input output 1 Signal 15 IO N14

110* GPIO1_IO[16] General purpose Input output 1 Signal 16 IO K14

112* GPIO1_IO[17] General purpose Input output 1 Signal 17 IO K16

114* GPIO1_IO[18] General purpose Input output 1 Signal 18 IO K15

116* GPIO1_IO[19] General purpose Input output 1 Signal 19 IO J14

120* GPIO1_IO[20] General purpose Input output 1 Signal 20 IO J17

122* GPIO1_IO[21] General purpose Input output 1 Signal 21 IO J16

124* GPIO1_IO[22] General purpose Input output 1 Signal 22 IO J15

126* GPIO1_IO[23] General purpose Input output 1 Signal 23 IO H14

130* GPIO1_IO[24] General purpose Input output 1 Signal 24 IO H17

132* GPIO1_IO[25] General purpose Input output 1 Signal 25 IO H16

163* GPIO1_IO[26] General purpose Input output 1 Signal 26 IO H15

161* GPIO1_IO[27] General purpose Input output 1 Signal 27 IO G14

87* GPIO1_IO[28] General purpose Input output 1 Signal 28 IO G17

93* GPIO1_IO[29] General purpose Input output 1 Signal 29 IO G16

89* GPIO1_IO[30] General purpose Input output 1 Signal 30 IO F17

91* GPIO1_IO[31] General purpose Input output 1 Signal 31 IO G13

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 34

155* GPIO2_IO[8] General purpose Input output 2 Signal 8 IO C17

157* GPIO2_IO[9] General purpose Input output 1 Signal 9 IO C16

167* GPIO2_IO[10] General purpose Input output 2 Signal 10 IO B17

169* GPIO2_IO[11] General purpose Input output 2 Signal 11 IO A15

140* GPIO2_IO[12] General purpose Input output 2 Signal 12 IO A16

136* GPIO2_IO[13] General purpose Input output 2 Signal 13 IO B15

138* GPIO2_IO[14] General purpose Input output 2 Signal 14 IO D17

142* GPIO2_IO[15] General purpose Input output 2 Signal 15 IO D16

99* GPIO2_IO[16] General purpose Input output 2 Signal 16 IO C2

97* GPIO2_IO[17] General purpose Input output 2 Signal 17 IO C1

101* GPIO2_IO[18] General purpose Input output 2 Signal 18 IO B3

103* GPIO2_IO[19] General purpose Input output 2 Signal 19 IO B2

105* GPIO2_IO[20] General purpose Input output 2 Signal 20 IO B1

107* GPIO2_IO[21] General purpose Input output 2 Signal 21 IO A2

104* GPIO3_IO[0] General purpose Input output 3 Signal 0 IO A8

106* GPIO3_IO[1] General purpose Input output 3 Signal 1 IO B8

92* GPIO3_IO[2] General purpose Input output 3 Signal 2 IO D9

102* GPIO3_IO[3] General purpose Input output 3 Signal 3 IO C9

100* GPIO3_IO[4] General purpose Input output 3 Signal 4 IO E9

94*/** GPIO3_IO[5] General purpose Input output 3 Signal 5 IO B9

98*/** GPIO3_IO[6] General purpose Input output 3 Signal 6 IO A9

88*/** GPIO3_IO[7] General purpose Input output 3 Signal 7 IO E10

90*/** GPIO3_IO[8] General purpose Input output 3 Signal 8 IO D10

82*/** GPIO3_IO[9] General purpose Input output 3 Signal 9 IO C10

80*/** GPIO3_IO[10] General purpose Input output 3 Signal 10 IO B10

84*/** GPIO3_IO[11] General purpose Input output 3 Signal 11 IO A10

86*/** GPIO3_IO[12] General purpose Input output 3 Signal 12 IO D11

74*/** GPIO3_IO[13] General purpose Input output 3 Signal 13 IO B11

78*/** GPIO3_IO[14] General purpose Input output 3 Signal 14 IO A11

54*/** GPIO3_IO[15] General purpose Input output 3 Signal 15 IO E12

64*/** GPIO3_IO[16] General purpose Input output 3 Signal 16 IO D12

72*/** GPIO3_IO[17] General purpose Input output 3 Signal 17 IO C12

70*/** GPIO3_IO[18] General purpose Input output 3 Signal 18 IO B12

76*/** GPIO3_IO[19] General purpose Input output 3 Signal 19 IO A12

48*/** GPIO3_IO[20] General purpose Input output 3 Signal 20 IO D13

60*/** GPIO3_IO[21] General purpose Input output 3 Signal 21 IO C13

62*/** GPIO3_IO[22] General purpose Input output 3 Signal 22 IO B13

68*/** GPIO3_IO[23] General purpose Input output 3 Signal 23 IO A13

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 35

50*/** GPIO3_IO[24] General purpose Input output 3 Signal 24 IO D14

52*/** GPIO3_IO[25] General purpose Input output 3 Signal 25 IO C14

58*/** GPIO3_IO[26] General purpose Input output 3 Signal 26 IO B14

66*/** GPIO3_IO[27] General purpose Input output 3 Signal 27 IO A14

56*/** GPIO3_IO[28] General purpose Input output 3 Signal 28 IO B16

158*/# GPIO4_IO[11] General purpose Input output 4 Signal 11 IO D5

160*/# GPIO4_IO[12] General purpose Input output 4 Signal 12 IO A3

162*/# GPIO4_IO[13] General purpose Input output 4 Signal 13 IO C5

164*/# GPIO4_IO[14] General purpose Input output 4 Signal 14 IO B5

166*/# GPIO4_IO[15] General purpose Input output 4 Signal 15 IO A4

173*/# GPIO4_IO[16] General purpose Input output 4 Signal 16 IO E6

133* GPIO4_IO[17] General purpose Input output 4 Signal 17 IO F5

131* GPIO4_IO[18] General purpose Input output 4 Signal 18 IO E5

127* GPIO4_IO[19] General purpose Input output 4 Signal 19 IO F2

129* GPIO4_IO[20] General purpose Input output 4 Signal 20 IO F3

137* GPIO4_IO[21] General purpose Input output 4 Signal 21 IO E4

139* GPIO4_IO[22] General purpose Input output 4 Signal 22 IO E3

141* GPIO4_IO[23] General purpose Input output 4 Signal 23 IO E2

143* GPIO4_IO[24] General purpose Input output 4 Signal 24 IO E1

145* GPIO4_IO[25] General purpose Input output 4 Signal 25 IO D4

147* GPIO4_IO[26] General purpose Input output 4 Signal 26 IO D3

149* GPIO4_IO[27] General purpose Input output 4 Signal 27 IO D2

151* GPIO4_IO[28] General purpose Input output 4 Signal 28 IO D1

144* GPIO5_IO[4] General purpose Input output 5 Signal 4 IO P9

146* GPIO5_IO[5] General purpose Input output 5 Signal 5 IO N8

148* GPIO5_IO[6] General purpose Input output 5 Signal 6 IO N11

150* GPIO5_IO[7] General purpose Input output 5 Signal 7 IO N10

152* GPIO5_IO[8] General purpose Input output 5 Signal 8 IO N9

154* GPIO5_IO[9] General purpose Input output 5 Signal 9 IO R6

Table 15 - GPIO Signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of this

document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

- Pins denoted by (#) can only be accessible with eMMC flash configuration on SOM board.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 36

4.14 System JTAG Controller

The System JTAG Controller (SJC) provides debug and test control with the maximum security. The

test access port (TAP) is designed to support features compatible with the IEEE Standard 1149.1 v2001

(JTAG).

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 45 System JATG Controller.

Pin # Signal name Description Type SoC Pin #

173*

JTAG_MOD

SJC mode selection. This pin is sampled at TRST reset to determine two possible modes for the TAP connection

configuration.

100K internal Pullup

I

P15

178*

JTAG_TMS

Test Mode Select (TMS). This is used to sequence the test controller's state machine. TMS is sampled on the rising edge of TCK and includes an internal pullup resistor.

47K internal Pullup

I

P14

170*

JTAG_TDO

Test Data Output (TDO). The serial output for test instructions and data. TDO is tri-statable and is actively driven in the shift-IR and shift-DR controller states. TDO changes on the falling edge of TCK.

100K internal Pullup

O

N15

172*

JTAG_TDI

Test Data Input (TDI). Serial test instruction and data are received through the test data input (TDI) pin. TDI is sampled on the rising edge of TCK and includes an internal pullup resistor.

47K internal Pullup

I

N16

174*

JTAG_TCK

Test Clock (TCK). This is used to synchronize the test logic and includes an internal pull-up resistor

47K internal Pullup

I

M14

176* JTAG_TRST_B Test Reset (TRST). This is used to asynchronously initialize the test

I N14

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 37

controller. The TRST pin has an internal pullup resistor.

47K internal Pullup

Table 16 - JTAG Interface signals

Note: - Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

4.15 Sony/Philips Digital Interface (SPDIF)

The Sony/Philips Digital Interface (SPDIF) audio block is a stereo transceiver that allows the

processor to receive and transmit digital audio. The SPDIF transceiver allows the handling of both SPDIF

channel status (CS) and User (U) data and includes a frequency measurement block that allows the precise

measurement of an incoming sampling frequency.

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 48 Sony/Philips Digital Interface.

Pin # Signal name Description Type SoC Pin #

173* SPDIF_OUT Output line signal O P15

83* SPDIF_OUT Output line signal O N17

110* SPDIF_OUT Output line signal O K14

80*/** SPDIF_OUT Output line signal O B10

99* SPDIF_OUT Output line signal O C2

85* SPDIF_IN Input line signal I M15

112* SPDIF_IN Input line signal I K16

74*/** SPDIF_IN Input line signal I B11

97* SPDIF_IN Input line signal I C1

82*/** SPDIF_SR_CLK SR Clock Signal O C10

86*/** SPDIF_EXT_CLK External clock signal I D11

173*/# SPDIF_EXT_CLK External clock signal I E6

84*/** SPDIF_LOCK Lock signal O A10

Table 17 - SPDIF Interface Signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

- Pins denoted by double Asterisk (**) are used as a boot straps pins. Loading these pins result in

wrong boot or no SOM bootup.

- Pins denoted by (#) can only be accessible with eMMC flash configuration on SOM board.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 38

4.16 Analog to Digital Converter (ADC)

The analog-to-digital converter (ADC) is a successive approximation ADC designed for

operation within an integrated microcontroller system-on-chip.

It has the following key features.

- Linear successive approximation algorithm with up to 12-bit resolution with 10/11 bit accuracy

- Up to 10 ENOB (dedicated Single Ended Channels)

- Up to 1MS/s sampling rate

- Up to 16 single-ended external analog inputs

- Single or continuous conversion (automatic return to idle after single conversion)

- 8/10/12 bit Output Modes

- Configurable sample time and conversion speed/power

- Conversion complete and hardware average complete flag and interrupt

- Configurable sample time and conversion speed/power

- Conversion complete and hardware average complete flag and interrupt

- Input clock selectable from up to four sources

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter: 13 Analog to Digital Converter.

Pin # Signal name Description Type SoC Pin #

65* ADC1_IN0 Analog Channel 1 Input 0 I K13

65* ADC2_IN0 Analog Channel 2 Input 0 I K13

77* ADC1_IN1 Analog Channel 1 Input 1 I L15

77* ADC2_IN1 Analog Channel 2 Input 1 I L15

75* ADC1_IN4 Analog Channel 1 Input 4 I M16

75* ADC2_IN4 Analog Channel 2 Input 4 I M16

55* ADC1_IN5 Analog Channel 1 Input 5 I M17

55* ADC2_IN5 Analog Channel 2 Input 5 I M17

199* ADC1_IN6 Analog Channel 1 Input 6 I K17

199* ADC2_IN6 Analog Channel 2 Input 6 I K17

200* ADC1_IN7 Analog Channel 1 Input 7 I L16

200* ADC2_IN7 Analog Channel 2 Input 7 I L16

83* ADC1_IN8 Analog Channel 1 Input 8 I N17

83* ADC2_IN8 Analog Channel 2 Input 8 I N17

85* ADC1_IN9 Analog Channel 1 Input 9 I M15

85* ADC2_IN9 Analog Channel 2 Input 9 I M15

Table 18 - Analog Input Signals

Note:-

- Pins denoted with Asterisk (*) are multifunctional. For more detail, please refer chapter – 10 of

this document.

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 39

4.17 Ultra-Secured Digital Host Controller (uSDHC)

The Ultra Secured Digital Host Controller (uSDHC) provides the interface between the host system

and the SD/SDIO/MMC cards. The uSDHC acts as a bridge, passing host bus transactions to the

SD/SDIO/MMC cards by sending commands and performing data accesses to/from the cards.

It has the following key features.

- Conforms to the SD Host Controller Standard Specification version 3.0

- Compatible with the MMC System Specification version 4.2/4.3/4.4/4.41

- Compatible with the SD Memory Card Specification version 3.0 and supports the Extended Capacity

SD Memory Card

- Compatible with the SDIO Card Specification version 3.0

- Designed to work with SD Memory, miniSD Memory, SDIO, miniSDIO, SD Combo, MMC, MMC plus,

and MMC RS cards

- Card bus clock frequency up to 208 MHz

- Supports 1-bit / 4-bit SD and SDIO modes, 1-bit / 4-bit / 8-bit MMC modes

For more detailed information, please refer to the i.MX6UL Applications Processor Reference Manual

chapter : 56 Ultra Secured Digital Host Controller.

Pin # Signal name Description Type SoC Pin #

97* SD1_CLK Clock for MMC/SDIO/SD card O C1

127* SD2_CLK Clock for MMC/SDIO/SD card O F2

50*/** SD2_CLK Clock for MMC/SDIO/SD card O D14

99* SD1_CMD CMD line Connect to line IO C2

129* SD2_CMD CMD line Connect to line IO F3

68*/** SD2_CMD CMD line Connect to line IO A13

101* SD1_DATA0 DATA0 line in all modes Also used to detect busy status

IO B3

103* SD1_DATA1 DATA1 line in 4/8-bit mode Also used to detect interrupt in 1/4-bit mode

IO B2

105* SD1_DATA2 DATA2 line or Read Wait in 4-bit mode Read Wait in 1-bit mode

IO B1

107* SD1_DATA3 DATA3 line in 4/8-bit mode or configured as card detection pin May be configured as card detection pin in 1-bit mode

IO

A2

160*/# SD1_DATA4 DATA7 line in 8-bit mode, not used in other modes

IO A3

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 40

162*/# SD1_DATA5 DATA7 line in 8-bit mode, not used in other modes

IO C5

164*/# SD1_DATA6 DATA7 line in 8-bit mode, not used in other modes

IO B5

166*/# SD1_DATA7 DATA7 line in 8-bit mode, not used in other modes

IO A4

52*/** SD2_DATA0 DATA0 line in all modes Also used to detect busy status

IO C14

58*/** SD2_DATA1 DATA1 line in 4/8-bit mode Also used to detect interrupt in 1/4-bit mode

IO B14

66*/** SD2_DATA2 DATA2 line or Read Wait in 4-bit mode Read Wait in 1-bit mode

IO A14

56*/** SD2_DATA3 DATA3 line in 4/8-bit mode or configured as card detection pin May be configured as card detection pin in 1-bit mode

IO

B16

76*/** SD2_DATA4 DATA7 line in 8-bit mode, not used in other modes

IO A12

48*/** SD2_DATA5 DATA7 line in 8-bit mode, not used in other modes

IO D13

60*/** SD2_DATA6 DATA7 line in 8-bit mode, not used in other modes

IO C13

62*/** SD2_DATA7 DATA7 line in 8-bit mode, not used in other modes

IO B13

137* SD2_DATA0 DATA0 line in all modes Also used to detect busy status

IO E4

139* SD2_DATA1 DATA1 line in 4/8-bit mode Also used to detect interrupt in 1/4-bit mode

IO E3

141* SD2_DATA2 DATA2 line or Read Wait in 4-bit mode Read Wait in 1-bit mode

IO E2

143* SD2_DATA3 DATA3 line in 4/8-bit mode or configured as card detection pin May be configured as card detection pin in 1-bit mode

IO

E1

VT-SOM-6UL Datasheet

Doc. Num: xxxyyyzzz Confidential Copyright © 2016 Volansys September 15, 2016 Volansys Technologies Page | 41

145* SD2_DATA4 DATA7 line in 8-bit mode, not used in other modes

IO D4

147* SD2_DATA5 DATA7 line in 8-bit mode, not used in other modes

IO D3

149* SD2_DATA6 DATA7 line in 8-bit mode, not used in other modes

IO D2

151* SD2_DATA7 DATA7 line in 8-bit mode, not used in other modes

IO D1

85* SD1_RESET_B Card hardware reset signal, active LOW

O M15

158*/# SD1_RESET_B Card hardware reset signal, active LOW

O D5

149* SD1_RESET_B Card hardware reset signal, active LOW

O D2

75* SD1_RESET_B Card hardware reset signal, active LOW

O M16

85* SD2_RESET_B Card hardware reset signal, active LOW

O M15

70*/** SD2_RESET_B Card hardware reset signal, active LOW

O B12