VHDL (Very High Speed Integrated Circuit HDL (VHSIC HDL)) GRECO CIn-UFPE.

-

Upload

julio-brandt-castanho -

Category

Documents

-

view

227 -

download

0

Transcript of VHDL (Very High Speed Integrated Circuit HDL (VHSIC HDL)) GRECO CIn-UFPE.

VHDL (Very High Speed Integrated Circuit HDL (VHSIC HDL))

GRECO

CIn-UFPE

Objetivo das Linguagens

Execução de um

algorítimo

Instruçõesseqüenciais

Linguagem de

programação

Objetivo das Linguagens

Características Gerais– linguagem procedural

• estruturada em funções e procedimentos

int soma (int a, int b) {return (a + b);}

compilador

Linguagem de Programação (HLL)

Programa Processador

Objetivo das HDL’s

Descrever Sistemas

Eletrônicos

Circuitoscombinacionais

hierarquia

componentes

Circuitosseqüenciais

concorrência

Reusabilidade

Ferramentade

Síntese

Linguagem de Descrição de Hardware (HDL)

DescriçãoMapeamento

de tecnologia

O que é síntese? Synthesis é um termo geral que descreve o processo

de transformação do modelo de origem, usualmente descrito em uma HDL, de um nível de abstratção comportamental para um nível comportametal mais baixo e detalhado.

Estas transformações tentam melhorar um conjunto de métricas, tais como: área, velocidade, dissipação de potência de um projeto. Ao mesmo tempo o processo de síntese deve satisfazer um conjunto de restrições, tais como: MIPS, freqüência de operação, taxa de I/O.

HDL’s

Algumas Linguagens de Descrição de Hardware– VHDL– Verilog (indústria americana, Motorola, ...)– HardwareC– Handel-C– C++– SystemC– Java– etc.

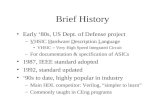

Introdução a VHDL VHDL - Very High Speed Integrated Circuit HDL (VHSIC HDL)

• É uma linguagem para descrição de hardware que permite ao usuário descrever circuitos de maneira estrutural (RTL) ou comportamental.

Circuitos digitais

Circuitos Analógicos (AVHDL)

Process(d,clk)Process(d,clk)BeginBegin if clk='1' thenif clk='1' then Q<=d;Q<=d; end if;end if;end Process;end Process;

ComportamentalComportamentalArquiteturalArquitetural

EstruturalEstrutural

ASIC/FPGAASIC/FPGA

Estação deEstação de trabalhotrabalhoEquipamentoEquipamento

modeladormodelador

Modelamento de Modelamento de Circuitos Integrados DigitaisCircuitos Integrados Digitais

Níveis de especificação

O que ?O que ?

Como? Como?

Exemplo

Estrutura de VHDL

Componentes de Projeto– Entidades (entities)– Arquiteturas (architectures)– Configurações (configurations) (opcional)– Bibliotecas de funções/ procedimentos

(Packages) (opcional)

Entidade

Descrição VHDL especifica:– Entity

• Fornece uma visão externa do circuito. Equivale a um símbolo no modelo esquemático.

– nome– interface

Entity 21mux isEntity 21mux isport (A : in bit;port (A : in bit; B : in bit; B : in bit; S : in bit;S : in bit; Y : out bitY : out bit ););end 21mux;end 21mux;

Introdução a VHDL

entity COMPARE isport (A,B: in bit; C: out bit);end COMPARE ;

A

BC

bitbit

bit

B

AC/8 /

8

/8+

entity SOMADOR isport (A,B: in bit_vector(7 downto 0); C: out bit_vector(7 downto 0));end SOMADOR;

Arquitetura

– Architecture •Define os componentes ou o

comportamento da entidade (entity) e suas conexões.

•Architecture está sempre conectada a uma entidade.

•A arquitetura pode conter componentes, Lógica Combinacional ou Seqüencial.

Tipos de Descrição em VHDL

Três tipos de descrição, ou arquiteturas, podem ser utilizados em VHDL

EstruturalEstrutural Comportamental Comportamental Comportamental Comportamental Data FlowData Flow Processos Processos

VHDL - Estrutural Sinais:

– interconexão entre componentes

Componentes:– devem ter sido

especificados anteriormente (hierarquia)

Uso dos componentes:– Podem ser usados mais de

uma vez *

*REUSABILIDADE de COMPONENTES

AB C

bitbit

bit

IXR2 INV

componentessinais

sinais

entity COMPARE isport (A,B: in bit; C: out bit);end COMPARE ;architecture STRUCT of COMPARE is signal I: bit; component XR2 port(x,y: in bit; z:out bit); end component; component INV port(x:in bit; z:out bit); end component;begin U0: XR2 port map(A,B,I); U1: INV port map(I,C);end STRUCT;

AB C

bitbit

bit

IU0U0 U1U1

EntidadeEntidade

ArquiteturaArquitetura

BibliotecaBibliotecade componentesde componentes(INV, XR2, AND ...)(INV, XR2, AND ...)

VHDL - Estrutural

VHDL - Comportamental(data flow)

Data flow (eq. booleanas):– concorrência

entity COMPARE is port(A,B: in bit; C : out bit);end COMPARE,architecture DFLOW of COMPARE issignal I: bit; begin I <= A XOR B; C<= NOT I;end DFLOW;

AB C

bitbit

bit

Ixorxor NOTNOT

VHDL - Comportamental (processo) Algoritmo (Processo)

– seqüencial Lista de sensibilidade

– sinais de entrada Região declarativa

– Região entre o fim da lista de sensibilidade e a palavra chave begin.

– Usada para declarar variáveis ou constantes dentro do processo.

Campo de atribuições– Campo entre a chave begin e end ALG;

entity COMPARE is port(A,B: in bit; C : out bit);end COMPARE,architecture ALG of COMPARE isbegin process (A,B) begin if (A = B) then C <= ´1´; else C <= ´0´; end if; end process;end ALG;

AB Cbit

bit

bit

Objetos em VHDL

Sinais Variables Constants

Sinais Sinais são objetos que são usados para conectar elementos concorrentes

(components, processos e atribuições concorrentes), similar aos fios uitlizados para conexão de componentes em uma protoborad, placa ou projeto esquemático.– Tipos de sinais

• escalar– signal S: bit := ´1´;

• vetor– signal S_BUS: bit_vector(0 to 7)

• Inteiro, Real, .......

– Localidade• globais

– entity• locais

– architecture

Variáveis em VHDL As variáveis são objetos usados para armazenar valores

intermediários entre indicações seqüenciais de VHDL. As variáveis são permitidas somente nos processos, procedimentos e funções, e são sempre locais àquelas funções.

As variáveis em VHDL são como variáveis em uma língua de programação convencional do software. Elas capturam e guardam imediatamente o novo valor atribuído a elas.

Constantes em VHDL Constantes são objetos que recebem um valor uma vez, quando declarado, e não

mudam seu valor durante a simulação. As constantes são úteis para criar descrições a serem lidas do projeto, e tornam mais fácil a mudança de parametros do projeto.

Declarações de Constantes podem ser feitas em qualquer área de declaração na descrição do projeto: architectura, block, process or subprogram

Exemplo

architecture sample1 of consts is constant SRAM: bit_vector(15 downto 0) := X"F0F0"; constant PORT: string := "This is a string"; constant error_flag: boolean := True;begin . . . process( . . .) constant CountLimit: integer := 205; begin . . . end process; end arch1;

Sinais - Atribuições concorrentes...

Especificam o comportamento paralelo dos módulos (hardware)

Concorrência:– atribuição de sinal – atribuição de sinal condicional/selecionada– processos– procedimentos– blocos

Atribuição de sinal concorrente

Usada em descrições estruturais e dataflow (circuitos combinacionais)

Não possuem ordem fixa de execução

A <= B + C;A <= B + C;

D < = E + FD < = E + F

++

++

BB

CCEE

FF

AA

DD

Atribuição de sinais

ExemploENTITY simpsig IS

PORT (

a, b, e : IN BIT; c, d: OUT BIT

);END simpsig;ARCHITECTURE struct OF simpsig ISBEGIN

c <= a AND B;d <= e;

END struct;

Exemplo: (arquivo simpsig.vhd)Exemplo: (arquivo simpsig.vhd)

Equivalente GráficoEquivalente Gráfico (simpsig.gdf)(simpsig.gdf)

ee dd

aabb cc

Atribuição de sinal condicional

Sintaxe:– target <= {expression when condition

else} expression Só uma expressão será atribuída

Z Z <= <= A A when when (x > 3) (x > 3) elseelse B B whenwhen (x < 3) (x < 3) elseelse CC

Não pode ser usada em processosNão pode ser usada em processos

Atribuição de sinal selecionada

Sintaxe:with expression selectwith expression select target <= {expression when choices};target <= {expression when choices};

with MYSIG select Z <= A when 15, B when 22, C when others;

Equivale ao CASEEquivale ao CASE Não pode ser usado em processosNão pode ser usado em processos

Atribuição de sinais condicionais

Exemplo de um multiplexador 2:1

ENTITY condsig ISPORT (A, B, sel : IN BIT;C : OUT BIT);

END condsig;ARCHITECTURE maxpld of condsig ISBEGIN

C <= A when sel = ‘0’ ELSE B;END maxpld;

Atribuição de sinais condicionais Exemplo (Multiplexador 4:1)

ENTITY selsig ISPORT (

do, d1, d2, d3 : IN BIT;s : IN INTEGER RANGE 0 to 3;output : OUT BIT

);END selsig;ARCHITECTURE maxpld of selsig ISBEGIN

WITH S SELECT-- cria um multiplexador

output <= d0 WHEN 0, d1 WHEN 1, d2 WHEN 2, d3 WHEN 3;

END maxpld;

d0

d1

d2

d3

s0 s1

output

Processos - Lógica Combinacional

Declarações em processos incluem um conjunto de declarações seqüenciais que atribuem valores à sinais. Estas declarações permitem a execução passo-a-passo da computação. Declarações em processos que descrevem apenas comportamento combinacional podem ser usados para criar lógica combinacional.

Para assegurar que um processo é combinacional, sua “sensitive list” deve conter todos os sinais que são lidos no processo.

“Uma sensitive list contém todos os sinais que causam as declarações do processo serem executados se seus valores mudam”.

Processo - Lógica combinacional

ENTITY proc IS -- Porta ANDPORT(a,b : IN BIT;c : OUT BIT);

END proc;ARCHITECTURE maxpld OF proc ISBEGIN

PROCESS(a, b) - - ProcessoBEGIN q <= a AND b;END PROCESS;

END maxpld;

aabb cc

Exemplo

Construtores sequenciais em VHDL

If-then-else case

Construtores seqüenciais VHDL inclui uma variedade das indicações de controle que podem ser usadas

descrever funções combinationais, indicar prioridades das operações, e especificar o outro comportamento em alto-nível.

O construtor if-then-else é a forma mais comum da indicação de controle em VHDL.

Formato da declaração case: if first_condition then statements elsif second_condition then statements else statements end if;

Processo: estrutura Algoritmo (Processo)

– seqüencial Lista de sensibilidade

– sinais de entrada Região declarativa

– Região entre o fim da lista de sensibilidade e a palavra chave begin.

– Usada para declarar variáveis ou constantes dentro do processo.

Campo de atribuições– Campo entre a chave begin e end ALG;

architecture ALG of COMPARE isbegin process (A,B) begin if (A = B) then C <= ´1´; else C <= ´0´; end if; end process;end ALG;

AB Cbit

bit

bit

Declaração Case Declarações Case são um tipo de indicação de controle que pode ser

usado como alternativas às construções de “if-then-else”. Formato da declaração case:

case control_expression is when test_expression1 => statements when test_expression2 => statements when others => statements end case;

Obs: a diferença preliminar entre as descrições escritas usando case e if-then-else é que as indicações if-then-else implicam uma prioridade implicita, enquanto que o uso do case não implica em nenhuma prioridade.

Loops em VHDL

As indicações do laço são uma catagoria de estruturas do controle que permitem que você especifique repetições seqüências do comportamento em um circuito.

Há três tipos preliminares de laços em VHDL:– for loops– while loops e – infinite loops.

Configuração

É uma lista de “componentes” que especifica qual arquitetura deve ser usada para cada entidade em um determinada projeto.

Entity A

Arch X Arch Y

Entity B

Arch X Arch Y

Entity C

Arch X Arch Y

Entity D

Arch X Arch Y

Exemplo:entity ArchA XB YC YD X

Escolhendo uma arquitetura...

Configurações– permite a seleção de

diversas arquiteturas em diferentes níveis de hierarquia.

Compare

ALUCPU

entity ALU is port( opcode:...end ALU;

architecture first of ALU is component COMPARE port (a,b:in bit; c:out : bit); end component; ...begin U0: COMPARE port map (s,d,q); ....end first

configuration fast_one of ALU isfor firstfor U0: COMPARE use entity WORK.COMPARE(dataflow);

Package

É uma unidade que agrupa várias declarações, as quais, podem ser compartilhadas entre vários projetos.

Packages são em geral armazenas em bibliotecas para maior conveniência.

Packages são usadas para declarar itens compartilhados, tais como: – Types– Subtypes– Components– Signals– Files– Aliases– Attributes e – Groups.

Package

Parte Declarativa– Declaração de constantes– Declaração de subprogramas– Declarações de tipos– Declaração de componentes

Corpo do Pacote– corpo de funções– corpo de procedimentos

Exemplo Package

Package my_defs isPackage my_defs isConstant my_value: integer := 10;Constant my_value: integer := 10;function my_not (a : boolean) return boolean;function my_not (a : boolean) return boolean;end my_defs;end my_defs;

Parte DeclarativaParte Declarativa

Package body my_defs isfunction my_not (a : boolean) return boolean isbegin return not a;end;end my_defs;

Corpo do PacoteCorpo do Pacote

Packages - MAX+PLUS II

Maxplus2.vhd maxplus2 altera Max+plus II primitivas, mega emacrofunções (VHDL)

megacore.vhd megacore altera MAX+PLUS II Megacore VHDL

sd1164.vhdstd1164b.vhd

std_logic_1164 ieee STD_LOGIC eSTD_LOGIC_VECTOR

lpm_pack.vhd lpm_components lpm Funções LPM (VHDL)

arith.vhdarithb.vhd

std_logic_arith ieee tipos SIGNED e UNSIGNED,comparações, conversões

signed.vhdsignedb.vhd

std_logic_signed ieee Funções que permite uso deSTD_LOGIC_VECTOR comotipos SIGNED

unsigned.vhdunsignedb.vhd

std_logic_unsigned ieee STD_LOGIC_VECTOR comotipos UNSIGNED

Arquivo Package Biblioteca ConteúdoArquivo Package Biblioteca Conteúdo

Resumindo...

Packages:Packages: declaração declaração de tipos, constantes ede tipos, constantes esubprogramas compar-subprogramas compar-tilhadostilhados

architectures:architectures: define defineimplementações das implementações das entidadesentidades

configurations:configurations: se- se-leciona implementaçõesleciona implementaçõesde componentesde componentes

entities:entities: define definemódulos de projeto e módulos de projeto e suas interfacessuas interfaces

Arquivos VHDLArquivos VHDLProjeto VHDLProjeto VHDL

VHDL - OperadoresTable 6.1 VHDL Operators.

VHDL Operator Operation + Addition - Subtraction * Multiplication* / Division*

MOD Modulus* REM Remainder*

& Concatenation – used to combine bits SLL** logical shift left SRL** logical shift right SLA** arithmetic shift left SRA** arithmetic shift right ROL** rotate left ROR** rotate right

= equality /= Inequality < less than

<= less that or equal > greater than

>= greater than or equal NOT logical NOT AND logical AND OR logical OR

NAND logical NAND NOR logical NOR XOR logical XOR

XNOR* logical XNOR

*Not supported in many VHDL synthesis tools. In the MAX+PLUS II tools, only multiply and divide by powers of two (shifts) are supported. Mod and Rem are not supported in MAX+PLUS II. Efficient design of multiply or divide hardware typically requires the user to specify the arithmetic algorithm and design in VHDL. ** Supported only in 1076-1993 VHDL.

Design

Compilation

Simulation Programação

Graphical Entry

HDL Entry

Compiler

Timing Diagram

Timing Analysis

Program CPLD

UP 1 Development Board

Fluxo de Projeto no Maxplus+II

VHDL

Referências– Manual VHDL da Altera– A Guide to VHDL, Stanley Mazor, Patricia

Langstrat– VHDL by Douglas, Perry– Vhdl Made Easy!

by David Pellerin, Douglas Taylor