University of Sargodha, Lahore Campus Prepared by Ali Saeed.

-

Upload

john-hardy -

Category

Documents

-

view

218 -

download

0

description

Transcript of University of Sargodha, Lahore Campus Prepared by Ali Saeed.

Computer Organization &

Assembly LanguageUniversity of Sargodha, Lahore Campus

Prepared by Ali Saeed

MASM stands for Microsoft Macro Assembler The Microsoft Macro Assembler is an x86

assembler that uses the Intel syntax for MS-DOS and Microsoft Windows

What is MASM

First Set the Environment Variable

How to use MASM

How to use MASM

Edit Command is use to enter in Assembly Editor

MASM prog1.asm to Compile Link prog1 Prog1; to run

How to use MASM

8086 was introduced in 1978 It had 16 bit processor 8088 was introduced in 1979 8088 has 8 bit data bus 8086 has faster clock rate, thus batter

performance 8088 is less expensive

8086 and 8088 Microprocessor

80186 and 80188 are enhanced versions of 8086 and 8088 respectively

These has new instruction set called extended instruction set

But, these did not had significant advantages over 8086 and 8088

Soon it was replaced by 80286

80186 and 80188 Microprocessor

It was introduced in 1982 It was also 16 bit processor It was faster then 8086 (12.5 MHz Vs

10MHz) It has two number of operation modes

◦ Real Addressing Mode◦ Protected virtual Addressing Mode

80286 Microprocessor

In Real Addressing mode this will behaves like 8086

Program for 8086 can be executed in this mode without modifications

In protected mode 80286 support multitasking, ability to execute several tasks at a time

Memory protection in protected mode memory use by one program can’t be use by others

80286 Microprocessor

It was 32 bit microprocessor 80386 or 386 was introduced in 1985 It was much faster than 80286 having 3.3

MHz Processor It has three modes

◦ Real Addressing Mode◦ Protected virtual Addressing Mode◦ Virtual 8086 mode (run multiple 8086 application

under memory protection mode) 386XS has same internal structure as 386, but

has 16 bit bus

80386 and 80386SX Microprocessor

Registers are small memory area inside the CPU.

Registers have fastest speed then other memory devices i.e. RAM, Hard Disk etc…

Registers are available of different size◦ 8 bit◦ 16 bit◦ 32 bit

What is Register

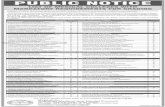

8086 Register

Organization of Registers in x86

AX - the accumulator register (divided into AH / AL). BX - the base address register (divided into BH / BL). CX - the count register (divided into CH / CL). DX - the data register (divided into DH / DL). SI - source index register. DI - destination index register. BP - base pointer. SP - stack pointer.

Registers

CS - points at the segment containing the current program.

DS - generally points at segment where variables are defined.

ES - extra segment register, it's up to a coder to define its usage.

SS - points at the segment containing the stack.

Segment Registers

Although it is possible to store any data in the segment registers

This is never a good idea. The segment registers have a very special

purpose - pointing at accessible blocks of memory.

Segment registers work together with general purpose register to access any memory value.

Segment Registers

For example if we would like to access memory at the physical address 12345h (hexadecimal), we should set the DS = 1230h and SI = 0045h.

This is good, since this way we can access much more memory than with a single register that is limited to 16 bit values.

Segment Registers

CPU makes a calculation of physical address by multiplying the segment register by 10h and adding general purpose register to it (1230h * 10h + 45h = 12345h):

Segment Registers

The address formed with 2 registers is called an effective address.

By default BX, SI and DI registers work with DS segment register;

BP and SP work with SS segment register. Other general purpose registers cannot

form an effective address! Also, although BX can form an effective

address, BH and BL cannot!

Segment Registers

SP – Stack Pointer, it is use to conjunction with SS to access the stack segment

BP – Base Pointer, it is used primarily to access data on stack, but unlike SP we can use BP to access data in other segment

SI – Source Index, it is used to point memory location in data segment address by DS. By adding SI we can easily access consecutive memory locations

DI – Destination Index, it work like SI, It work with string operations, and access memory with ES

Pointer and Index Register

All register come above is for data register. To access instructions 8086 use registers CS

and IP. CS contain the segment number of next

instruction IP contain offset of next instruction IP is updated every time as each instruction

is executed IP can not be manipulated by an instruction An instruction may not contain IP as

operand

Instruction Pointer (IP)

Thanks