UNIT IV 8051- MICROCONTROLLER - WordPress.com · UNIT IV- 8051 MICROCONTROLLER Prepared by R....

Transcript of UNIT IV 8051- MICROCONTROLLER - WordPress.com · UNIT IV- 8051 MICROCONTROLLER Prepared by R....

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 1

UNIT IV

8051- MICROCONTROLLER

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 2

Application

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 3

Pin Description of the 8051

1234567891011121314151617181920

4039383736353433323130292827262524232221

P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST

(RXD)P3.0(TXD)P3.1

(T0)P3.4(T1)P3.5

XTAL2XTAL1

GND

(INT0)P3.2(INT1)P3.3

(RD)P3.7(WR)P3.6

VccP0.0(AD0)P0.1(AD1)P0.2(AD2)P0.3(AD3)P0.4(AD4)P0.5(AD5)P0.6(AD6)P0.7(AD7)EA/VPPALE/PROG

PSENP2.7(A15)P2.6(A14)P2.5(A13)P2.4(A12)P2.3(A11)P2.2(A10)P2.1(A9)P2.0(A8)

8051

(8031)

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 4

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 5

Complex Instruction Set Computer (CISC)

• Memory in those days was expensive. Bigger programs required more storage which

included more money . There was a need to reduce the number of instructions per

program. This was achieved by having multiple operations within single instruction.

• Multiple operations lead to many different kinds of instructions. Access to memory in

turn makes the instruction length variable and fetch-decode execute time unpredictable –

making it more complex. Thus hardware was made to understand the complexity of

instruction set.

• The computer having such instruction set was named as Complex Instruction Set

Computer (CISC). Intel 8051 is an example for CISC architecture.

Difference between Harvard and Princeton or Von Neumann Architecture

• In Harvard Architecture, the CPU can have separate data and instruction memory and

busses, allowing transfers to be performed simultaneously on both busses.

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 6

• In Von Neumann architecture, the CPU can be either reading an instruction

or reading/writing data from/to the memory. Both cannot occur at the same time since

the instructions and data use the same bus system.

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 7

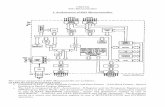

Basic 8051 Architecture

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 8

Features

Various features of 8051 microcontroller are given as follows.

• 8-bit CPU

• 16-bit Program Counter

• 8-bit Processor Status Word (PSW)

• 8-bit Stack Pointer

• Internal RAM of 128bytes

• Special Function Registers (SFRs) of 128 bytes

• 32 I/O pins arranged as four 8-bit ports (P0 - P3)

• Two 16-bit timer/counters : T0 and T1

• Two external and three internal vectored interrupts

• One full duplex serial I/O

8051 Clock and Instruction Cycle

• The heart of 8051 is the circuitry that generates the clock pulses by which all internal

operations are synchronised. Pins XTAL1 and XTAL2 are provided for connecting

resonator to form an oscillator.

• The time taken to complete any instruction is called as machine cycle or

instruction cycle. In 8051 one instruction cycle consists of 6 states or 12 clock cycles,

instruction cycle is also referred as Machine cycle.

Instruction cycle of 8051 (Instruction cycle has six states (S 1 - S 6 ). Each state has two

pulses (P1 and P2))

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 9

128 bytes of Internal RAM Structure

The lower 32 bytes are divided into 4 separate banks. Each register bank has 8 registers of one

byte each. A register bank is selected depending upon two bank select bits in the PSW register.

(RS1,RS0 bits of PSW)

Next 16bytes are bit addressable. In total, 128bits (16X8) are available in bit addressable area.

Each bit can be accessed and modified by suitable instructions.

• A bit variable can be set with a command such as SETB and cleared with a command

such as CLR.

Example instructions are:

• SETB 25h ; sets the bit 25h (becomes 1)

• CLR 25h ; clears bit 25h (becomes 0)

The bit addresses are from 00H (LSB of the first byte in 20H) to 7FH (MSB of the last byte in

2FH). Remaining 80bytes of RAM are available for general purpose. The general purpose RAM

can be accessed using direct or indirect addressing modes.

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 10

Internal Data Memory and Special Function Register (SFR) Map

The special function registers (SFRs) are mapped in the upper 128 bytes of internal data memory

address. Hence there is an address overlap between the upper 128 bytes of data RAM and SFRs.

Note that the upper 128 bytes of data RAM are present only in the 8052 family. The lower128

bytes of RAM (00H - 7FH) can be accessed both by direct or indirect addressing while the upper

128 bytes of RAM (80H - FFH) are accessed by indirect addressing.

The SFRs (80H - FFH) are accessed by direct addressing only. This feature distinguishes the

upper 128 bytes of memory from the SFRs, as shown in figure.

The set of Special Function Registers (SFRs) contains important registers such as Accumulator,

Register B, I/O Port latch registers, Stack pointer, Data Pointer, Processor Status Word (PSW)

and various control registers.

Processor Status Word (PSW)

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 11

Accumulator is an 8 bit register widely used for all arithmetic and logical operations.

Accumulator is also used to transfer data between external memory. B register is used along

with Accumulator for multiplication and division. A and B registers together is also called

MATH registers.

Stack Pointer (SP) – it contains the address of the data item on the top of the stack. Stack may

reside anywhere on the internal RAM. On reset, SP is initialized to 07 so that the default stack

will start from address 08 onwards.

Data Pointer (DPTR) – DPH (Data pointer higher byte), DPL (Data pointer lower byte). This is

a 16 bit register which is used to furnish address information for internal and external program

memory and for external data memory.

Program Counter (PC) – 16 bit PC contains the address of next instruction to be executed. On

reset PC will set to 0000. After fetching every instruction PC will increment by one.

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 12

Special Function Register

1. Timer

Timers/Counters are used generally for

• Time reference

• Creating delay

• Wave form properties measurement

• Periodic interrupt generation

• Waveform generation

• The two timers in 8051 share two SFRs (TMOD and TCON) which control the timers,

and each timer also has two SFRs dedicated solely to itself (TH0/TL0 and TH1/TL1).

• 8051 has two 16-bit programmable UP timers/counters. They can be configured to

operate either as timers or as event counters

• In the "timer" function mode, the counter is incremented in every machine cycle.

• In the "counter" function mode, the register is incremented in response to a 1 to 0

transition at its corresponding external input pin (T0 or T1). It requires 2 machine cycles

to detect a high to low transition.

1.1. Timer Mode control (TMOD) Special Function Register

TMOD register is not bit addressable.

Gate: Based on the status of the signal. Timer starts counting using either internal clock (timer

mode) or external pulses (counter mode).

C/T*: It is used for the selection of Counter/Timer mode.

Mode Select Bits.

M1 and M0 are mode select bits.

1.2. Timer control (TCON) Special function register:

TCON is bit addressable. The address of TCON is 88H. It is partly related to Timer and partly to

interrupt.

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 13

2. Interrupt

8051 has five interrupts. They are maskable and vectored interrupts. Out of these five, two are

external interrupt and three are internal interrupts.

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 14

8051 makes use of two registers to deal with interrupts.

2.1. IE Register - Interrupt Enable register

• This is an 8 bit register used for enabling or disabling the interrupts. The structure of IE is

2.2. IP Register.

This is an 8 bit register used for setting the priority of the interrupts.

3. Serial Interface

3.1. SBUF

The serial port of 8051 is full duplex, i.e., it can transmit and receive simultaneously.

UNIT IV- 8051 MICROCONTROLLER

Prepared by R. Kavitha Page 15

The register SBUF is used to hold the data. The special function register SBUF is physically two

registers. One is, write-only and is used to hold data to be transmitted out of the 8051 via TXD.

The other is, read-only and holds the received data from external sources via RXD.

3.2.Serial Port Control Register (SCON)

Register SCON controls serial data communication.

Address: 098H (Bit addressable)

Mode select bits

SM2:multi processor communication bit

REN: Receive enable bit

TB8: Transmitted bit 8 (Normally we have 0-7 bits transmitted/received)

RB8: Received bit 8

TI: Transmit interrupt flag

RI: Receive interrupt flag

3. Power Mode control Register

Register PCON controls processor power down, sleep modes and serial data band rate. Only

one bit of PCON is used with respect to serial communication. The seventh bit (b7)(SMOD) is

used to generate the baud rate of serial communication.

SMOD: Serial baud rate modify bit

GF1: General purpose user flag bit 1

GF0: General purpose user flag bit 0

PD: Power down bit

IDL: Idle mode bit