TSMC 40ULP/LP EFLX™-100 CORE PRODUCT BRIEF 40ULP/LP EFLX™-100 CORE PRODUCT BRIEF ... DDH and V...

Transcript of TSMC 40ULP/LP EFLX™-100 CORE PRODUCT BRIEF 40ULP/LP EFLX™-100 CORE PRODUCT BRIEF ... DDH and V...

TSMC40ULP/LPEFLX™-100COREPRODUCTBRIEF

December2016.Copyright2014-2016FlexLogix™Technologies,Inc.

The EFLX™-100 is an embedded FPGA IP core, for implementing reconfigurable logic,containing120Look-Up-Tables (LUTs:each isadual4-input LUTwith2 independentoutputsand 2 bypassable flip flops) in Reconfigurable Building Blocks (RBBs), patented interconnectnetwork,multipleclocks&scan:reconfigurableatanytime.Targetspecs:

EFLX™-100LogicCore

EFLX™-100DSPCore

TheEFLX-100coreisavailablein4differentVTconfigurationsand2nominalvoltages:eachoptimizedfordifferentperformance-to-powerrequirementsfordifferenttargetapplications.

TargetspecsforEFLX-100basedonGDSforTSMC40ULP:

ConfigurationBitCellandStaticLogic:selectaVT

RBBandDSPlogic:selectaVT

16-bitCounterMHz

TT,85C

DeepSleepModeLeakageμW

CoreSleepModeLeakageμW

0.9V 1.1V TT,85C,0.9V

eHVT eHVT 110 190 0.5 1.5eHVT SVT 180 270 0.5 1.5HVT HVT 110 190 1.5 4.5HVT SVT 180 270 1.5 4.5InquireforEFLX-100TSMC40LPspecs:GDSiscompatible

Name EFLX™-100Core

Technology TSMC40nmULP/LPCMOS

MetalUtilization 5metallayers

NominalSupplyVoltage(V) 0.9V&1.1V

JunctionTemperature(°C) −40to125LeakagePower(μW)forEFLX-100corewitheHVTBitCell

DeepSleepMode0.5μWSleepMode1.5μW(at85°C,0.9V,TT)

16-bitCounterFrequency(MHz) 110–270MHzdependingonVT/Vddchosen(TT,85C,0.9or1.1V)

Area(mm2) 0.13

ClockInputs 1to8

DataI/O(optionalflops) 152inputsand152outputs

LogicCore DSPCoreDual4-inputLUTswith2independentoutputs 120 88

Totalflipflops(exDSP) 544 480

DSPMACs 0 2

EFLXArraySize 1×1to5x5

Design-for-TestSupport Yes

LUTUtilization >90%

AXI/JTAGsoftIP Yes,ifrequested

TSMC40LPCompatibility Yes(inquirefor40LPspecs)

RBBDSP

RBBLogic

RBBLogic

IO

IO

IO IO

RBBLogic

RBBLogic

RBBLogic

IO

IO

IO

IO

TSMC40ULP/LPEFLX™-100Core ProductBrief|December2016 www.flex-logix.compage2

December2016.Copyright2014-2016FlexLogix™Technologies,Inc.EFLXandFlexLogixaretrademarksofFlexLogix™Technologies,Inc.

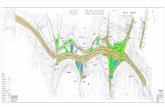

The EFLX-100 Core comprises of three major blocks: thereconfigurable building blocks (RBBs) of Logic/DSP types, theinterconnectnetwork,andtheuserI/Os.EFLXfeaturesfullconnectivityinside thecore,andprovidesadditional interconnectsat theboundarytoconcatenatemultiplecoresviatheexpandablenetworkI/Os.

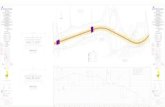

TheEFLX-100userI/Oconfigurationisshownbelowleft.TheEFLX-100controlpinsareshowbelowright.

Eachcorehasaninternalpowergrid(VDDHandVSS)whichcanbeconnectedtothecustomer’sdigitalSoCpowergrid.Thecorehaspowercontrolpinsforpower-onandpowergating.ThecoreincludesconfigurationbitswhichareconfigurableviaAXI,JTAGorourcustomserialinterface.Oneachsideofthecore,thereare2inputclocksand2outputclockswhichconcatenateinEFLXarrays.

TheEFLXcoreisavailablenow.Validationinsiliconisinprocessforall10EFLXcorevariationsinTSMC40ULP.InformationisavailableunderNDAtodoextensiveevaluationandchiparchitecturetradeoffs.Contactinfo@flex-logix.com.

EFLX-100

UserClock

UserClock

UserClock

5

Config.(Au

x.)

3

DFT(Au

x.)

PowerCtrl

22

Config.

DFT

2Po

werCtrl

2

UserClock

6Config.

PowerCtrl

DFT3

EFLX-100~438

µmactual= 1output

&1inputs

UserI/Os:60inputpins+60outputpins

UserI/Os:16inpu

tpins+

16outputpins

UserI/Os:60inputpins+60outputpins

= 1outputs&1inputsUs

erI/Os:16inpu

tpins+

16outputpins ~298umactual

DeliverablesandEDADesignViewsFront-endDesignview(withNDA) Back-endDesignViews(withLicense)

EncryptedVerilogModel VerilogModelLIB GDS-IILEF CDL/Spicenetlist

Detaileddatasheet&DSPUser’sGuide IntegrationguidelinesSiliconevaluationreport Integrationassistanceasneeded

EFLXCompilerevaluationversion EFLXCompilerbitstreamgenerationversion Testvectors

RBBRBB

IOB

煑

煑IOB

Interconnects

Expa

ndableNetworkI/Os

UserI/Os

EFLXFPGACore

UserI/Os