TLCS-900/L Series › media › datasheet › Toshiba › TMP93PW...8 BIT AD Converter (10CH) HS...

Transcript of TLCS-900/L Series › media › datasheet › Toshiba › TMP93PW...8 BIT AD Converter (10CH) HS...

TOSHIBA Original CMOS 16-Bit Microcontroller

TLCS-900/L Series

TMP93PW76

Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, “Points of Note and Restrictions”.

Especially, take care below cautions. **CAUTION**

How to release the HALT mode Usually, interrupts can release all halts status. However, the interrupts (INT0,

INT1), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of fc or fs) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

TMP93PW76

2003-03-31 93PW76-1

CMOS 16-Bit Microcontroller

TMP93PW76F

1. Outline and Feature

The TMP93PW76F is a system evaluation LSI having a built in One-Time PROM (128 Kbytes) for TMP93CW76/CU76/CT76F.

A programming and verification for the internal PROM is achieved by using a general EPROM programmer with an adapter socket.

The function of this device is exactly same as the TMP93CW76/CU76/CT76F by programming to the internal PROM and the TMP93PW76F is used as the evaluation chip of TMP93CW76/CU76/CT76F.

Product no. ROM RAM Package Adapter

Socket no.

TMP93PW76F OTP 128 Kbytes 2.5 Kbytes P-QFP100-1420-0.65A BM11146A

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Qualityand Reliability Assurance/Handling Precautions. TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in generalcan malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer,when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoidsituations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage toproperty. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the mostrecent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the “Handling Guide forSemiconductor Devices,” or “TOSHIBA Semiconductor Reliability Handbook” etc.. The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personalequipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products areneither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction orfailure of which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended Usage include atomic energy controlinstruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments,medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be madeat the customer’s own risk. The products described in this document are subject to the foreign exchange and foreign trade laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed byTOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from itsuse. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION orothers. The information contained herein is subject to change without notice.

000707EBP1

Purchase of TOSHIBA I2C components conveys a license under the Philips I2C Patent Rights to use these components in an I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips.

TMP93PW76

2003-03-31 93PW76-2

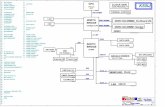

Figure 1.1 TMP93PW76F block diagram

P51/INT3/TI2 (TI4)

P87/COMP IN

P52/INT2/TI1(TI0)

PD0 to 1/G8 to 9PC0 to 7/G0 to 7

PC0 to 5/S8 to 13

PE0 to 7/S0 to 7

P86/CSYNCIN

DVCC DGND

to SIO

XWXBXDXHXIXIXI

XS

SR F

900/L CPU

P C

High frequency OSC

(16 MHz)

8-Bit Timer (TC0)

Capture (Capture 0, 1, 2)

VS

RMTU, RMTD

EXT

V-Separation

CFGTM CTL, CFG, DFG, DPG

PCTL

8 BIT AD

Converter

(10CH)

HS

Capture Input

(CAPIN)

INT2, 3, 4 Others INT

X1

X2

PB0/XT1

PB1/XT2

TEST

CLK CPU INT

RESET P54/INT0

P53/INT1

ADREF P40 to 47/AIN2 to 9 P75, 76/AIN0, 1 AGND

P82/RMTIN

P83/EXT/TO

P84/DPGIN

P85/CFGIN

P81/DFGIN

P80/CTLIN

TEST1

TEST2

TEST3 (NC)

for P75 (AIN0) P76 (AIN1)

PA0/PWM3/ PVPH

for P50 (SI)

to AD

P50/INT4/TI3(TI5)/SI

P91/TPG01/ VASWP

P73/SDA0

P74/SCL0 P75/AIN0/SDA1 P76/AIN1/SCL1

PWM0

PWM1

PA3/PWM2

P93/TPG03

P97/TPG11

P90/TP0/TPG00

P92/TP1

P94/CR P94/HA

P51/SO

P52/SCK

Vkk

(VFT Driver)

W

IX

B

D

H

IY

IZ

SP

P20 to 27 P10 to17

P00 to 07

C-sync In

P96/TO1/TPG10

to PWM3

RMT-Input

External-Input

Low frequency OSC

(32 MHz)

PV/PH

for 8-BIT PWM

VISS/VASS CTL Duty Detector

Watchdog Timer (WDT)

Time Base Timer (TBC)

ROM

(128 KB)

RAM

(2.5 KB) Port 2

Port 1

Port 0

Interrupt Controller

Real Time Counter (RTC)

Port D

Port C

Port F

Port E

8-BIT PWM (1CH)

14-BIT PWM (3CH)

SIO

I2C bus I/F

(IIC)

8-Bit Timer (TC1)

8-Bit Timer (TC2)

8-Bit Timer (TC3)

8-Bit Timer (TC4)

8-Bit Timer (TC5)

Timing Pulse Generater

(TPG)

Head Amp SW Color Rotary

(HA/CR)

32 bits

A

C

E

L

TMP93PW76

2003-03-31 93PW76-3

2. Pin Assignment and Functions

The assignment of input and output pins for the TMP93PW76F, their names and functions are described below.

2.1 Pin Assignment

Figure 2.1.1 shows pin assignment of the TMP93PW76F.

Figure 2.1.1 Pin assignment (100-pin QFP)

P23

P24

P25

P26

P27

PE0/S0

PE1/S1 PE2/S2

PE3/S3

PE4/S4

PE5/S5

PE6/S6

PE7/S7

PF0/S8

PF1/S9

PF2/S10

PF3/S11

PF4/S12

PF5/S13

PC0/G0

PC1/G1

PC2/G2

PC3/G3

PC4/G4

PC5/G5

PC6/G6

PC7/G7

PD0/G8

PD1/G9

VKK

TEST2

TEST1

PB1/XT2

PB0/XT1

/RESET

/TEST

X2

X1

DGND

CLK

P54/INT0

P53/INT1

P52/INT2/TI1/TI0/SCK

P51/INT3/TI2/TI4/SO

P50/INT4/TI3/TI5/SI

ADREF

ADGND

P47/AIN9

P46/AIN8

P45/AIN7

P44/AIN6

P43/AIN5

P42/AIN4

P41/AIN3

P40/AIN2

P76/AIN1/SCL1

P75/AIN0/SDA1

P74/SCL0

P73/SDA0

P87/COMPIN

P22

P21

P20

P17

P16

P15

P14

P13

P12

P11

P10

P07

P06

P05

P04

P03

P02

P01

P00

TE

ST

3

DV

CC

PA

0/P

WM

3/P

VP

H

PA

3/P

WM

2

PW

M0

PW

M1

P90

/TP

0/T

PG

00

P91

/TP

G01

/VA

SW

P

P92

/TP

1

P93

/TP

G03

P94

/CR

P95

/HA

P96

/TO

1/T

PG

10

P97

/TP

G11

P80

/CT

LIN

P81

/DF

GIN

P82

/RM

TIN

P83

/EX

T/T

O1

P84

/DP

GIN

P85

/CF

GIN

P86

/CS

YN

CIN

1 95

90

85

80 100

5 75

15

65

20

60

25 55

30 35

40

45

50

70

10

TMP93PW76

2003-03-31 93PW76-4

2.2 Pin Names and Functions

The names of input/output pins and their functions are described below. (1) MCU mode

Table 2.2.1 Pin names and function (1/3)

Pin name Number of pins

I/O Functions

P00 to P07 8 I/O port0: I/O ports

P10 to P17 8 I/O port1: I/O ports

P20 to P27 8 I/O port2: I/O ports

P40 to P47

AIN2 to AIN9

8 Input

Input

port4: Input ports

Analog input: Input to AD converter

P50

INT4

TI3

TI5

SI

1 I/O

Input

Input

Input

Input

Port50: I/O port (schmitt input)

External Interrupt request input 4: Rising edge/Falling edge programable

16-bit timer3 (TC3) Input 3

16-bit timer5 (TC5) input 5

SIO received data

P51

INT3

TI2

TI4

SO

1 I/O

Input

Input

Input

Output

Port51: I/O port (schmitt input)

External Interrupt request input 3: Rising edge/Falling edge programable

16-bit timer2 (TC2): Input 2

16-bit timer4 (TC4): input 4

SIO sending data

P52

INT2

TI1

TI0

SCK

1 I/O

Input

Input

Input

I/O

Port52: I/O port (schmitt input)

External Interrupt request input 2: Rising edge/Falling edge programable

16-bit timer1 (TC1) Input 1

8-bit Timer0 (TC0) Input 0

SIO clock line

P53

INT1

1 I/O

Input

Port53: I/O port (schmitt input)

External Interrupt request pin1: Rising edge/Level programable

P54

INT0

1 I/O

Input

Port54: I/O port (schmitt input)

External Interrupt request pin0: Rising edge/Falling edge programable

P73

SDA0

1 I/O

I/O

Port73: I/O port (schmitt input, Push-pull or open-drain output selectables)

I2C bus SDA0 line

P74

SCL0

1 I/O

I/O

Port74: I/O port (schmitt input, Push-pull or open-drain output selectable)

I2C bus SCL0 line

P75

SDA1

AIN0

1 I/O

I/O

Input

Port75: I/O port (schmitt input, Push-pull or open-drain output selectable)

I2C bus SDA1 line

Analog input 0: Analog input signal for AD converter

P76

SCL1

AIN1

1 I/O

I/O

Input

Port76: Input port (schmitt input, Push-pull or open-drain output selectable)

I2C bus SCL1 line

Analog input 1: Analog input signal for AD converter

P80

CTLIN

1 I/O

Input

Port80: I/O port (schmitt input)

CTL Capture input (Capture 0)

P81

DFGIN

1 I/O

Input

Port81: I/O port (schmitt input)

DFG Capture input (Capture 1)

TMP93PW76

2003-03-31 93PW76-5

Table 2.2.1 Pin names and function (2/3)

Pin name Number

of pins I/O Functions

P82

RMTIN

1 I/O

Input

Port82: I/O port (schmitt input)

Remote Control Signal Capture input

P83

EXT

TO1

1 I/O

Input

Output

Port83: I/O port (schmitt input)

External Capture input (Capture 0)

Timer Out 1

P84

DPGIN

1 I/O

Input

Port84: I/O port (schmitt input)

DPG Capture input (Capture 0)

P85

CFGIN

1 I/O

Input

Port85: I/O port (schmitt input)

CFG Capture input (Capture 2)

P86

CSYNCIN

1 I/O

Input

Port86: I/O port (schmitt input)

C.sync Capture input

P87

COMPIN

1 I/O

Input

Port87: I/O port (schmitt input)

Envelope Comparate Input(to HA/CR)

P90

TP0

TPG00

1 I/O

Output

Output

Port90: I/O port (Push-pull or open-drain output selectable)

Timing Pulse output 0

TPG00: TPG0 output

P91

VASWP

TPG01

1 I/O

Output

Output

Port91: I/O port (Push-pull or open-drain output selectable)

Video/Audio head switching control signal output

TPG01: TPG0 output

P92

TP1

1 I/O

Output

Port92: I/O port (Push-pull or open-drain output selectable)

Timing Pulse output 1

P93

TPG03

1 I/O

Output

Port93: I/O port (Push-pull or open-drain output selectable)

TPG03: TPG0 output

P94

CR

1 I/O

Output

Port94: I/O port (Push-pull or open-drain output selectable)

Color Rotary Output

P95

HA

1 I/O

Output

Port95: I/O port (Push-pull or open-drain output selectable)

Head Amp Switching Control Output

P96

TO1

TPG10

1 I/O

Output

Output

Port96: I/O port (Push-pull or open-drain output selectable)

Timer Out 1

TPG10: TPG1 output

P97

TPG11

1 I/O

Output

Port97: I/O port (Push-pull or open-drain output selectable)

TPG11: TPG1 output

PA0

PVPH

PWM3

1 I/O

Output

Output

PortA0: I/O port

PVPH 3-state Output

PWM(8 bits) output 3

PA3

PWM2

1 I/O

Output

PortA3: I/O port(Push-pull or open-drain output selectable)

PWM(14 bits) output 2

TMP93PW76

2003-03-31 93PW76-6

Table 2.2.1 Pin names and function (3/3)

Pin name Number

of pins I/O Functions

PWM0 1 Output PWM(14 bits) output 0 (Push-pull or open-drain output selectable)

PWM1 1 Output PWM(14 bits) output 1 (Push-pull or open-drain output selectable)

PB0

XT1

1 I/O

Input

PortB0: I/O port (Open-drain Output)

Low Frequency Oscillator connecting pin

PB1

XT2

1 I/O

Output

PortB1: I/O port (Open-drain Output)

Low Frequency Oscillator connecting pin

PC0 to PC7

G0 to G7

8 Output

Output

PortC: Output (High break down voltage outputs with pull-down resistor)

Grid Drivers

PD0,1

G8, 9

2 Output

Output

PortD: Output (High break down voltage outputs with pull-down resistor)

Grid Driver

PE0 to PE7

S0 to S7

8 I/O

Output

PortE: I/O ports (High break down voltage outputs with pull-down resistor)

Segment Driver

PF0 to PF5

S8 to S13

6 I/O

Output

PortF: I/O ports (High break down voltage outputs with pull-down resistor)

Segment Driver

TEST1 1 Output

TEST2 1 Input TEST1 should be connected with TEST2 pin.

TEST3 1 Output TEST3 (NC) should be open connection.

CLK 1 Output Clock output: Output (System Clock 2) clock.

Pulled-up during reset.

Can be set to output disable for reducing noise. (Initial Disable) TEST 1 Input Test pin: Always set to “Vcc” level RESET 1 Input Reset: Initializes LSI. (with pull-up resistor)

X1 1 Input High Frequency Oscillator connecting pins (16 MHz)

X2 1 Output High Frequency Oscillator connecting pins (16 MHz)

VKK 1 VFT Driver power supply pin

DVCC 1 Power supply pin

DGND 1 GND pin (0 V)

ADREF 1 Reference voltage input for AD converter

ADGND 1 GND pin for AD converter

TMP93PW76

2003-03-31 93PW76-7

(2) PROM mode Table 2.2.2 shows pin function of the TMP93PW76F in PROM mode.

Table 2.2.2 Pin name and function of PROM mode

Pin Function Number of

Pins I/O Function

Pin Name (MCU mode)

A7 to A0 8 Input P27 to P20

A15 to A8 8 Input P17 to P10

A16 1 Input

PROM address input

PA0

D7 to D0 8 I/O PROM data input/output P07 to P00 CE 1 Input Chip enable P93 OE 1 Input Output control P91 PGM 1 Input Program control P92

VPP 1 Power supply 12.75 V/5 V (Program power supply voltage) TEST

VCC 1 Power supply 6.25 V/5 V VCC

VSS 2 Power supply 0 V DGNG, ADGND

Pin Function Number of

Pins I/O Treatment of Pin

P90 1 Input Fix to low level (security pin) RESET 1 Input

CLK 1 Input Fix to low level (PROM mode)

TEST3 1 Output Open

X1 1 Input

X2 1 Output Self oscillation with resonator

P76, P75,

P97 to P94 6 I/O Fix to high level

TEST1/TEST2 2 Output/Input Short

P47 to P40

P54 to P50

P74, P73

P87 to P80

PA3

PB1, PB0

PC7 to PC0

PD1, PD0

PE7 to PE0

PF5 to PF0

PWM0

PWM1

ADREF

VKK

54 I/O Open

TMP93PW76

2003-03-31 93PW76-8

3. Operation This section describes the functions and basic operational blocks of the TMP93PW76F. The TMP93PW76F has PROM in place of the mask ROM which is included in the TMP93CW76.

The other configuration and functions are the same as the TMP93CW76/CU76/CT76F. Regarding the function of the TMP93PW76F (not described), see the part of TMP93CW76/CU76/CT76F.

The TMP93PW76F has two operational modes : MCU mode and PROM mode.

3.1 MCU Mode

(1) Mode-setting and function The MCU mode is set by opening the CLK pin (pin open). In the MCU mode, the

operation is same as TMP93CW76/CU76/CT76F. (2) Memory-map

The memory map of TMP93PW76F is same as that of TMP93CW76F. Figure 3.1.1 shows the memory map in MCU mode. Figure 3.1.2 show that in PROM mode.

Figure 3.1.1 Memory map in MCU mode Figure 3.1.2 Memory map in PROM mode

ROM areas of TMP93CW76/CU76/CT76F are shown in Table 3.1.1. When TMP93PW76F is used as the evaluation-chip for TMP93CU76, the programmable area located address 00000H to 07FFFH should be full of data FFH. When TMP93PW76F is used as the evaluation-chip for TMP93CT76, the programmable area located address 00000H to 0DFFFH should be full of data FFH.

Table 3.1.1 Memory of TMP93CW76/CU76/CT76

ROM Area Product No. MCU Mode PROM Mode

TMP93CW76 FE0000H to FFFFFFH 00000H to 1FFFFH

TMP93CU76 FE8000H to FFFFFFH 08000H to 1FFFFH

TMP93CT76 FEE000H to FFFFFFH 0E000H to 1FFFFH

Internal I/O (144 bytes)

Internal RAM (2.5 Kbytes)

Internal PROM (128 Kbytes-256 bytes)

Interrupt vector table area (256 bytes)

000000H

000090H

000A90H

FE0000H

FFFF00H

FFFFFFH

Internal PROM (128 Kbytes)

000000H

1FFFFH

( I Internal area)

TMP93PW76

2003-03-31 93PW76-9

3.2 PROM Mode

(1) Mode setting and Function PROM mode is set by setting the RESET and CLK pins to the “L” level. The

programming and verification for the internal PROM is achieved by using a general EPROM programmer with the adapter socket.

a. Preparation of OTP adapter BM11146A: for TMP93PW76F

b. Setting of OTP adapter The switch1 (SW1) is set to N side and the switch2 (SW2) is set to PW76 side.

c. Setting of PROM writer i) Set PROM type to TC 571000D.

Size: 1 Mbyte (128 K 8 bits) VPP: 12.75 V tPW: 100 s Electric Signature mode: none

ii) Data transmission In TMP93PW76F, PROM is placed on addresses 00000 to 1FFFFH in PROM

mode, and addresses FE0000H to FFFFFFH in MCU mode. Therefore data should be transferred to addresses 00000 to 1FFFFH in PROM mode using the object converter (tuconv) or the block transfer mode (see instruction manual of PROM programmer.)

iii) Setting of the program address Start address: 00000H End address: 1FFFFH

d. Programming Program and verify according to operating process of PROM programmer. Figure 3.2.1 shows the setting of the pins in PROM mode.

TMP93PW76

2003-03-31 93PW76-10

Figure 3.2.1 PROM mode pin setting

(2) Caution for Electric Signature

The TMP93PW76F dose not support the electric signature mode (hereinafter referred to as “signature”). If PROM programmer used the signature, the device would be damaged because of applying voltage of 12 0.5 V to pin 9 (A9) of the address.

Please use without setting the signature. (3) Program Mode

All bits of the TMP93PW76F are 1 when delivered (the erase state). Data 0 is written in the necessary bit location during program operating.

Writing function can be operated at VPP 12.75 V, OE VIH, CE VIL, PGM VIL. Built-in one time PROM can be written in any sequence. It is possible to write only special address.

(4) Adopter Socket (BM11146A: for TMP93PW76F) BM11146A is the adapter sockets to write data into the TMP93PW76F. The

TMP93PW76F has built-in one time PROM using a general EPROM programmer. (5) Program Storing Area of PROM Mode

The TMP93PW76F has the program space (FE0000H to FFFFFFH) of 128 Kbytes. The address 00000H to 1FFFFH of PROM mode equals to the address FE0000H to FFFFFFH of MCU mode.

(6) Program Write Setting Method Using a general EPROM programmer PROM to be prepared should equal to TC571000D functions. a. Set the switch (SW1) of BM11146A (hereinafter referred to as “adapter”) to the

program side (N). And the switch2 (SW2) to PW76 side. (Note 1) b. Connect MCU to the adapter. (Note 2) c. Connect the adapter to PROM programmer. (Note 2)

P07

to

P00

P97 to P94,

P76, P75

P90

VPP (12.75 V/5 V)

CLK

VCC

VCC

VCC

D7

to

D0

A16

to

A0

X1

X2

PA0

P17

to

P10

P27

to

P20

DGND

Use the 10 MHz resonator in case of programming and verification by a general PROM programmer.

ADGND SECURITY

TEST1

For other pins, refer to the section on pinfunctions (Table 2.2.2).

TEST

P91

P93

P92

RESET

OE

CE

PGM

TEST2

TMP93PW76

2003-03-31 93PW76-11

d. Set the PROM type of PROM programmer to TC571000D. e. Set the start address for writing PROM to 00000H, and the end address to 1FFFFH.

(Note 3) f. Writing to built-in one time PROM and verifying should be operated according to the

operation procedures of PROM programmer.

Note 1: If data is written to built-in one time PROM without setting the switch1 (SW1) to the program side and switch2 (SW2) to PW76 side, the device would be damaged.

Note 2: Please set with the first pin of the adapter and that of PROM programmer socket matched. If the first pin is conversely set, MCU or programmer would be damaged.

Note 3: If data “0” is written to the address which is over 1FFFFH, the contents of the original program would be damaged because of writing 0 to the addresses 00000H to 1FFFFH.

(7) Programming Flow Chart

The programming mode is set by applying 12.75 V (programming voltage) to the VPP pin when the following pins are set as follows, (VCC: 6.25 V, RESET : “L” level, CLK: “L” level).

While address and data are fixed and CE pin is set to “L” level, 0.1 ms of “L” level pulse is applied to PGM pin to program the data.

Then the data in the address is verified. If the programmed data is incorrect, another 0.1 ms pulse is applied to PGM pin. This programming procedure is repeated until correct data is read from the address. (25

times maximum) Subsequently, all data are programmed in all addresses. The verification for all data is done under the condition of Vpp Vcc 5 V after all data

were written. Figure 3.2.2 shows the programming flow chart.

TMP93PW76

2003-03-31 93PW76-12

Figure 3.2.2 Flow chart

Start

Vcc 6.25 V 0.25 V Vpp 12.75 V 0.25 V

Address Start Address

X 0

Program 0.1 ms Pluse

X>25?

Read All Data

Pass Fall

Address Address 1

Verify

X X 1

Vcc 5 V Vpp 5 V

Last Address? No

Error

Yes

Error

OK

Yes

OK

No

TMP93PW76

2003-03-31 93PW76-13

(3) Security Bit The TMP93PW76F has a Security Bit in PROM cell. If the Security Bit is programmed to 0, the content of the PROM is disable to be read

(FFH data) in PROM mode.

(How to program the Security Bit.)

The difference from the programming procedures described in section 3.2 (1) are follows. a. Setting OTP adapter

Set the switch1 (SW1) to S side and the switch2 (SW2) is set to PW76 side. b. Setting PROM programmer

i) Transferring the data ii) Setting of programming address

The security bit is in bit 0 of address 00000H. Set the start address 00000H and the end address 00000H. Set the data FEH at the address 00000H.

TMP93PW76

2003-03-31 93PW76-14

4. Electrical Characteristics

4.1 Absolute Maximum Rating

Parameter Symbol Rating Unit

Power Supply Voltage Vcc 0.5 to 6.5

Input Voltage VIN 0.5 to Vcc 0.5

Output Voltage (except PC, PD, PE, PF) VOUT1 0.5 to Vcc 0.5

Output Voltage (PC, PD, PE, PF) VOUT2 Vcc 40

V

Output Current (except PC, PD, PE, PF) (per 1 pin) IOH1 3.2

Output Current (PC, PD) (per 1 pin) IOH2 25

Output Current (PE, PF) (per 1 pin) IOH3 15

Output Current (per 1 pin) IOL 3.2

Output Current (total except PC, PD, PE, PF) IOH1 40

Output Current (total of PC, PD, PE, PF) IOH2 120

Output Current (total) IOL 120

mA

Power Dissipation (Ta 70°C) PD 600 mW

Soldering Temperature Tsolder 260

Storage Temperature Tstg 65 to 150

Operating Temperrature Topr 20 to 70

°C

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

TMP93PW76

2003-03-31 93PW76-15

4.2 DC Characteristics

Ta 20 to 70°C

Parameter Symbol Condition Min Typ. Max Unit

fc 4 to 16 MHz 4.5 Power Supply Voltage Vcc

fs 30 to 34 kHz 2.7 5.5 V

P0, P1, P2, P4, P9,

PA, PB, PE, PF VIL1 (CMOS) 0.3 Vcc

RESET , P5, P7, P8 VIL2 (Schmitt) 0.25 Vcc

TEST VIL3 (Fixed) 0.3

Input

Low

Voltage

X1 VIL4 (Xtal)

0.3

0.2 Vcc

P0, P1, P2, P4, P9,

PA, PB, PE, PF VIL1 (CMOS) 0.7 Vcc

RESET , P5, P7, P8 VIH2

(Schmitt) 0.75 Vcc

TEST VIH3 (Fixed) Vcc 0.3

Input

High

Voltage

X1 VIH4 (Xtal)

Vcc 2.7 to 5.5 V

0.8 Vcc

Vcc 0.3

Output Low Voltage VOL IOL 1.6 mA

(Vcc 2.7 to 5.5 V)

0.45 V

VOH IOH 400 µA

(Vcc 2.7 to 5.5 V) 2.4

Output High Voltage

VOH1 IOH 700 µA

(Vcc 4.5 to 5.5 V) 4.1

V

PE, PF 5

PC, PD IOH

Vcc 4.5 V

VOH 2.4 V 15 mA

Input Leakage Current ILI 0.0 Vin Vcc 0.02 ±5

Output Leakage Current ILO 0.2 Vin Vcc-0.2 0.05 ±10 µA

Power Down

Voltage VSTOP

VIL2 0.2 Vcc,

VIH2 0.8 Vcc 2.0 6.0 V

Vcc 5 V ± 10% 50 150 RESET

Pull Up Resistor RRST

Vcc 3 V ± 10% 80 200 k

Pin Capacitance CIO osc 1 MHz/100 mVp-p 10 pF

Schmitt Width RESET ,

P5, P7, P8 VTH 1.0 V

NORMAL 30 50

RUN 18 28

IDLE2 15 25

IDLE1

Vcc 5 V ± 10%

fc 16 MHz

5 8

mA

SLOW 50 80

RUN 30 45

IDLE2 25 40

IDLE1

Vcc 3 V ± 10%

fs 32.768 kHz

(typ: VCC 3.0 V) 6 15

µA

STOP

Icc

Vcc 2.7 to 5.5 V 0.2 10

Note 1: Typical value are for Ta 25°C and Vcc 5 V unless otherwise noted.

Note 2: Icc measurement conditions (NORMAL, SLOW). Only CPU is operational; output pins are open and input pins are fixed.

TMP93PW76

2003-03-31 93PW76-16

4.3 AD Conversion Characteristics

Ta 20 to 70°C, Vcc 4.5 to 5.5 V

Parameter Symbol Min Typ. Max Unit

ADREF Vcc-1.5 Vcc Vcc V Analog Reference Voltage Supply

ADGND Vss Vss Vss V

Analog Input Voltage Range VAIN ADGND ADREF V

Analog Current for ADREF IREF 1.0 1.5 mA

Total tolerance (excludes quantization error)

(Ta 25°C, Vcc ADREF 5 V) ET ±3 LSB

TMP93PW76

2003-03-31 93PW76-17

4.4 Serial BUS Interface Timing

(1) I2C bus Logic Timing

Parameter Symbol Min Typ. Max Unit

SCL cycle tCYCSCL 2N

/fc s

SCL low pulse width tLOW 2N-1

/fc s

SCL High pulse width tHIGH 2N-1

/fc s

SDA Rising Time (Note 1) tRSDA s

SDA Falling Time (Note 1) tFSDA s

SCL Rising Time (Note 1) tRSCL s

SCL Falling Time (Note 1) tFSCL s

The time from start command write to start sheecense tGSTA1 2N

/fc s

Start condition hold time, start generation of the first clock after this tGSTA2 2N-1

/fc s

Delay time from SCL falling to data output (Note 2) tODAT1 5/fc s

Set up time of data output for SCL rising (Note 2) tSUODAT 0 s

The time of holding data for SCL rising (Note 3) tHODAT 4/fc s

The time from stop command write to starting stop sheecense tGSTP1 2N-1

/fc s

The time from SDA falling to SCL rising (during stop sheecense) tGSTP2 2N-2

/fc s

Stop condition set up time tGSTP3 2N-1

/fc s

Note 1: The time of rising/falling depend on the feature of bus interface.

Note 2: The worst case is at the first bit of slave address.

Note 3: The worst case is at the acknowledge bit.

Note 4: N: Diving value set by I2CCR1 <SCK 2:0>

SCK N

000 6

001 7

010 8

011 9

100 10

101 11

110 12

111 reserved

SCL

Start Command

tGSTA2

SDA

tSUODAT tHDODAT tHIGH tLOW

tCYSCL

tRSCL tFSCL

tGSTP2

tFSDA tRSDA

tGSTA1 tODAT1

Stop Command

tGSTP1 tGSTP3

TMP93PW76

2003-03-31 93PW76-18

(2) Master SCL output timing The I2CCR1 <SCK 2:0> are used to select a maximum transfer frequency directed from

the SCL pin in the master mode. When rising time of the output clock (tRC) is at least 8/fc [s], a high-level time of the output clock (tHC) is tSCL.

While the SCL line is fixed to low-level by a slave device,the output clock stops. The first clock (tHC [s]) after restart is (tSCL/2) tHC tSCL.

(a) In case of tRC< (8/fc) [s] tHC tLC tSCL/2 [s] (tSCL 1/fSCL [s])

(b) In case of tRC (8/fc) [s] tHC tSCL [s], tLC tSCL/2 [s]

SCL pin (Output)

1/FSCL [s] tHC tLC

tRC FSCL fSCL

0.5VCC

0.5VCC SCL pin (Output)

1/FSCL [s] tLC

tRC FSCL fSCL/1.5

tHC

TMP93PW76

2003-03-31 93PW76-19

(3) Clock Syncro 8 bit SIO mode a. SCK Input mode

Expression Parameter Symbol

Min Max Unit

SCK cycle tSCY2 25X s

SCK falling Latch output data tOHS2 6X s

Enable output data SCK raising tOSS2 tSCY2 16X s

SCK raising Latch input data tHSR2 6X ns

Enable input data SCK raising tISS2 0 ns

Note: X 1/fc

b. SCK Output mode Expression

Parameter Symbol Min Max

Unit

SCK cycle tSCY2 25X 2

11X s

SCK falling Latch output data tOHS2 2X s

Enable output data SCK raising tOSS2 tSCY2 2X s

SCK raising Latch input data tHSR2 2X s

Enable input data SCK raising tISS2 0 ns

Note: X 1/fc

SCK (Input Output mode)

SO (Output data)

SI (Input data)

tSCY2 tOSS2

tISS2

tHSR2

tOHS2

TMP93PW76

2003-03-31 93PW76-20

4.5 Read operation in PROM mode

DC/AC characteristics Ta 25 5 C Vcc 5 V 10 %

Parameter Symbol Condition Min Max Unit

VPP Read Voltage Input High Voltage (A0 to A16, CE , OE , PGM )

Input low Voltage (A0 to A16, CE , OE , PGM )

VPP

VIH1

VIL1

4.5

2.2

0.3

5.5

VCC 0.3

0.8

V

V

V

Address to Output Delay tACC CL 50 pF 2.25TCYC ns

TCYC 400 ns (10 MHz Clock)

200 ns

A0 to A16

tACC

D0 to D7 Data Output

OE

PGM

CE

TMP93PW76

2003-03-31 93PW76-21

4.6 Program operation in PROM mode

DC/AC characteristics Ta 25 5 C Vcc 6.25 V 0.25 %

Parameter Symbol Condition Min Typ. Max Unit

Programming Supply Voltage

Input High Voltage (D0 to D7, A0 to A16, CE , OE , PGM )

Input low Voltage (D0 to D7, A0 to A16, CE , OE , PGM )

VCC Supply Current

VPP Supply Current

VPP

VIH1

VIL1

ICC

IPP

fc 10 MHz

VPP 13.00 V

12.50

2.2

0.3

12.75 13.00

VPP 1.0

0.8

50

50

V

V

V

mA

mA

PGM Program Pulse Width PW CL 50 pF 0.095 0.1 0.105 ms

Note 1: The power supply of Vpp (12.75 V) must be set power-on at the same time or the later time for a power supply of Vcc and must be clear power-on at the same time or early time for a power supply of Vcc.

Note 2: The pulling up/down device on condition of Vpp 12.75 suffers a damage for the device.

Note 3: The maximum spec of Vpp pin is 14.0 V. Be carefull of a overshoot at the programming.

PGM

Unknown

A0 to A16

tPW

Data-in stable Data-out valid D0 to D7

VPP

OE

CE

![INT} || 13 INT]](https://static.fdocuments.in/doc/165x107/61cab154ad2220048e4756f8/int-13-int.jpg)

![FOR JUDGEMENT · sthalekar[int], ritesh agrawal[int], ram lal roy[int], rakesh kumar-i[int], rajkumari a banju[int], purvish jitendra malkan[int], praveena gautam[int], praveen jain[int],](https://static.fdocuments.in/doc/165x107/60315236cd2017262f2021dd/for-judgement-sthalekarint-ritesh-agrawalint-ram-lal-royint-rakesh-kumar-iint.jpg)

![[ORDERS (INCOMPLETE MATTERS / IAs / CRLMPs)]dinesh chandra pandey[int], ashok anand[int], arvind s. avhad[int], akriti chaubey [int], ajay kumar singh[int], abhas kumar[int] (1) ia](https://static.fdocuments.in/doc/165x107/60b5e2334a50260c3417ccf9/orders-incomplete-matters-ias-crlmps-dinesh-chandra-pandeyint-ashok-anandint.jpg)

![Brian Mitchell (bmitchel@mcs.drexel.edu) - Drexel University MCS680-FCS 1 Running Time of Programs int MSTWeight(int graph[][], int size) { int i,j; int.](https://static.fdocuments.in/doc/165x107/56649e7d5503460f94b809b4/brian-mitchell-bmitchelmcsdrexeledu-drexel-university-mcs680-fcs-1-running.jpg)