High-Voltage MOSFET Behavior in Soft-Switching Converters ...

Threshold Voltage Mosfet

-

Upload

santoshineepanda -

Category

Documents

-

view

222 -

download

0

Transcript of Threshold Voltage Mosfet

8/8/2019 Threshold Voltage Mosfet

http://slidepdf.com/reader/full/threshold-voltage-mosfet 1/6

Spring 2001 EE 8223 − Analog IC Design Page 17

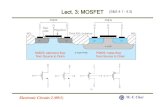

MOSFET Threshold Voltage

What affects the threshold voltage? ⇒ substrate doping, oxide thickness,

source-to-substrate voltage bias, gate material, and surface charge density

When V GS > V THN (nMOSFET), the semiconductor/oxide interface is

inverted, i.e., the inversion layer is formed. The associated depletion region

(beneath the inversion layer) thickness is described by

A

F ssid

qN X

φφε −=

2; where

i

AF

n

N

q

kT ln−=φ .

The charge attracted under the MOS gate is described by

F s Asid Ab qN X qN Q φφε −== 2' [C/m2]

In accumulation mode, φs = φF ⇒ Qb′= 0.

When increasing V GS (positively) results in φs = 0, the semiconductor surface

at the oxide interface becomes depleted.

Continuing to increase V GS till φs =− φF results in the formation of the

inversion channel.

Note that the value of V GS when φs =− φF is V THN . In this situation the

negative charge in the depletion region is described by

SBF Asid Ab V qN X qN Q +−== φε 22' [C/m2]

Between strong inversion and depletion, φs changed a total of 2φF .

8/8/2019 Threshold Voltage Mosfet

http://slidepdf.com/reader/full/threshold-voltage-mosfet 2/6

Spring 2001 EE 8223 − Analog IC Design Page 18

Threshold voltage expression:

( F SBF THN THN V V V φφγ 220 −++=

where

'

'0

'

''0

0 22

ox

bF FB

ox

ssbF msTHN

C

QV

C

QQV +−=

−+−−= φφφ

and

'

2

ox

Asi

C

N qεγ =

The value of φms is obtained by adding the contact potentials:

( ) ( ) F GF oxoxGms φφφφφφφ −=−+−=

Note that a voltage equal to V FB must be applied at the gate for φs = φF .

8/8/2019 Threshold Voltage Mosfet

http://slidepdf.com/reader/full/threshold-voltage-mosfet 3/6

Spring 2001 EE 8223 − Analog IC Design Page 19

MOSFET Operation

For strong inversion linear (nonsaturation) operation, see the gradual-

channel approximation derived in Section 5.3.1 of your text.

In the strong inversion linear region:

−−=

2)(

2 DS

DSTHN GSnn DV

V V V L

W KP I for V GS ≥ V THN and V DS ≤ (V GS−V THN )

−−=

2)(

2SD

SDTHPSG p p DV

V V V L

W KP I for V SG ≥ |V THP| and V SD ≤ (V SG−|V THP|)

In the strong inversion (SI) saturation region:

• For V DS = V GS – V THN , the inversion charge at the drain-channel

junction is zero (Q I ′(y=L) ⇒ 0), i.e., the channel becomes pinched

off.

• Substituting V DS,sat. (=V GS −V THN ) for V DS in the linear-mode

equation provides

[ ]2)(2

THN GSn

n D V V L

W KP I −= for V GS ≥ V THN and V DS ≥ (V GS−V THN )

• According to first-order theory, I D will not further increase for V DS

> V GS − V THN (not true!).

8/8/2019 Threshold Voltage Mosfet

http://slidepdf.com/reader/full/threshold-voltage-mosfet 4/6

Spring 2001 EE 8223 − Analog IC Design Page 20

• Why does the drain actually increase with V DS > V DS,sat.? Consider

the electrical gate of the MOSFET in SI saturation,

dldrawnelec X L L −=

Then [ ]2)(2

THN GSelec

nn D V V

L

W KP I −=

Channel length modulation (CLM) occurs due to the increase

depletion layer width as V DS increases

c Dn DS

dl

elec Dn

DS

elecTHN GS

elec

n

DS

n D I

dV

dX

L I

dV

dLV V

L

W KP

V

I λ⋅=

⋅=⋅−−=

∂

∂ 1)(

2

2

2

Typical values for λc range from approximately 0.1 V-1

(short

channel devices) to 0.01 (long channel devices).

Including CLM in our first-order drain current equation,

[ ])(1)(2

,2

sat DS DScTHN GSn

n D V V V V L

W KP I −+−= λ

• For minimum gate length devices, max V DS

is limited by punch-

through when the drain-substrate depletion region extends from

drain to source. This is BAD! The resultant high current can

destroy the device.

• For long channel devices, max V DS is limited by the drain

implant/substrate diode.

• Warning! The above analysis neglects mobility reduction with

increasing V DS.

8/8/2019 Threshold Voltage Mosfet

http://slidepdf.com/reader/full/threshold-voltage-mosfet 5/6

Spring 2001 EE 8223 − Analog IC Design Page 21

• Also, for large values of V DS, saturation will appear to occur for

values of V DS below V DS,sat due to the fact that Q I ′(y) is actually a

function of V DS (i.e., it is not constant). This is also the result of

velocity saturation in short channel devices. Velocity saturation

causes V DS,sat and I DS,sat to decrease.

Note that the MOSFET has 3 different levels of inversion: weak, moderate,

and strong. Within each level of inversion, the MOSFET can be saturated ornon-saturated. Hence, the MOSFET 6 different modes of operation.

8/8/2019 Threshold Voltage Mosfet

http://slidepdf.com/reader/full/threshold-voltage-mosfet 6/6

Spring 2001 EE 8223 − Analog IC Design Page 22

MOSFET Modeling

Review model parameters and their relationship to theory.

MOSFET Layout

Layout example (with schematic):

![Automotive MOSFETs - nexty-ele.com · Infineon automotive MOSFET portfolio offers benchmark quality, wide voltage range and diversified package Polarity Voltage class [V] Trench MOSFET](https://static.fdocuments.in/doc/165x107/5e166022fb6bdf66350ab0f0/automotive-mosfets-nexty-elecom-infineon-automotive-mosfet-portfolio-offers-benchmark.jpg)