The Erlangen Slot Machine An FPGA-Based Partially … Erlangen Slot Machine An FPGA-Based Partially...

Transcript of The Erlangen Slot Machine An FPGA-Based Partially … Erlangen Slot Machine An FPGA-Based Partially...

The Erlangen Slot Machine � An

FPGA-Based Partially

Recon�gurable Computer

Der Technischen Fakultät der

Universität Erlangen-Nürnberg

zur Erlangung des Grades

D O K T O R - I N G E N I E U R

vorgelegt von

Mateusz Majer

Erlangen 2011

Als Dissertation genehmigt vonder Technischen Fakultät derUniversität Erlangen-Nürnberg

Tag der Einreichung: 19.10.2010Tag der Promotion: 20.01.2011Dekan: Prof. Dr.-Ing. Reinhard GermanBerichterstatter: Prof. Dr.-Ing. Jürgen Teich

Prof. Dr. Dr. h.c. mult. Manfred Glesner

3

Abstract

Partial recon�guration is a special case of device con�guration that allows to

change only parts of a hardware circuit at run-time. Only a prede�ned region

of an FPGA is updated while the remainder of the device continues to operate

undisturbed. This is especially valuable when a device operates in a mission-

critical environment and cannot be disrupted while a subsystem is rede�ned

for performance or �exibility reasons. The triggering of partial recon�guration

can be instigated by user requests, detected changes of environmental factors

or operating system scheduling. It o�ers a novel possibility to dynamically load

and execute hardware modules, previously only known for software modules.

Partial recon�guration is useful in increasing the computational �exibility and

e�ciency by time-sharing the existing memory and logic resources on the device.

Using partial recon�guration, the functionality of a single FPGA is increased,

allowing fewer or smaller FPGA devices to be used. Embedded systems using

FPGAs supporting partial recon�guration can be customized in their hardware

at run-time with partial recon�guration. However, the design �ow and pe-

ripheral I/O architectures of these devices are not ideally suited for run-time

recon�gurable application development. Therefore, the bene�ts of partial re-

con�guration used in hardware designs are currently seen as limited.

The Erlangen Slot Machine (ESM) is introduced as a new FPGA-based dynam-

ically recon�gurable computer architecture supporting run-time customization

through the use of partial recon�guration at its architectural level. Built within

the DFG priority program 1148 Recon�gurable Computing its main goals are:

• making partial recon�gurable designs viable for real-world applications,

5

• operating system support for scheduling, placement and run-time recon-

�guration of partially recon�gurable modules,

• tool support for the development of run-time recon�gurable computation

and communication modules using new inter-module communication para-

digms, and to

• provide a platform for interdisciplinary research on algorithms, methods,

and applications using run-time recon�guration.

Its architectural support for partial recon�gurable modules simpli�es the design

and evaluation of modular and partially recon�gurable applications. Its key

bene�t is the decoupling of all peripheral I/O pins from the FPGA through

the use of an external crossbar. This feature enables �exible signal routing to

any recon�gurable region on the FPGA and e�ectively decouples the peripheral

I/Os from the �xed FPGA pins. Moreover, it provides a �exible platform for

run-time allocation models, real-time aspects and operating systems research

for run-time recon�gurable systems.

The design �ow tool SlotComposer automates the creation of partially recon-

�guration modules. It allows the automated insertion of inter-module commu-

nication structures. Moreover, it aids partial module placement with graphical

visualization and creates design �ow scripts for partial bitstream synthesis.

As an application example using partial run-time recon�guration, an advanced

video application was implemented on the ESM platform. To support real-time

video processing in the application, methods for hardware-software communi-

cation, hardware task placement, inter-module communication and decoupled

peripheral I/O access were analyzed and implemented for use on the ESM plat-

form.

6

Deutscher Titel und

Zusammenfassung

Die Erlangen Slot Machine � Einepartiell rekon�gurierbare FPGA-basierte

Computerarchitektur

Kurzzusammenfassung

Partielle Rekon�guration ist ein Spezialfall der FPGA-Kon�guration, bei der

zur Laufzeit eine vorde�nierte FPGA-Region mit einer neuen Schaltung geladen

wird, während dabei die übrigen Regionen des FPGAs nicht gestört werden. Dies

ist besonders erwünscht, wenn Geräte in einer kritischen Umgebungen arbeiten

und ihr laufender Betrieb nicht unterbrochen werden darf. In diesem Fall erlaubt

die partielle Rekon�guration die Schaltungen von Teilsystemen im laufenden

Betrieb auszutauschen, um die E�zienz und die Flexibilität der Schaltung, auf-

grund von wechselnden Anforderungen oder variierenden Umgebungsfaktoren,

zu verbessern.

7

Die Verwendung der partiellen Rekon�guration erhöht die Funktionalität und

Flexibilität eines einzelnen FPGAs, so dass kleinere und somit günstigere FPGA-

Bausteine verwendet werden können. Eingebettete Systeme mit FPGAs könnten

damit im laufenden Betrieb an sich wechselnde Anforderungen in Echtzeit ange-

passt werden, wodurch die Implementierung verschiedener Anforderungen in ei-

nem einzigen Baustein zusammengelegt werden kann. Allerdings haben verschie-

dene Module unterschiedliche Anforderungen an die I/O- und Speicherschnitt-

stellen, welche von aktuellen FPGA-Plattformen nicht berücksichtigt werden

und damit die Entwicklung von rekon�gurierbaren Anwendungen erschweren.

Diese Einschränkungen haben dazu geführt, dass im Bereich der partiellen Re-

kon�guration nur wenige Beispiele die praktische Anwendbarkeit der partiellen

Rekon�guration zeigen.

Die Erlangen Slot Machine (ESM) ist eine neuartige FPGA-basierte, dynamisch

rekon�gurierbare Computerarchitektur, die für den Einsatz von partieller Re-

kon�guration konsequent ausgelegt wurde. Ihre �exible Architektur vereinfacht

die Entwicklung und Evaluierung von modularen und partiell rekon�gurierbaren

Hardware-Designs. Ihr groÿer Vorteil ist die Entkopplung aller peripheren I/O-

Pins durch den Einsatz einer externen Crossbar. Diese ermöglicht eine �exible

Signalverteilung zu jeder rekon�gurierbaren Region auf dem FPGA, wodurch die

peripheren I/Os von den physikalischen FPGA-Pins entkoppelt werden. Darüber

hinaus bietet die ESM eine �exible Plattform für Entwicklung und Analyse von

Scheduling, Platzierungsverfahren und Echtzeitbetriebssystemen für laufzeitre-

kon�gurierbare FPGA-Systeme im Allgemeinen.

Mit dem Design-FlowWerkzeug SlotComposer wird die automatische Erstellung

von partiell rekon�gurierbaren Modulen verwirklicht. Es ermöglicht das auto-

matisierte Einfügen von Kommunikationsverbindungen zwischen partiellen Mo-

dulen, die graphische Platzierung von partiellen Modulen, als auch das Erstellen

von Design-Flow Skripten für die Kon�gurationsdaten-Synthese der partiellen

Module.

Als Anwendungsbeispiel für die partielle Rekon�guration wurde eine erweiterte

Video-Anwendung, die ein Assistenzsystem für die Erkennung von vorausfahren-

den Fahrzeugen und Fahrbahnmarkierungen, auf der ESM-Plattform vollstän-

dig implementiert. Zur Unterstützung der Echtzeit-Videoverarbeitung mit par-

tiell rekon�gurierbaren Video�ltern wurden Methoden für Hardware-Software-

Kommunikation, Modul-Platzierung, Inter-Modul Kommunikation sowie Zugri�

auf die I/O Pins der Peripherieschnittstellen entwickelt.

8

Acknowledgments

First and foremost, I would not have begun nor been able to complete this work

without the love, support, and encouragement of my partner Meline, my family

and my friends. Without them, this dissertation would not have been possible.

Moreover, I am indebted to my PhD adviser Prof. Jürgen Teich for support-

ing this exciting course of research and for advising on this dissertation. His

vision, enthusiasm, and expertise motivated me as much as I bene�ted from

his open support for the Erlangen Slot Machine endeavor. Thanks to my ex-

ternal committee members Prof. Manfred Glesner, Prof. Robert Weigel, and

Prof. Wolfgang Schröder-Preikschat. Moreover, special thanks go to Prof. Sán-

dor Fekete and Jan van der Veen for their assistance and great collaboration on

the conceptual part of the Erlangen Slot Machine and algorithmic part of the

ReCoNodes project.

I have had a great deal of assistance from the sta�, students and visitors to the

Department of Computer Science 12. In particular, I thank Hritam Dutta, Josef

Angermeier, Ali Ahmadinia, Christophe Bobda, Jan van der Veen, Dirk Koch

and Thilo Streichert for reviewing, discussing and helping me to clarify many

aspects of this work. Big thanks go also to Ulrich Batzer, Matthias Kovatsch,

Jan Grembler,André Linarth and Thomas Haller, without whom my work would

not exist in this form.

Furthermore, this work was supported by DFG grant TE 163/14-2, project Re-

CoNodes [1, 2], funded within the priority program 1148, Recon�gurable Com-

puting Systems [3]. I would also like to acknowledge the DFG for providing

9

additional support to build 20 prototypes of the ESM boards. And a special

thanks goes to Patrick Lysaght at Xilinx for his great support.

As the development of the Erlangen Slot Machine platform [4] was a huge task,

it would have been impossible without joint work on di�erent �elds:

Ulrich Batzer Taillight recognition demonstrator [5]Matthias Kovatsch Taillight recognition demonstrator [6]Bruno Kleinert Recon�guration manager driver [7]Thomas Stark Crossbar software driver [8]Plamen Shterev SlotComposer design �ow [9]Jan Grembler Video demonstrator [10]Christian Freiberger Recon�guration manager [11]Felix Reimann RMB communication [12]Peter Asemann PowerPC board support package [13]André Linarth ESM Motherboard [14]Thomas Haller ESM Babyboard [15]

I feel indebted to all persons involved in this great project and would like to

thank them again for their great work.

Mateusz Majer

München, July 2010

10

Contents

Abstract 5

Deutscher Titel und Zusammenfassung 7

Acknowledgments 9

1. Introduction 15

1.1. Motivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.2. Contributions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.3. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

2. Background 27

2.1. What is Recon�gurable Computing? . . . . . . . . . . . . . . . 27

2.2. Recon�gurable Hardware . . . . . . . . . . . . . . . . . . . . . . 28

2.2.1. Fine-Grained Architectures . . . . . . . . . . . . . . . . 29

2.2.2. Coarse-Grained Architectures . . . . . . . . . . . . . . . 36

2.2.3. Con�gurable Processors . . . . . . . . . . . . . . . . . . 38

2.2.4. Related Computing Platforms . . . . . . . . . . . . . . . 39

2.3. Partial Recon�guration . . . . . . . . . . . . . . . . . . . . . . . 39

2.4. Technical Advantages and Limitations . . . . . . . . . . . . . . 41

3. The Erlangen Slot Machine 45

3.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.2. Communication Models . . . . . . . . . . . . . . . . . . . . . . . 48

3.3. Implemented Architecture . . . . . . . . . . . . . . . . . . . . . 52

3.4. The Babyboard . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

3.4.1. Main FPGA . . . . . . . . . . . . . . . . . . . . . . . . . 59

3.4.2. The Recon�guration Manager . . . . . . . . . . . . . . . 60

3.5. The Motherboard . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.5.1. PowerPC . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.5.2. Crossbar . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

11

Contents

3.5.3. Video Input . . . . . . . . . . . . . . . . . . . . . . . . . 74

3.5.4. Video Output . . . . . . . . . . . . . . . . . . . . . . . . 75

4. Development of Partially Recon�gurable Modules 77

4.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2. Partial Design Flow . . . . . . . . . . . . . . . . . . . . . . . . . 79

4.3. The SlotComposer . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.4. Operating System Framework . . . . . . . . . . . . . . . . . . . 86

4.5. Real-time Recon�gurable Hardware Task Management . . . . . 90

4.5.1. Hardware Task Generation . . . . . . . . . . . . . . . . . 94

4.5.2. Design Flow . . . . . . . . . . . . . . . . . . . . . . . . . 95

4.6. Hardware Interfaces for Video Processing . . . . . . . . . . . . . 101

4.6.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . 101

4.6.2. HW/SW Communication . . . . . . . . . . . . . . . . . . 103

4.6.3. Video Input . . . . . . . . . . . . . . . . . . . . . . . . . 103

4.6.4. Video Output . . . . . . . . . . . . . . . . . . . . . . . . 104

4.6.5. Memory Interfaces . . . . . . . . . . . . . . . . . . . . . 104

5. Application Scenarios and Use Cases 107

5.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.2. Real-Time Video Processing on the ESM . . . . . . . . . . . . . 109

5.2.1. Data Flow . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5.2.2. Main FPGA Partitioning . . . . . . . . . . . . . . . . . . 111

5.3. Implemented Video-Engines . . . . . . . . . . . . . . . . . . . . 112

5.3.1. Basic Video Filters . . . . . . . . . . . . . . . . . . . . . 112

5.3.2. Edge-Engine . . . . . . . . . . . . . . . . . . . . . . . . . 115

5.3.3. Taillight-Engine . . . . . . . . . . . . . . . . . . . . . . . 116

5.4. A Point-Based Rendering Application . . . . . . . . . . . . . . . 124

5.4.1. Background . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.4.2. Rendering Pipeline . . . . . . . . . . . . . . . . . . . . . 128

5.4.3. Implementation Results . . . . . . . . . . . . . . . . . . 133

6. Conclusions 137

6.1. Summary of Contributions . . . . . . . . . . . . . . . . . . . . . 137

6.2. Interdisciplinary Research Platform . . . . . . . . . . . . . . . . 140

6.3. Future Work . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

A. Glossary 145

12

Contents

B. Technical Speci�cation of the ESM 149

List of Figures 149

List of Tables 156

Bibliography 157

Curriculum Vitae 177

13

1. Introduction

Over the years, embedded systems designers have used di�erent approaches to

design systems in ways that optimize and customize hardware to �t the speci�c

requirements of the application they are developing. These approaches fall into

software, recon�gurable hardware and user-speci�ed hardware categories.

Recon�gurable hardware devices are hardware devices in which the functionality

of the logic gates is customizable at run-time. The connections between the logic

gates are also con�gurable. Memories are used as look-up tables to implement

the universal gates, and are used to control the con�guration of the switches in

the interconnection network. The program that indicates the functionality of

each gate and the switch state is called a con�guration.

Field-Programmable Gate Arrays (FPGAs) are the most common type of re-

con�gurable hardware devices. Their functionality is set at power-up and can

be changed during run-time.

User-speci�ed hardware is used to create custom physical silicon to implement

the target device. This ranges from a minimal e�ort such as a gate array to a

fully-customized device with handcrafted features, known as Application Speci�c

Integrated Circuits (ASICs). Their functionality is set during manufacturing

and is immutable. However, the long development process, very high setup

costs preposition this approach for high volume applications only.

One currently new approach for compute intensive applications is stream com-

puting. It uses parallel software programming languages, that target massively

parallel processor arrays, such as Graphics Processing Units (GPUs). How-

ever, this approach is currently not suited for embedded applications because

15

1. Introduction

its power consumption of more than 100 Watts is too high for most embedded

systems [16, 17].

Applications implemented in hardware devices display e�ciency in concurrent

applications, achieved by using multiple parallel processing blocks. Coupled

with their �exibility to allow the embedded systems designer to tailor the device

to match their application's demands as closely as possible, hardware devices

achieve the highest possible throughput. The per-block power of an FPGA may

now be well be below that of DSPs, even though the chip-level power dissipation

is higher. DSPs typically consume 3-4 Watt and FPGAs 7-10 Watt but FPGAs

can often handle 10x the processing load by using multiple parallel processing

blocks [18].

Recon�gurable Computing (RC) has started with the advent of FPGAs and

hardware-oriented design languages like VHDL and Verilog. They enable a

10x to 100x gain over a conventional microprocessor in performance and func-

tional density (operations per area-time) [18]. The advantage of recon�gurable

computing comes from highly parallel data paths and post production pro-

grammability which allows data �ows to be highly specialized to the applica-

tion. Moreover, partial dynamic recon�guration enables run-time specialization

which brings about software like �exibility to the hardware domain.

Recon�gurable architectures can re-adapt the behavior of their hardware re-

sources to a speci�c computation that needs to be performed. Computing using

recon�gurable architectures provides an alternate paradigm to utilize available

logic resources on the chip analog to software multithreading. However, the

performance gains obtained by the use of recon�gurable devices are limited

as development complexity and system integration costs increase. Moreover,

programming hardware devices remains di�cult, usually requiring a hardware-

oriented language such as Verilog or VHDL. Hardware solutions can take an

order of magnitude longer to code and verify than software solutions which im-

pacts development costs and increases time to market. New high-level languages

like Impulse-C or Mitron-C can shorten the development time, but they need

further development to match VHDL's e�ciency [19].

All user-programmable features inside an FPGA are controlled by memory cells

that are volatile and, therefore, must be con�gured on power-up. These memory

cells are known as the con�guration memory, and de�ne the Look-Up Tables

(LUT) , signal routing, Input/Output Blocks' (IOBs) voltage standards, and all

16

Figure 1.1.: The architecture of the Xilinx Virtex family of FPGAs allows designmodules to be swapped on-the-�y using a Partial Recon�guration(PR) methodology [20, 21]. Each partial module is placed in a pre-de�ned area called PR region. This allows multiple design modulesto time-share resources on a single device, while the base design andand all external links continue to operate uninterrupted.

other aspects of the design. To program the con�guration memory, instructions

for the con�guration control logic and data for the con�guration memory are

provided in the form of a synthesized bitstream. Once an FPGA is programmed

it can be then partially recon�gured using a partial bitstream.

Partial Recon�guration (PR) is useful for systems with multiple functions that

can time-share the same FPGA device resources. In such systems, one section of

the FPGA continues to operate, while other sections of the FPGA are disabled

and partially recon�gured to provide new functionality. Partial recon�guration

is used to change the structure of one part of an FPGA design, while the rest of

the device continues to operate undisturbed. This is analogous to the situation

where a microprocessor manages context switching between software processes.

In the case of partial recon�guration of an FPGA, it is the hardware logic that

is being switched. Partial recon�guration provides an advantage over multiple

recon�gurations in applications that require continuous operation not otherwise

accessible during recon�guration. One example, illustrated in Figure 1, is a

software de�ned radio system. Because of the environment in which this appli-

cation operates, signals from radio and video links need to be preserved � but at

the same time the data processing format requires updates and changes during

operation. The underlying premise of this thesis is that with partial recon�gura-

17

1. Introduction

tion, the system can maintain these real-time links while other modules within

the FPGA are changed on-the-�y [20, 21].

The recon�guration process can be classi�ed whether only the whole device is

programmed as one entity only once (static full recon�guration), or whether

just parts of the device are recon�gured at run-time (partial recon�guration).

Before an FPGA is operational after recon�guration, a certain time elapses,

often called recon�guration time. These di�erent terms of recon�guration are

illustrated inf Figure 1. The partial recon�guration of individual slots achieves

a higher �exibility and reduces recon�guration times (gray areas).

A

A1 A2 A1 A2

M6 M5 M7

M8 M5 M9 M10

M1 M3

M4 M5

M2 M1 M2

timea)

b)

c)

Slot 6

Slot 5

Slot 4

Slot 3

Slot 2

Slot 1

Slot 6

Slot 5

Slot 4

Slot 3

Slot 2

Slot 1

Slot 6

Slot 5

Slot 4

Slot 3

Slot 2

Slot 1

Run-time full reconfiguration

Run-time partial reconfiguration

Static full reconfiguration

Reconfiguration time Execution time

time

time

Figure 1.2.: Di�erent recon�guration modes supported by the ESM platform: a)static full recon�guration, b) run-time full recon�guration, and c)run-time partial recon�guration.

18

1.1. Motivation

1.1. Motivation

Despite the announcement made by several companies in the last couple of years

about the design and production of new and mostly coarse-grained recon�g-

urable chips [22, 23, 24], the dominant part of today's recon�gurable computing

platforms are still �ne-grained and FPGA-based.

The growing capacities provided by FPGAs as well as their partial recon�g-

uration capabilities allow them to implement complex digital designs. Xilinx

FPGAs [25, 26, 27, 28] combine the advantages of large capacity and the ability

to support partial recon�guration. The Virtex-II series o�ers enough logic for

e�ciently implementing applications with high demand of resources, e.g., arising

in video, audio and signal processing as well as in other �elds like automotive

applications.

There are, however, open problems concerning module relocation: In order to

connect a module to other modules and/or pins, signals are often required to

pass through other modules. Those signals used by a given module and crossing

other modules are called feed-through signals. Using feed-through lines to access

resources has, however, two negative consequences, as illustrated in Figure 1.3:

• Di�culty of design automation: Each module must be implemented with

all possible feed-through channels needed by other modules. Because de-

signers only know at run-time which module needs to feed through a signal,

many channels reserved for a possible feed-through become redundant.

• Relocation of modules: Modules accessing external pins are no longer

relocatable, because they are compiled for �xed locations where a direct

signal line to these pins is established.

Many FPGA-based recon�gurable platforms such as [29, 30, 31, 32] o�er vari-

ous interfaces for audio, video capturing and rendering and for communication.

However, each interface is connected to the FPGA using dedicated pins at �xed

locations. Modules with access to a given interface such as a VGA input port

must be placed in the area of the chip where the FPGA signals are connected.

If the input or output signals are not grouped together then the relocation of

these modules becomes impossible. Until now, no platform on the market has

provided a solution to these problems.

19

1. Introduction

Figure 1.3.: The feed-through line problem with relocatable modules. Placing anew module B into slot two requires that the new module provides allfeed-through lines needed by slot one and three. This fact disablesany module relocation and makes it impossible to place moduleswith di�erent feed-through requirements into the other slots.

The most important problems limiting the use of partial and dynamic recon�g-

uration are:

• limited support for partial recon�guration,

• I/O-pin dilemma,

• inter-module communication dilemma and

• local memory dilemma.

These limits of existing FPGA-based recon�gurable computers are explained in

detail in Section 3.4:

Very few FPGAs allowing partial recon�guration exist on the market. These

few FPGAs, like the Virtex series by Xilinx [25], impose nonetheless some re-

strictions on the least amount of resources that can be recon�gured at a time,

for example column-wise recon�guration.

Many existing platforms include I/O peripherals like video, RAMs, audio, ADC

(analog to digital converter) and DAC (digital to analog converter) connected at

�xed pins of the FPGA device. As a consequence of these pin constraints, partial

recon�guration may be di�cult or even impossible, because a new module can

20

1.1. Motivation

require access to di�erent I/O pins. Another problem related to pins is that

the pins belonging to a given logical group like video, and audio interfaces are

not situated closely to each other. On many platforms, they are spread around

the device. A module accessing an external device will have to feed many lines

through many di�erent components. This situation is illustrated in Figure 1.4:

Two modules (one of which is a VGA module) are implemented. The VGA

module uses a large number of pins at the bottom part of the device and also

on the right hand side. Implementing a module without feed-through lines is

only possible on the two �rst columns on the left hand side. The e�ort needed

for implementing a recon�gurable module on more than two columns together

with the VGA module is very high. FPGA development boards from Celoxica

Ltd. [29], Alpha Data Ltd. [30], XESS Corp. , and Nallatech Inc. all exhibit the

same limitations. On the XF-Board [33, 32] from ETH Zurich, the peripherals

are connected to one side of the device. Each module accesses I/Os through an

operating system (OS) layer implemented on the left and right part of the device.

Many other existing platforms like the RAPTOR board [34], Celoxica RC1000

and RC2000 [29] are PCI systems that require a workstation for operation. The

use in stand-alone systems as needed in many embedded systems is not possible.

Modules placed at run-time on the device typically need to exchange data among

each other. Such a request for communication is dynamic due to run-time mod-

ule placement. Dynamically routing signal lines on the hardware is a very cum-

bersome task. For e�ciency reasons, new communications paradigms must be

investigated to support such dynamic connection requests, for example packet-

based DyNoCs [35] or principles of self-circuit routing.

Modules requiring large amounts of local memory cannot be implemented since

a module can only occupy the memory inside its physical slot boundary. Stor-

ing data in o�-chip memories is therefore the only solution. However, existing

FPGA-based platforms often have only one or two external memory banks and

their pin connections are spread over the borders of the FPGA.

The design and implementation of a recon�gurable computing platform poses

many challenging problems. Motivation to research these challenging problems

is re�ected in the following topics and tasks, especially through related an rele-

vant research questions:

Hardware Support How should the hardware device be partitioned so that

multiple independent tasks can execute? Can multiple I/O streams be

21

1. Introduction

Figure 1.4.: Pin distribution of a VGA module on the RC200 platform. It can beseen that the VGA Module occupies pins on the bottom and rightFPGA borders. In consequence, only a narrow part on the left sideis available for dynamic module recon�guration.

supported? How hard is it to access external memory? How is con�gura-

tion data manged and who is controlling the recon�guration process?

Task Design Each task has to communicate with external I/Os or with other

running tasks. How does the task development process support inter-

module and external communication? What are global requirements for

supporting arbitrary task placement? How should relocatable tasks be

designed so they do not interfere with neighboring tasks? How can tools

automate the development process?

OS Framework Basic operating system services are needed for run-time schedul-

ing and placement. How can the overhead of the operating system be

minimized? Should the operating system itself be a hardware task or run

on a separate microprocessor? Additionally, the lack of advanced software

tools is a signi�cant bottleneck in application development with partial

recon�guration support.

To support parallel execution of hardware tasks analog to software multitask-

ing a well de�ned methodology for the development of these tasks has to be

established. At the operating system level hardware resources, caching of con-

�guration data for each hardware task, access to global memory and communi-

cation resources must be e�ciently manged. These challenging problems gen-

erate many questions that need to be solved in order to enable the creation of

a �exible recon�gurable platform, as illustrated in Figure 1.5. The operating

22

1.2. Contributions

system manages the recon�gurable hardware by providing an abstraction layer

between task request and the recon�gurable hardware device as illustrated in

Figure. Each task request fetches the corresponding module con�guration from

a module database. The scheduler determines the exact point in time for the

module to be loaded into the hardware device [36]. However, this can only be

performed if the placer can �nd a free region that the module can �t in. More-

over, the number of free regions can be further limited through defragmenting

of the device area which is caused by frequent loading of new modules [37].

Based on the above review of current platform capabilities, issues, and questions,

this thesis contends that the present underuse of partial dynamic recon�guration

is due in great part to a lack of a standardized development environment and

a common operating system framework platform to support its key technology

bene�ts.

Figure 1.5.: Overview of a recon�gurable computing platform. The recon�g-urable hardware device is controlled by an operating system whichloads partial tasks on request.

1.2. Contributions

The Erlangen Slot Machine, a new FPGA-based partially recon�gurable plat-

form, overcomes the I/O bottleneck of existing FPGA-based platforms by imple-

menting a crossbar oriented peripheral I/O architecture and dedicated external

23

1. Introduction

memory for up to six partial modules [38, 39, 40, 41, 42]. This recon�gurable

platform also includes an external processor for main control and a dedicated

FPGA for recon�guration management [43]. These architectural features o�-

load partial recon�guration support and management functions form the main

FPGA to external devices [44]. This enables the sole use of the main FPGA for

partial recon�gurable modules. Another resulting feature is a simpli�ed devel-

opment process as static control logic does not intervene with the development

of run-time recon�gurable tasks. Thus, up to 22 partial hardware tasks can be

loaded on demand while satisfying peripheral I/O access of each partial task

through the external crossbar [45].

Also new is the introduction of a tool support for an automated transformation

of hardware designs into partial hardware designs at the HDL-level. When a

part of an application is moved to a partial hardware module, the design �ow

was found to be very time consuming and error prone because a new top-level

module with intermediate communication modules and signals had to be cre-

ated. Therefore, a software tool called SlotComposer was developed to generate

communication glue logic needed for partial recon�guration at the top HDL-

level. The use of platform tailored communication schemes further reduces the

development time [46, 47].

The complexity of implementing a fully working video application on an FPGA

is high, especially if external memories and peripheral I/Os are used. To prove

the ESM concept's practicability for complex applications using partial recon-

�guration, a video processing application for lane and object detection for a

driver assistance system was successfully implemented [48, 49]. This applica-

tion utilizes real-time partial recon�guration and all features of ESM platform.

Our software tool hwtaskgen generates a set of partial recon�gurable hardware

tasks for benchmarking purposes. Each generated partial task has a simple

communication interface with the operating system �rmware running on the

PowerPC. The execution time and the physical size of each task is speci�ed

before its generation and is therefore �xed at design time. These features enables

the comparison of time overheads and di�erent scheduling strategies for partial

recon�guration on various FPGA platforms.

The second application implements a point rendering pipeline on the ESM plat-

form [50]. Point rendering is an alternative 3D rendering scheme based on point

clouds instead of traditional triangle meshes. The software part of the appli-

cation controls the rendering-pipeline in real-time and is used to precompute

24

1.3. Overview

coe�cients in �oating point format. The point rendering throughput of 60 mil-

lion pixels per second is independent of the camera view but limited by the

memory bandwidth required to read pixels from memory.

Not included in the scope of this thesis are additional contributions to the

following aspects:

• Dynamic NoC approach for the communication infrastructure in recon�g-

urable devices [51, 52].

• Packet routing in dynamically changing network on chip [53].

• Task scheduling and module-layout defragmentation for run-time recon-

�gurable architectures [54, 36, 55].

1.3. Overview

Chapter 2 describes technical advantages and limitations of recon�gurable com-

puting today. The chapter begins with the promise of recon�gurable computing

and details the aspects such as partial recon�guration and run-time environ-

ments for hardware tasks. It then describes the underlying technology which

consists of �ne-grained devices like FPGAs and coarse-grained devices. The for-

mer consists of Con�gurable Logic Blocks (CLBs) operating at bit level, while

the latter uses a sea of Arithmetic Logical Units (ALUs). Then, Chapter 2

details existing recon�gurable computing platforms and their limitations.

Chapter 3 presents the platform, hardware task and operating system models

upon which the Erlangen Slot Machine (ESM) is based. The chapter describes

the inter-module communication problem and provides several solutions, all of

which were implemented on the ESM platform. Then Chapter 3 presents the

ESM platform which resolves the limitations of existing recon�gurable platforms

and describes the physical implementation of the ESM Motherboard and Baby-

board. Finally, a �exible recon�guration management architecture is detailed

and workload scenarios are presented.

Chapter 4 describes the development tools which were implemented to support

the partial module development. It also depicts the operating system framework

which controls the execution of hardware tasks at run-time.

25

1. Introduction

Chapter 5 reports on application scenarios which were implemented on the ESM

platform. The main application domain is video processing. In the �rst applica-

tion a real-time video processing architecture for a driver assistance application

is presented. The second application uses the ESM for real-time point-based

rendering of 3D images.

Chapter 6 concludes the thesis with a review of the results, their signi�cance,

and provides directions for further study. The appendix contains a glossary and

the technical speci�cation of the ESM platform.

26

2. Background

2.1. What is Recon�gurable Computing?

The promise of recon�gurable computing is to deliver high performance accel-

eration for the domain of compute intensive applications which are implicitly

suited for pipelining and parallel execution.

FPGA-based systems are commonly used in recon�gurable computing because

of their hardware recon�guration, application performance, and wide spread

availability. In most common scenarios, FPGAs are used in high performance

computing or in low volume, high-end hardware devices, like backbone Internet

routers or ASIC emulators. Traditionally, FPGAs are being used as glue logic

between various I/O standards or interfaces. With the help of hardcore and

softcore processors, FPGAs begin to enter the embedded market by integrating

I/O devices, memory controllers and microprocessors into one device. This

positions them directly against established System-on-Chip solutions for low to

mid volume quantities, as lower FPGA prices and higher gate counts for each

new generation help to drive this change.

Systems using FPGAs retain the execution speed of dedicated hardware but

also have software like functional �exibility. The logic within the FPGA can be

changed if or when it becomes necessary. Bug �xes and functionality upgrades

can be applied as easily as their software counterparts. For example, releasing

a new WLAN access point with a pre-draft speci�cation is feasible with a sys-

tem based on recon�gurable hardware. When the �nal draft is �nalized, then

the internal logic can be redesigned to re�ect the changes and automatically

27

2. Background

uploaded to the system. After the next system start the device will be able to

use the new version of the protocol.

Recon�gurable computing involves manipulation of the logic within the FPGA

at run-time. In other words, the design of the hardware may change in response

to the demands placed upon the system while it is running. Here, the recon-

�gurable hardware acts as an execution engine for a broad range of hardware

task, in the same manner as a microprocessor acts as an execution engine for a

variety of software threads. This allows the system designer to �t more hard-

ware tasks on the chip than physically possible, which works especially well

when some hardware tasks are occasionally idle. One application example is

a smart surveillance camera that supports multiple video denoising �lters and

multiple object trackers. Depending on weather and lighting conditions, the

most appropriate components are selected and recon�gured by the operating

system on-the-�y. This enables the camera to deliver consistent performance at

reasonable device costs while operating in a changing environment.

2.2. Recon�gurable Hardware

What exactly is recon�gurable hardware and how does it compare to a stan-

dard microprocessor? In both cases, their �xed physical functionality consist of

transistors and wires built on a silicium substrate. Internal memory elements

are used to program the functional units and interconnect structures to form an

instruction speci�c data path. This data path controls the data source and sink

for each functional unit found on the device.

The main di�erence is the frequency with which the functional units change

their behavior, the number of functional units, and the programmable intercon-

nect di�er signi�cantly, as shown in Table 2.1. Basically, the microprocessor

programs its functional units with every instruction it processes. Being a se-

quential machine, its objective is to process as many instructions in as few clock

cycles possible. However, each instruction must be fetched from external mem-

ory, decoded, executed, and �nally the result must be stored. On the other

hand, a recon�gurable hardware device tries to process as much data in parallel

as possible using as few instructions as possible. This is achieved through a very

high number of small and simple functional units as well as an extensive and

programmable interconnect. Recon�gurable devices are programmed only once

28

2.2. Recon�gurable Hardware

at start-up to provide an application speci�c parallel data path until they are

powered down.

On one side, the microprocessor is built to process billions of instructions per

second with inherently �exible and sequential conditional data �ow. On the

other side, a recon�gurable device can process billions of data words with one

programmed con�guration. Both models have their advantages, as the sequen-

tial compute model is better suited for control intensive applications, which

on the other hand are not suited for massively parallel architectures found in

recon�gurable devices.

Key Parameters Recon�gurable Devices Microprocessors and

DSPs

Number of

Functional Units

Typically� 64, up to hundreds of

thousands

Typically� 32

Instructions per

second

Few, as up to Billions of data

words are processed and not

instructions

Billions

Computation

paradigm

Parallel data computation with

high-performance custom memory

I/O architecture

Sequential

instruction

processing

Table 2.1.: Conceptual di�erences between recon�gurable hardware and micro-processors depicted with the help of architectural key parameters.

2.2.1. Fine-Grained Architectures

The most successful recon�gurable device is the FPGA, which stands for Field-

Programmable Gate Array. Its programmable fabric consists of an array of �ne-

grained logic blocks that operate on the bit level. The array and the interconnect

structure are illustrated in Figure 2.1.

The chip area of an FPGA consists of Con�gurable Logic Blocks (CLBs) ar-

ranged in a mesh structure, as shown in Figure 2.1 and 2.2. Each CLB contains

several slices and is connected to a switch box which enables distance and local

connections to other CLBs. Each slice insides the CLB is a self contained logic

block with two Look-Up Tables (LUTs) and corresponding �ip-�ops, as shown

in Figure 2.3. Signals used for carry signal propagation can be directly linked to

29

2. Background

upper and lower neighbor CLBs in order to allow e�cient synthesis of adders.

The space between the CLBs is �lled with interconnect consisting of segmented

wires and programmable switch points which occupy up to 90% of the FPGAs

chip area [56]. The edges of the chip contain Input/Output Blocks (IOBs) and

Digital Clock Managers (DCMs) as in the case of the Xilinx Virtex-II archi-

tecture. The regularity of the mesh structure is disrupted by memory blocks

and embedded hardware multiplier columns, as illustrated in Figure 2.2. In

case of the Virtex-5 architecture [27], the IOBs are grouped into I/O banks and

distributed in special columns inside the CLB array.

The XC2064 from Xilinx [57] was introduced in 1985 and was the �rst commer-

cially available FPGA. It distinguished itself from previous programmable logic

devices through 64 con�gurable logic blocks and a �exible interconnect between

them. Its SRAM based con�guration memory de�nes the functionality of each

logic block and their connections but could only be programmed at start-up. In

1996 Xilinx introduced the XC6200 series [58], the �rst partially recon�gurable

FPGA. One of today most advanced FPGAs, the Virtex-5 family [59, 27] is still

SRAM based and contains up to 330000 logic blocks coupled with dedicated

hardware blocks for I/O, memory, clock management and dedicated arithmetic

units. Moreover, it allows to reprogram parts of its logic blocks and interconnect

during run-time.

CLB Switch box Logic block

Routing channel

Figure 2.1.: Basic logical structure of an FPGA device.

30

2.2. Recon�gurable Hardware

During the programming process of an FPGA con�guration data is written into

an internal SRAM based con�guration memory. The programming process is

called full con�guration or recon�guration because all internal elements of the

FPGA are set to a new state which implements the desired digital design. The

con�guration data, also called bitstream, speci�es the functionality of each logic

block and connections between them. Thus, every SRAM based FPGA must

be con�gured from an external source prior to its operation.

Partial recon�guration is restricted to only a part of the FPGA device area and

can be performed only during run-time. This enables the design of computing

elements which are adaptable during run-time. Moreover, this allows to dynam-

ically modify, replace or add system components while the remaining circuits

remain to operate undisturbed [60, 61].

Today SRAM based con�guration storage dominates, although other non-volatile

technologies are available. The two main vendors are of SRAM based FPGAs

are Xilinx and Altera. Flash storage of con�guration data is used for example

in ProASIC devices from Actel [62] and LatticeXP devices from Lattice Semi-

conductor [63]. Storing con�guration data inside the FPGA in a �ash memory

has the bene�t of instant device start-up since no data has to be loaded from

an external source as in the case of SRAM based FPGAs.

The downside of �ash memory is its slow write access which is several orders

of magnitude slower than SRAM. One-time programmable anti-fuse technology

used by Actel [64] provides the most secure and restricted programming scheme

as the con�guration of the FPGA cannot be changed or read back after the �rst

device initialization.

FPGA's ability to work e�ciently on single bit signals is termed as �ne-grained

recon�gurable hardware. Boolean functions and �nite state machines can be

implemented in parallel fashion with maximum performance on these architec-

tures. This is due to the simplicity of each k-bit wide look-up table (LUT) inside

every con�gurable logic block (CLB) that can be programmed to compute every

k-ary Boolean function f : Bk → B , where B = {0, 1}. However, large wordlength computations, for example greater than 128 bit, start to cause intercon-

nect congestion problems. This manifest itselfs in timing problems and lengthy

place and route phases as thousands of functional units have to be connected

together under strict timing constraints.

31

2. Background

Figure 2.2.: Global view of the array structure inside an Xilinx Virtex-II FPGA.Note that the interconnect between the CLBs is not shown but com-prises 80% to 90% of the total chip area [65, 56].

The Virtex-II 6000 FPGA from Xilinx [25] is the main computing engine of the

Erlangen Slot Machine (ESM) that has been built to overcome many problems of

partial recon�guration mentioned in Section 1.1. This FPGA devices contains a

large number of resources on a single chip, as listed in Table 2.2. In the following

we will describe the structure and all important elements of this FPGA family.

CLB Array Size 96*88Number of Slices 33792

Max. Size of Distributed RAM 1.056 MbitBlock Multipliers 144

BlockRAMs 144Max. Size of BlockRAM 2.592 Mbit

DCMs 12

Table 2.2.: Technical data of the Virtex-II 6000 FPGA from Xilinx [25].

The FPGA contains an array of 8488 Con�gurable Logic Blocks (CLBs) which

is overlaid with a second sparse array of Block Multipliers and BlockRAMs,

as shown in Figure 2.2. The connectivity to external devices is provided by

32

2.2. Recon�gurable Hardware

dedicated I/O blocks which are located near each I/O pin. The Global Clock

Mux an the Digital Clock Manager (DCM) are used for global clock distribution

and for clock cycle adjustments of individual areas on the chip. The interconnect

between CLBs is not shown in this �gure.

Con�gurable Logic Block The CLB is the main building block of each FPGA

structure. The number of CLBs located on a FPGA and the interconnect struc-

ture de�ne its performance and the complexity level of a logic design that can be

implemented. More CLBs allow to build more complex, parallel, and pipelined

digital designs.

The CLB itself is subdivided in smaller parts, called slices. In the Virtex-II

FPGA family four slices are located inside each CLB and all four of them are

connected to a switch matrix and a fast connect bus. Figure 2.3 depicts the

internal connections inside a CLB. The fast connect bus allows the direct con-

nection of slices which are located in close proximity. Connections not supported

through the fast connect bus are routed outside the CLB through the switch

matrix.

Figure 2.3.: Internal structure of a Con�gurable Logic Block and a slice element.The left �gure shows that a CLB consists of four slices and a switchmatrix for long distance connections [25]. The right �gure depictsthe internal structure of a slice. It can be con�gured to implementlogic functions or used as a memory element. Each slice containstwo registers (Flip-Flops).

33

2. Background

Slice Slices are basic elements inside each CLB that implement logic functions.

For Virtex FPGAs, each slice contains two look-up tables and two �ip-�ops. The

�ip-�ops can be used to store the output of a look-up table. All logic functions

can be implemented with the help of LUTs. Boolean functions with four inputs

can be realized with a LUT by storing a complete truth table for this function.

Functions of arbitrary input width can be implemented through the concate-

nation of several LUTs. Because the con�guration of the truth table is stored

in SRAM cells, each CLB can be con�gured to act as a shift register or sim-

ple memory cell. In the latter case, the term Distributed Memory is used for

simple memory cells which are based on LUTs. The Virtex-II 6000 FPGA can

implement up to 1056 Kbit of Distributed Memory on chip. However, the use of

look-up tables for memory purposes renders them unusable for the implemen-

tation of logic functions.

BlockRAM To save logic resources, memory can be directly instantiated in

dedicated memory blocks found inside the FPGA. These memory blocks are

called BlockRAMs and have a size of 18 Kbit. The accumulated memory size

on the Virtex-II 6000 FPGA is 2592 Kbit. BlockRAMs are located in special

columns on the FPGA, as shown in Figure 2.2. Moreover, each memory block

has a dual ported address and data interface to allow two independent reads

or writes on the memory. Concatenation can be used to create larger memory

blocks. Therefore, BlockRAMs are the best choice for the implementation of

large memory blocks as long as the required memory size can be �t in and

timing constraints are met. Otherwise, external memory resources have to be

used with the drawback of higher latencies and higher power consumption for

external I/O access.

Block Multipliers Similar to �xed BlockRAM elements, the Virtex-II FPGA

family contains �xed hardware multipliers. Due to their �xed hardware func-

tionality they execute very fast and do not consume any logic resources. They

are physically grouped with the BlockRAM columns, as shown in Figure 2.2.

Each Block Multiplier has a �xed input size of 18 bit and the Virtex-II 6000

FPGA contains 144 multipliers.

Digital Clock Manager Clock distribution inside the FPGA is critical feature.

The Digital Clock Manager (DCM) is a vital element of the clock net. The DCM

34

2.2. Recon�gurable Hardware

can synthesize a custom clock frequency with an adjustable clock phase.

Bus-macros Bus-macros are FPGA speci�c hard-macros, �xed logic blocks

that are pre-placed and pre-routed. They are used as �xed data paths for signals

going in and out of a recon�gurable module as shown in the following �gure [21].

The HDL code should ensure that any recon�gurable module signal that is used

to communicate with another module does so only by �rst passing through a

bus-macro. There are device-speci�c versions of bus-macros.

Each bus-macro provides a �xed number of bits for the inter-module communi-

cation, typically 8 or 16 bits. Also custom made bus-macros with user de�ned

data width are possible to design but require extensive overhead for the design

and routing of these hard-macros. The number of instantiated bus-macros must

match the number of bits traversing the boundaries of the recon�gurable mod-

ules. As an example, if recon�gurable module A communicates via 32 bits to

module B, then four (32/8) bus-macros with 8 bit will need to de�ne the data

paths between modules A and B.

If a signal passes through a recon�gurable module connecting the two modules

on either side of the recon�gurable module, bus-macros must be used to make

that connection. This e�ectively requires creation of an intermediate signal

that is de�ned in the recon�gurable module. The signal cannot be actively used

during the time the recon�gurable module is being con�gured.

There are several di�erent types of bus-macros supplied by Xilinx, allowing

designers to choose from signal directions that are left-to-right or right-to-left

for Virtex-II/Pro; left-to-right, right-to-left, top-to-bottom, or bottom-to-top

for Virtex-4 FPGA, as shown in Fig. 2.4. The physical width of the bus-macro

can also be chosen (wide - 4 CLBs wide or narrow - 2 CLBs wide) and whether

signals passing through the bus-macro are registered or not (synchronous vs.

asynchronous).

However, most vendor provided bus-macros, regardless of direction or physical

width, provide eight bits of data width and enable/disable control. This �aw can

be eradicated with the use of custom made bus-macros, as used in the ReCoBus

[66] or the Caronte project [67]. However, both projects require an additional

design �ow with very device speci�c and technology dependent libraries.

35

2. Background

PartialReconfigurable

Module

PartialReconfigurable

Module

L2RL2R R2LR2L

R2LR2L L2RL2R

Figure 2.4.: Usage of bus-macros inside a Virtex-II FPGA between partial re-con�gurable modules (PRMs) and the static base design or otherpartially recon�gurable modules.

2.2.2. Coarse-Grained Architectures

Coarse-grained dynamic recon�gurable devices promise to deliver higher perfor-

mance at a lower cost than FPGAs. Their goal is to increase performance for

a given application domain by reducing �exibility. However, they are no longer

capable of implementing arbitrary digital circuits like FPGAs.

Similar to an FPGA, coarse-grained devices consist of an array of Processing

Elements (PEs) whose functions and interconnect can be changed during run-

time. A PE provides an ALU for numerical and logical calculations, logic for

shift/mask operations, a register �le and multiplexers for switching the data

�ow between PEs.

The processing element is called coarse-grained is no more bit oriented, as its

data path width can range from 8 bit to 64 bit. Compared to FPGAs, a coarse-

grained device operates on data words and not on single bits. Therefore, the

ALU is optimized for one speci�c word length. This reduces the costs and the

power consumption through a smaller die size, compared to an ALU structure

implemented in an array of LUTs on an FPGA device. The limited number

of processing elements and a restricted interconnect structure reduce �exibility

but also the amount of con�guration data. This leads towards faster con�gu-

ration times (within a few clock cycles) of a coarse-grained architecture when

compared with FPGAs. It also enables time multiplexed execution of parallel

threads through partial recon�guration. Example of coarse-grained recon�g-

urable architectures are RaPID [68], Matrix, Piperench [69], ADRES [70], and

PACT XPP [71]. Figure 2.5 shows the array and internal PE structure of a

36

2.2. Recon�gurable Hardware

coarse-grained architecture called WPPA (weakly-programmable processor ar-

ray) [72, 73]. The data path width of the PE can be set at design time, varying

from 8 bit to 64 bit. Together with interconnect customization this enables the

designer to select the most appropriate architecture for a speci�c application

domain. The operation of ALU, shift/mask logic, and data paths between com-

ponents are controlled with instructions stored in the local instruction memory.

During execution the PE reads only its local instruction memory forgoing slow

external memory accesses. The size of the PE array can be set at design time,

from 16 to 512 PEs. On the edge of the PE array, distributed memory mod-

ules can be provided to hold streaming data. Input/Output data is directly

transferred to/from each PE or distributed memory modules.

Figure 2.5.: Example of a coarse-grained recon�gurable architecture WPPA withparameterizable processing elements (WP PEs) [72, 73].

Dynamic recon�guration can be used to enhance the area e�ciency by changing

PE functionality and PE interconnect structure at run-time. By using a single

PE array for multiple tasks, the chip area gains computational density and post

production �exibility. The simplest way for it is to store multiple sets of con�gu-

ration data in each PE and to control the switching with a global con�guration

manager. New array con�gurations can be performed in the background if a

dedicated con�guration bus is implemented.

37

2. Background

2.2.3. Con�gurable Processors

In general, recon�gurable architectures target the acceleration of software. De-

pending on the application, the recon�gurable hardware can be loosely coupled

to a microprocessor via the processor bus or shared memory. This approach

allows to extend a standard computer workstation by attaching an accelerator

card to the Motherboard. The downside of this approach is limited bandwidth

and high communication latency between the host processor and the recon�g-

urable device which forces the accelerator to operate with relative autonomy. In

most cases, compute-intensive data is o�-loaded to the accelerator card and the

results are collected after processing, without intensive communication during

the processing phase. Thus, only compute intensive applications can bene�t

from acceleration. Examples of this loose system coupling include Splash2 [74],

Celoxica RCHTX [75], ClearSpeed [75], and other PCI or PCIe based recon-

�gurable accelerator boards. Other examples are also the Cray XD1 and SGI

RC100 accelerator cards for high performance clusters. They both contain two

large coprocessor FPGAs with access to local high speed memory and custom

communication links which can be used transparently by the software applica-

tions.

In more e�ective schemes for closely-coupled systems, the recon�gurable hard-

ware can be implemented as a coprocessor connected directly or through a

dedicated memory bu�er to the processor. GARP [76], REMARC [77], and

MorphoSys [78] are examples of such architectures.

The integration of a recon�gurable fabric (also called recon�gurable functional

unit) into to the data path of a processor or embedding a microprocessor directly

into an FPGA generates a very tightly coupled system. In the �rst case, the

recon�gurable hardware becomes a integral part of the processor architecture.

The recon�gurable functional unit can be con�gured to compute application

speci�c custom instructions. These instruction can be used like any other pro-

cessor instructions. Through run-time con�guration of the recon�gurable unit

new custom instructions can be created on-the-�y. Examples of these architec-

tures are Stretch S5000 [79], OneChip [80], DISC [81], Chimera [82] and MOLEN

[83].

In the second case, the microprocessor itself is embedded inside the recon�g-

urable hardware. For example, the IBM PowerPC 405 hardcore processor is

physically embedded inside Virtex-II/Pro FPGAs [84]. Another method is to

38

2.3. Partial Recon�guration

generate custom softcore microprocessor for the FPGA which can be customized

to application speci�c needs but occupy valuable logic resources. This is per-

formed with optimized and FPGA speci�c IP-core generators which allow a high

degree of customization. Examples of such softcore microprocessors are Xilinx

MicroBlaze [85], Altera Nios-II [86], and ARM7 processor core [87] for Actel

FPGAs.

2.2.4. Related Computing Platforms

The potential to accelerate supercomputing applications motivated several projects

to explore recon�gurable computing systems. Similar to existing supercomput-

ers, a large number of FPGAs were embedded in dedicated network topologies.

Two examples from the early 1990s are the Splash-II [74] and the Programmable

Active Memory (PAM) [88]. Splash contained 32 and PAM 25 FPGAs. Both

systems proved their impressive performance by outperforming standard super-

computers in several application areas [89].

The Berkeley Emulation Engine [90] is a new member of the high performance

computing arena. The current BBE2 [91, 92] FPGA based platform is designed

to be modular and scalable in order to accelerate a wide range of application

domains such as, real-time signal processing, scienti�c computing, large scale

simulation and emulation. The platform is based on the BEE Motherboard

containing �ve large FPGAs with high speed memory and communication in-

terfaces. Depending on the application requirements a network of BEE Mother-

boards and storage modules is combined to create the recon�gurable computing

system. One example application is the Research Accelerator for Multiple Pro-

cessors Project (RAMP) [93, 94] which emulates a thousand core multiprocessor

system where each FPGA hosts several softcore processors.

2.3. Partial Recon�guration

FPGAs load their con�guration from external memory during start-up or can

be made to do so by asserting a chip reset signal. This means that the FPGA

must be re-programmed entirely and its current internal state is lost. In order

to bene�t from concurrent hardware tasks which can be loaded independently

39

2. Background

during run-time into the FPGA, partial recon�guration and read-back of the

internal hardware task state must be supported [25, 95, 21]. However, loading

tasks into the devices is a sequential process and the overhead for each task is

typically proportional to its con�guration data size.

Whenever possible, a reset of the FPGA should be avoided, because a complete

new con�guration has to be written to the FPGA whereby all internal states

are lost. Partial recon�guration, also known as partial dynamic or run-time

recon�guration, allows partial changes of the FPGA logic without a�ecting the

state of other logic blocks. This means that parts of the FPGA una�ected

by the partial recon�guration process continue to work without any interrupt.

Changes to a small block of logic will be always much faster than recon�guration

of the entire FPGA as the recon�guration overhead is proportional to the chip

area occupied by the logic block. The more con�guration overhead there is, the

more likely is that the system performance will be below that of �xed-hardware

version when partial recon�guration is performed too frequently.

A hardware task is functional hardware component/module that contains its

own con�guration and run-time dependent state information. Hardware module

relocation allows to load and execute a hardware task in any free recon�gurable

region. Hardware modules should be developed in a position-independent way

to be relocatable. However, the con�guration data, sometimes referred to as

bitstream or bit�le, references absolute CLB positions inside the FPGA. This

requires an extra translation step to change the position information inside the

bit�le to the desired recon�guration region. Otherwise, each partial module has

to be synthesized in a separate process for each possible recon�guration region.

To actually carry out a dynamic placement of a hardware module during run-

time, a few assumptions are required. First, it is desirable to add constraints on

the size and shape of the relocatable hardware module. These constraints limit

the number of possible choices within the FPGA and make run-time placement

algorithms more e�cient and e�ective. Second, inter-module and o�-chip com-

munication require �xed communication access points that must be known at

design time of a relocatable hardware task. Hence, every hardware task should

adhere to a standard communication interface. This paves the way for greater

hardware task re-use and is especially important if a hardware task library has

to be maintained.

As most hardware tasks are comparable to functional logic blocks, it is safe

to assume that many existing hardware designs can be split and migrated to

40

2.4. Technical Advantages and Limitations

relocatable hardware tasks. One goal to accomplish this migration in a time

e�ective manner is to build a thin wrapper around the existing logic block with-

out any modi�cations to its original behavior. This task wrapper itself is part

of a hardware task framework which is always present within the recon�gurable

device. The framework itself provides inter-task communication support, ac-

cess to o�-chip peripherals and external memory devices through a standard

interface.

Due to the dynamic nature of recon�gurable computing, it is helpful to have

software components manage various con�guration processes at run-time. These

task can be divided into:

• Deciding which hardware objects to execute, where on the device and

when.

• Swapping of hardware tasks into and out of the recon�gurable logic.

• Switching communication paths between hardware tasks or between hard-

ware tasks and peripheral I/O devices.

This embedded software is analogous to an operating system that manages exe-

cution of multiple software threads. Like threads, hardware tasks may have pri-

orities, deadlines, dependencies and communication/memory constraints. The

goal of the run-time environment is to organize this information and make de-

cisions based upon it. As there are decisions to be made while the system

is running, algorithms have to be developed for on-line scheduling and plac-

ing of hardware tasks. The on-line scheduler is responsible for deciding which

hardware tasks are currently running. However, it is not possible to run tasks

without the placer which manages the 2D free space hardware area within the

recon�gurable device. Moreover, the placer is also responsible for keeping track

of all used communication channels. In order meet all hardware task constraints

communication aware placement has to be combined with the scheduling pro-

cess, as for example it makes no sense to schedule a task for execution when its

memory or communication constraints cannot be met by the placer.

2.4. Technical Advantages and Limitations

Recon�gurable computing has the advantage of greater functional density through

the use of a more simple hardware device. Needed logic blocks can be loaded on

41

2. Background

demand into the recon�gurable device. The high device cost can be reduced to

the low cost of a smaller device and an additional memory required to store the

logic design. Because many new systems have a network connection, this cost

of extra con�guration memory can be cut by implementing on demand update

strategies directly into the operating system of the recon�gurable device.

There are several advantages of recon�gurable computing over general purpose

processors on one hand, and ASICs on the other hand:

• Acceleration of various compute-intensive applications and very high speed

implementations of sequential tasks.

• Easy support for bug �xes and upgrades in the �eld with no down time.

Moreover, recon�gurable devices enable aggressive time-to-market strate-

gies with only core features being implemented on roll out. Missing fea-

tures can be delivered later on via an upgrade. Moreover, this extends the

life cycle of the system, thus reducing costs for the owner.

• Hardware multitasking enables multiple applications to run concurrently

on the same device. This enables true recon�gurable computing with mul-

tiple optimized applications running concurrently on one recon�gurable

device. As parts of the application can be developed independently these

systems can have shorter design and implementation cycles.

• Hardware sharing between hardware tasks is realized because running

tasks can be replaced. Bene�ts are reduced device size, reduced power

consumption and overall lower costs.

• Shorter recon�guration times through partial recon�guration enable fre-

quent recon�guration changes if required by the application. This enables

self-adaptive systems which deliver consistent performance in changing

environments.

However, there are three main limitations which need to attract more attention

in order to move recon�gurable computing towards mainstream adoption.

Compilers and back-end tools for recon�gurable computing are still under devel-

opment. Not only are e�cient high level compilers supporting partial recon�gu-

ration missing but also the low level back-end tools coming from corresponding

42

2.4. Technical Advantages and Limitations

chip vendors must be improved for a productive design environment [19]. Com-

mercial support for partial recon�guration must also be available together with

a well de�ned design �ow.

Debugging support for partial recon�guration is currently not available as a

debugging methodology including supporting tools is not available. Clock dis-

tribution and communication channels in recon�gurable systems are another

problem source.

Finally, the inability to verify run-time recon�gurable systems is an obstacle

for medical, aeronautical and mission critical control systems. The only viable

option is to emulate the run-time behavior. This can be done by implementing

all partial recon�gurable tasks at the same time on a much larger device and

to select the correct module through additional multiplexers. However, the

recon�guration is only emulated and the recon�guration process itself is not

performed.

43

3. The Erlangen Slot Machine

3.1. Introduction

Partial recon�guration requires run-time loadable modules that are pre-compiled

and their bitstreams are stored in an external memory device, which will then

be used to recon�gure a dedicated region on the FPGA. Several models and

algorithms for on-line placement have been developed in the past, see e.g.,

[96, 97, 98, 3]. However, these algorithms are limited by two main factors.

First of all, the model assumptions are often not realistic enough for implemen-

tation on real hardware or require a tedious development process. Second, the

development process of recon�gurable modules is subject to many restrictions

that make a systematic development process for partial recon�guration di�cult.

Until now, no FPGA-based platform on the market provides a solution to the

problems of design automation for dynamically recon�gurable hardware modules

and their e�cient and �exible relocation. The purpose of the Erlangen Slot

Machine (ESM) [4, 99, 100, 101, 45, 40, 42] is to overcome many of the

de�ciencies of existing FPGA-based recon�gurable computers by providing:

• A new �exible FPGA-based recon�gurable platform that supports relo-

catable hardware modules arranged in so-called slots.

• Tool support for the development of run-time recon�gurable computa-

tion and communication schemes using new inter-module communication

paradigms.

45

3. The Erlangen Slot Machine

• A powerful recon�guration manager which enables various pre-processing

stages for fast bitstream manipulation. We call the pre-processing stages

plug-ins. For example, a relocation plug-in can be selectively activated

before a bitstream is uploaded to the FPGA.

Recon�guration times in the range of seconds [102] are not su�cient for ap-

plications that require a fast reaction to external events. Our hardware recon-

�guration manager is the foundation for recon�guration times in the range of

milliseconds. For example, these fast recon�guration times will allow a seamless

switching of video �lters in a video pipeline processing architecture.

The main goal of the Erlangen Slot Machine's architecture [99, 100, 103, 2] is

to accelerate application development as well as research in the area of partially

recon�gurable hardware. The Erlangen Slot Machine owes its name to this

arrangement of recon�gurable slots which can be changed independently. This

modular organization of the device simpli�es the relocation, primary condition

for a viable partially recon�gurable computing system. Each module moved

from one slot to another will come across equal resources.

The advantage of the ESM platform is its one dimensional (1D) slot-based

architecture with support for varying slot widths. Slots are prede�ned recon�g-

urable regions in which hardware tasks can be exchanged during run-time. The

slot architecture on the ESM enables the execution of independent as well as

communicating hardware tasks by delivering peripheral data through a separate

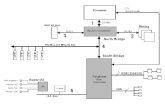

crossbar switch to each slot. This is shown in Figure 3.1.

We decided to design an o�-chip crossbar in order to leave as many resources

free on the FPGA for partially recon�gurable modules. The ESM architecture is

based on the �exible decoupling of the FPGA I/O-pins from a direct connection

to an interface chip. This �exibility allows independent placement of application

modules in any available slot at run-time. Thereby, run-time placement is not

constraint by physical I/O-pin locations, as the I/O-pin routing is performed

automatically in the crossbar; thus, the I/O pin dilemma is solved in hardware.

The ESM platform, as shown in Figure 3.1, is centered around a large FPGA

serving as the main recon�gurable engine and a second FPGA realizing the

crossbar switch for peripheral I/O access. These two FPGAs are placed on two