The 8051 Microcontroller

description

Transcript of The 8051 Microcontroller

The 8051 Microcontroller

Chapter 2

HARDWARE SUMMARY

2/24

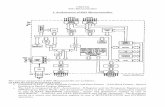

The features of MCS-51 ™ are:

• 4K bytes ROM (factory mask programmed)• 128 bytes RAM • Four 8-bit I/O (Input / Output) ports• Two 16-bit timers• Serial interface• 64K external code memory space• 64K external data memory space• Boolean processor (operates on single bits)• 210 bit-addressable locations• 4 microseconds multiply/divide

3/24

• Other members of the MCS-51™ family offer different combinations of on-chip ROM or EPROM, on-chip RAM, or a third timer

4/24

5/24

• 32 of the 8051’s 40 pins function as I/O port lines

• 24 of these lines are dual-purpose (26 on the 8032/8052), each can operate as I/O or as a control line or the part of the address or data bus

6/24

PORT 0• Dual-purpose port on pins 32-39• In minimum-component designs

general purpose I/O port• For larger designs with external

memory multiplexed address and data bus

PORT 1• Dedicated I/O port on pins 1-8• Used solely for interfacing to

External devices

PORT 2• Pins 21-28

• Dual purpose port

• General I/O port or as the high‑byte of the address bus with external code memory

PORT 3• Dual-purpose port on pins 10-17

• Multifunctional

• General-purpose I/O

7/24

8/24

PSEN• Program Store Enable is an output

signal on pin 29.

• Enables external program (code) memory.

• Usually connects to an EPROM's Output Enable(OE) pin

ALE• The Address Latch Enable output signal on pin 30.• When Port 0 is used in its alternate mode ALE is the

signal that latches the address into an external register during the first half of a memory cycle.

• Pulses at 1/6th the on-chip oscillator frequency and can be used as a general-purpose clock for the rest of the system.

• During the MOVX instruction one ALE pulse is missed.• This pin is also used for the programming input pulse for

EPROM versions of the 8051.

EA• The External Access input signal on pin 31

is generally tied high (+5 V) or low (ground).

• If low, programs execute from external memory only.

• The EPROM versions of the 8051 also use the EA line for the +21 volt supply (Vpp) for programming the internal EPROM.

RST• The RST input on pin 9 is the master

reset for the 8051.

• When brought high for at least two machine cycles, the 8051 internal registers are loaded with appropriate values for an orderly system start-up.

9/24

• Oscillator driven by a crystalconnected to pins 18-19

• The nominal crystal frequency is 12 MHz,up to 16 MHz

10/24

• Writing to a port pin loads data into a port latch that drives a FET connected to the port pin

• Pull-up resistor is absent on Port 0 (except in case external address/data bus

• “read latch” and “read pin” capability• For alternate function the output drivers are switched to

an internal address (Port 2), address/data (Port 0), or control (Port 3) signal

11/24

• Most microprocessors implement a shared memory space for data and programs

• Microcontrollers are rarely used as the CPU in “computer system”

• The 8051 implements a separate memory space for programs (code) and data

• Both the data and the code may be internal, both expand using external components to a maximum of 64K code memory and 64K data memory

• The on-chip RAM contains arrangement of general-purpose storage, bit-addressable storage, register banks and special function registers

• The registers and I/O ports are memory mapped, accessible like any other memory location

• The stack resides within the internal RAM, rather than external RAM as typical of microprocessors

12/24

• Any locations in the general-purpose RAM can be accessed feely using the direct or indirect addressing modes

• Internal RAM can also be accessed using indirect addressing through R0 or R1

• The 8051 contains 210 bit‑addressable locations, 128 from address 20H to address 2FH and the rest are special function registers

• 128 general-purpose locations are accessed as bytes or as bits

• The bottom 32 locations of internal memory contain the register banks

• The 8051 instruction set supports 8 registers, R0-R7

• “context switching”, separate sections of software use a private set of registers independent of other sections of software

• The 8051 internal registers part of the on-chip RAM, each register also has an address (PC and IR are exceptions)

• 21 SFRs at the top of internal RAM

13/24

• PSW Program Status Word at address D0H• Carry Flag (C or CY) is dual-purpose, during add or subtract• Auxiliary Carry Flag AC when adding binary-coded-decimal BCD• Flag 0 (F0) is a general-purpose flag bit available for user applications• Register Bank Select Bits, RS0 and RS1, determine the active register bank• Overflow flag (OV), after add or sub, set when arithmetic overflow• Parity Bit (P), check for parity after reception• B register, or accumulator B, address F0H, for MUL and DIV• Stack Pointer (SP),8 bit register, 81H address, contains address of the data currently on the top of the stack,

POP and PUSH• The Data Pointer (DTPR), access to external code or data memory, 16-bit register at addresses 82H (DPL)

and 83H (DPH)• Port 0 at address 80H,Port 1 at 90H, Port 2 at a0H, Port 3 at B0H, all Ports are bit-addressable• Timer Registers, Timer 0, TL0 at 8AH and TLH at 8CH, Timer 1, TL1 at 8BH and TH1 at 8CH• Serial Port Registers, The serial data buffer SBUF at 99H holds both the transmit data and receive data

Interrupt enable register IE at A8H, the interrupt priority register IP at B8H

14/24

• The Power Control Register PCON at 87H• An instruction that sets the IDLE bit is the last before

IDLE mode, in IDLE mode the CPU status is preserved and all register contexts are maintained

• Instruction that sets the PD is the last before Power Down Mode

• In power down mode besides everything else al functions are stopped, the only exit is a system reset

15/24

• During the first half of each memory cycle, the low-byte of the address is provided on Port 0 and is latched using ALE, a 74HC373 latch holds the low-byte of the address stable for the duration of the memory cycle

• During the second half of the memory cycle, Port 0 is used as the data bus, reading and writing

16/24

• External code memory is read-only memory enabled by PSEN signal

• Machine cycle is 1 micro second in duration

17/24

18/24

• External data memory is read/write memory• Up to 64K bytes of external data RAM can be

connected to the 8051

19/24

• If more than one 256-byte page of RAM is used, then a few bits from port 2 or some other Port, can select a page

20/24

• If multiple EPROMs and/or RAMs are interfaced to an 8051, address decoding is required

21/24

• A program can be loaded into the RAM (by writing to it as data memory) and executed (by accessing it as code memory)

22/24

8032/8052 ENHANCEMENTS

23/24

• The 8051 is reset by holding RST high for at least two machine cycles and then returning it low

24/24

• When RST returns low, programs execution always begins at the first location in code memory

• On-chip ROM is the same after reset operation