Stephen Norum LCLS Oct. 12, 2006 1 LCLS Machine Protection System Outline Overview of interim MPS...

-

Upload

vivian-wheeler -

Category

Documents

-

view

217 -

download

0

description

Transcript of Stephen Norum LCLS Oct. 12, 2006 1 LCLS Machine Protection System Outline Overview of interim MPS...

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20061

LCLS Machine Protection System

OutlineOverview of interim MPSUpdate on the interim MPS progressBurst and single shot modesInterim MPS scheduleFull MPS

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20062

Overview of Interim MPS

Using existing infrastructure (1553 MPS)Adding new signals and devicesInterim MPS will be used for gating beam

Single Shot ModeBurst Mode

MPS algorithm is responsible for both LCLS and CID beamPockels cell and MPS mechanical shutter limit laser rate on cathode

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20063

1553 MPS

MPS device faults are input to Latching Digital Input Modules (LDIMs)Algorithms running in local processors (APs) determine the max allowed rate based on these faultsThe supervisor (SP00) chooses the lowest rate from the APs for the beam’s max allowed rate

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20064

Status

LDIM Assignments and MPS DatabaseLDIM channels have been assignedVMS database has been built from these assignments

AlgorithmAlgorithm processor code is near completion and is being reviewed

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20065

Interim MPS Devices

Vacuum valves/statusBeam stoppersMagnet power suppliesProfile monitorsStandalone toroid, toroid comparatorsFlow switches and temperature monitorsJoule meterTone interrupt unit (TIU)Protection Ion Chambers (PICs)

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20066

Interesting Additions

MPS responsible for both CID and LCLS beamBAS II stoppers are used to isolate LCLSWhile BAS II stoppers are in

TIU is ignored as there are no devices between BX01 and TD11Algorithm rate limits LCLS beam only

While BAS II stoppers are outTIU works regularly—will zero rate all beams on any TIU faultAlgorithm rate limits both CID and LCLS beam

Algorithm switches modes automatically

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20067

Interesting Additions

Burst and Single Shot ModesRequired for profile monitor acquisitionBurst mode—create a specified number of pulses at a requested rateSingle shot—create a single pulseBoth modes are preceded and followed by no beam

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 20068

Burst Mode

ImplementationEPICS IOC obtains three pieces of information

Number of pulses in burstBurst Mode—a request to go enter burst modeBurst Request—the request to allow beam

An event receiver (EVR) provides timing data to IOCIOC uses the timing data to count pulsesWhen number of requested pulses have been created, the IOC drops the burst requestTiming is handled by IOC, rate limiting logic is handled by MPS algorithm

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200610

Burst Mode Logic

Burst Mode Burst Request Rate (Hz)

0 0 –

0 1 –

1 0 0

1 1 Burst Rate

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200611

Single Shot Mode

Implementation similar to Burst Mode“Counting” is done in hardwareA hardware flip-flop is set when single shot mode is requestedWhen the single shot request is made, a pulse is createdThe trigger for this pulse clears the flip-flop, ensuring only one pulse is created

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200612

Interim MPS Schedule

Creation Installation Testing CertificationSoftware SLC Database

- Device List Complete Complete Oct 13 N/A - LDIM Assignment Complete Complete Oct 13 N/A - Electrical Interconnect Complete Complete Complete N/AMPS Algorithm Oct 23 Oct 24 Dec 07 Oct 23IOC - Burst mode Nov 15 Nov 23 Nov 22 Nov 22 - Single shot Oct 11 Oct 13 Oct 11 N/A - Digital IO Database Oct 18 Oct 20 Oct 20 N/A

Date of Completion (2006)

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200613

Interim MPS ScheduleProcurement Installation Testing Certification

Hardware Linac PLIC - PLIC Processor Nov 01 Nov 03 Nov 06 N/APIC - Power supply Complete Complete Complete Complete - PICP Complete Complete Complete Complete - PICs Complete Dec 06 Nov 01 N/AUtilities - Gas Complete Dec 06 Dec 07 N/AIOC - VME Crate Complete Oct 18 Oct 16 N/A - EVR Complete Oct 18 Nov 22 N/A - Transition Module Complete Oct 18 Oct 16 N/A - Terminal Block Complete Oct 18 Oct 16 N/A - IOC Cable Complete Oct 18 Oct 16 N/A - IP Carrier Complete Oct 18 Oct 16 N/A - IP 445 Complete Oct 18 Oct 16 N/A - IP 440 Complete Oct 18 Oct 16 N/AMPS Electronics Oct 11 Oct 13 Oct 11 Oct 11Shutter - Shutter Controller Complete Nov 15 Complete N/APockels Cell - Pockels Cell AND Gate Oct 25 Nov 03 Nov 01 N/AFaston Complete Complete Complete N/A24V Power Supply Complete Oct 13 Oct 11 Oct 11LDIM Complete Complete Complete N/A

Date of Completion (2006)

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200614

Full MPS Requirements

Strict timing requirement—respond to MPS faults before next 120 Hz pulse (8.3 ms)Multiple rate limits determined by fault locationAutomatic Recovery—if requested, raise beam to before-fault rate after a fault is correctedFault logic based on how quickly an integrated loss threshold is exceeded

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200615

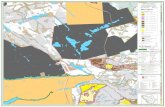

Simplified MPS Device Layout

(Note: Only PICs and PLICs shown. Many more devices are input to the MPS)

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200616

Full LCLS MPS

New hardware developed by MRFModified VME-EVR-200 (VME-EVR-235)Larger FPGA (XC2VP20)2× logic cells, 1.5× IO, 2× PPC coresAdditional SFP transceiver and clock circuit10/100 MAC/PHYMMC Slot for Atmel Flash Card128 MB SDRAM

Board has been ordered

Stephen Norum

LCLS MPS [email protected]

Oct. 12, 200619

Full LCLS MPS

MPS hardware provides a high-speed communication path back to EVG (2.5 Gbps)The MPS’s mitigation path is independent of the EVG and MPG, allowing the MPS to quickly respond to faultsDesign overview has been presented to small groupConceptual design review scheduled for November 9th