Stage VII : March 1 st 2004 COMPONENT LAYOUT

description

Transcript of Stage VII : March 1 st 2004 COMPONENT LAYOUT

Team W1Team W1Design Manager: Rebecca MillerDesign Manager: Rebecca Miller

1. Bobby Colyer (W11)1. Bobby Colyer (W11)2. Jeffrey Kuo (W12)2. Jeffrey Kuo (W12)3. Myron Kwai (W13)3. Myron Kwai (W13)4. Shirlene Lim (W14)4. Shirlene Lim (W14)

Stage VIIStage VII: : March 1March 1stst 2004 2004

COMPONENT LAYOUTCOMPONENT LAYOUT

Presentation #7: Rijndael Presentation #7: Rijndael EncryptionEncryption

Overall Project Objective:Implement the new AES Rijndael algorithm on

chip

18-525 Integrated Circuit Design Project

StatusStatus

Design Proposal Architecture Proposal Size Estimates/Floorplan Gate Level Design Layout

Component Layout Simulations

To be Done Top Level Routing Optimizations Everything else…

18-525 Integrated Circuit Design Project

Design Decisions & Design Decisions & ProblemsProblems

DECISIONSSplit ROM

Added logic because of split romSplit into 4 sub-ROMs

PROBLEMSTiming problems Routing Problems – Global LevelSizing of DFF to get equal rise and fall times

18-525 Integrated Circuit Design Project

Implementing Rijndael Encryption on Chip with Implementing Rijndael Encryption on Chip with this in mind:this in mind:

– Throughput– Speed

• At least 350 Mhz

–Size•As dense as possible while maintaining a ratio of 1:1

Project Goals & ObjectivesProject Goals & Objectives

18-525 Integrated Circuit Design Project

On-Chip Encryption to be used in:On-Chip Encryption to be used in:– Web servers

•High through put for passing through information•Hardware encryption generally 10-100x faster than software•Security of a private key greater if stored in hardware

–Software keys can be hacked, stolen and used elsewhere

Project Goals & ObjectivesProject Goals & Objectives

18-525 Integrated Circuit Design Project

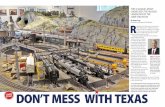

TOP

LEVEL

SCHEMATIC

Updated Floorplan325 um x 330 um

Metal 3

Metal 2

Metal 1

Metal 4

SBOX and Control Logic

Text DFFs and Add RoundKey

5th Round Key Expand

Input to SBOX Logic & SelectOutput and Input Logic

4 Rounds of Key Expand

4 Rounds of Round Permutation

Input/Output Logic

CLKDivider

Select & Input Logic

SBOX and Control LogicFinal Text Out

Key DFFs and Input Logic

METAL 1

METAL 2

METAL 3

METAL 4

POLY

LAYOUT – NO METAL

LAYOUT – Buses

Clock Divider

Add Round Key

DFF Input

S-box Mux Tree In

Demux 20

S-box Mux Tree Out

Final Text Output

Round Permutation

&

DFF

Key Expand & DFF

S-box Mux Tree Out

DFF Input Key

Demux 10

S-BOX - ROM

D-FLIP FLOP LAYOUT

18-525 Integrated Circuit Design Project

Waves D-FlipFlop Fall Time

18-525 Integrated Circuit Design Project

624.832 ps

531.818p

Waves D-FlipFlop Rise Time

18-525 Integrated Circuit Design Project

1.08073 ns

502.778p

Waves D-FlipFlop Propagation Time

18-525 Integrated Circuit Design Project

1.15726 ns

416.542p

DFF Setup Time

18-525 Integrated Circuit Design Project

174.371 ps

408.723p

100.237p

ROM Propogation Time

408.723p

Critical Path

18-525 Integrated Circuit Design Project

245.367 ps

1.03n

More on Critical PathMore on Critical Path

• Must include the setup time for DFF • Actual Critical Path is about 1.2n• Must double it as this logic only occurs on negative edge of clock• Speed Estimation: 417MHz

Questions?Questions?

18-525 Integrated Circuit Design Project

![BLP27M810 - AmpleonComponent layout 76.2 mm 40 mm BLP27M810 2400-2500MHz 20RO4350B [V1] C1 R1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11 C12 C13 amp00015 See Figure 1 for component layout. Component](https://static.fdocuments.in/doc/165x107/5f667bb6e67ef756c500581c/blp27m810-ampleon-component-layout-762-mm-40-mm-blp27m810-2400-2500mhz-20ro4350b.jpg)