source synchronous intf

Transcript of source synchronous intf

-

8/15/2019 source synchronous intf

1/44

EE141

System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 11

Chapter 14Chapter 14

High-Speed I/O InterfaceHigh-Speed I/O Interface

-

8/15/2019 source synchronous intf

2/44

EE141

System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !2

What is this chapter about?What is this chapter about?

High-speed I/O interfacesHigh-speed I/O interfaces Have been widely used in computer

communication and consumer electronics systems !re able to transmit and receive data at higher rates

with fewer I/O pins "ocus on

High-speed I/O architectures I/O interface testing

!t the #omponent/subsystem level

!t the System level$sing %"&-assisted 'ethods

(ew challenges in high-speed I/O and testing

-

8/15/2019 source synchronous intf

3/44

EE141

System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "3

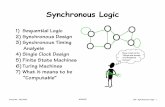

OutlineOutlineI) High-Speed I/O !rchitectures

*lobal #loc+ I/O !rchitectures

Source Synchronous I/O !rchitectures

Embedded #loc+ I/O !rchitectures

,asics on itter (oise and ,it Error .ate ,E.0

II) &esting of I/O Interfaces

&esting of *lobal #loc+ I/O

&esting of Source Synchronous I/O

&esting of Embedded #loc+ High-Speed Serial I/O

III) %"&-!ssisted &esting

!# oopbac+ &esting

High-Speed Serial-in+ oopbac+ &esting

&esting the E2uali3ers

I) System-evel Interconnect &esting

Interconnect &esting with ,oundary Scan

Interconnect &esting with High-Speed ,oundary Scan

Interconnect ,uilt-In Self-&est

) "uture #hallenges

I) #oncluding .emar+s

-

8/15/2019 source synchronous intf

4/44

EE141

System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 44

I. High-Speed I/O ArchitecturesI. High-Speed I/O Architectures

-

8/15/2019 source synchronous intf

5/44

EE141

System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . #5

(a) Global Clock (GC)(a) Global Clock (GC)

Synchroni3ed globalcloc+

System cloc+ for &5

data driving and .5

data sampling

#loc+ s+ew onboard limits its use

to 6 a few 177 'bps

data rate

-

8/15/2019 source synchronous intf

6/44

EE141

System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . $6

(b) Source Synchronous (SS)(b) Source Synchronous (SS)

&5 sends dataalong withstrobe anothercloc+0

.5 uses sent

strobe tosample the data

(o cloc+ orstrobe s+ewissue

-

8/15/2019 source synchronous intf

7/44EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . %

7

Source Synchronous (SS) (Cont’d)Source Synchronous (SS) (Cont’d)

Some designs use strobe/strobe8 to improve timing accuracy

-

8/15/2019 source synchronous intf

8/44EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . &

8

Source Synchronous (SS) (Cont’d)Source Synchronous (SS) (Cont’d)

imited by data todata s+ew due touneven channels ,oard layout E-' issues9 e.g )

coupling noises

ariation in driveamong channels !chieve up to

:1777 'bps datarates for wide bus #an improve data

rate with splitting

into many narrowerbus

-

8/15/2019 source synchronous intf

9/44EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . '

9

(c) Embedded Clock (EC)(c) Embedded Clock (EC)

,it cloc+ is embedded in the serial data and gets recovered at .5 via cloc+

recovery circuit in+ layer is composed of encoder/decoder

;hysical layer ;H

-

8/15/2019 source synchronous intf

10/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1(10

Basics on Jitter, Noise, and Bit Error Rate (BER)Basics on Jitter, Noise, and Bit Error Rate (BER)

-

8/15/2019 source synchronous intf

11/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1111

itter Components and !erminolo"y itter Components and !erminolo"y

% is bounded and . is unbounded

. is commonly modeled by a *aussian

-

8/15/2019 source synchronous intf

12/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1!12

Characteristics o# itter Component $%&sCharacteristics o# itter Component $%&s

ISI> different waveform traces %#%9 dual pea+ due to non-ideal reference voltage

;9 Saddle shape or *olden *ate suspension bridge

.9 ,ell shape or *aussian

-

8/15/2019 source synchronous intf

13/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1"13

itter Separation (a)' $%& ased itter Separation (a)' $%& ased

&ailfit is the industry de facto standard for separating % and .

$se . *aussians to model the &ail distributions

%istance between left and right *aussian means gives % p+-p+

!verage of left and right *aussian sigmas gives % sigma

-

8/15/2019 source synchronous intf

14/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1414

itter Separation (a)' C%& ased (Cont’d)itter Separation (a)' C%& ased (Cont’d)

&ailfit the #%"s

. model is an integrated *aussian

. becomes linear in ?-space

Same basic concept transformed data and model

-

8/15/2019 source synchronous intf

15/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1#15

itter Separation (b)' Spectrum ased itter Separation (b)' Spectrum ased

%% the estimated in time-domain via average first

; is the spi+es in the spectrum

. the bac+ground of the spectrum

f

p s d ( f )

PJRJ

-

8/15/2019 source synchronous intf

16/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1$16

itter *oise and E+ in ,-%imensionitter *oise and E+ in ,-%imension

,oth =itter andnoise can cause,E.

Eye and ,E.contour are @-

dimensional (o dot should bein the compliance3one to pass

-

8/15/2019 source synchronous intf

17/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1%17

II. esting o! I/O Inter!acesII. esting o! I/O Inter!aces

-

8/15/2019 source synchronous intf

18/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1&18

!estin" Global Clock (GC) ./O!estin" Global Clock (GC) ./O

&est with an !&E %ata and cloc+ are

generated and by

the tester level

pattern and timing0

Setup and hold timeis controlled by the

tester

%ata output is

strobed by the

tester

-

8/15/2019 source synchronous intf

19/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 1'19

!estin" Source Synchronous (SS) ./O!estin" Source Synchronous (SS) ./O

It is a difficult tas+ totest SS I/O %$& witha deterministic !&Ethat cannot use ane5ternal %$& cloc+ orstrobe

Strobe may begenerated by testervia a linear searchthat can be timeconsuming

Strobe timing marginis reduced by thetester accuracy/=itter

-

8/15/2019 source synchronous intf

20/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !(20

!estin" Embedded Clock (EC) ./O (a)' !0!estin" Embedded Clock (EC) ./O (a)' !0

&5 needs to be tested with a compliance cloc+ recovery defining a =itter transfer

function &"0

Eye-diagram =itter ;%" ,E. #%" manifests (, test

& is the eye-closure at a ,E. level e.g ) 17-1@0

+

_

CR/PLL

UI-TJBER

CDF

Zero

Level

Jitter

PDF

!-"

D#t# I$p%t

E&e-di#'r#()

Jitter PDF)

BER CDF) #$d

*e#s%re(e$t

&ste(

-

8/15/2019 source synchronous intf

21/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !121

!estin" Embedded Clock (EC) ./O (a)' !0 (Cont’d)!estin" Embedded Clock (EC) ./O (a)' !0 (Cont’d)

(, within the conte5t of an eye-diagram @-dimensional0

& and &( defines the compliance 3one

(o data sample should fall within the compliance 3one e.g ) ,E. 6A 17-1@0

-

8/15/2019 source synchronous intf

22/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !!22

!estin" Embedded Clock (EC) ./O (b)' Channel!estin" Embedded Clock (EC) ./O (b)' Channel

ossy channel is a low-pass filter

%igital s2uare input waveform becomes slow edge round waveforms due to

the loss of high-fre2uency contents

%ata-dependent =itter %%0 and %ata-dependent noise %%(0 manifest lossy

and intersymbol interference effects

-

8/15/2019 source synchronous intf

23/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !"23

!estin" Embedded Clock (EC) ./O (b)' Channel (Cont’d)!estin" Embedded Clock (EC) ./O (b)' Channel (Cont’d)

#hannel compliance test may be done in terms of S-parameter S@1

!n compliance BS@1B curve sets the upper limit for the test

&his method suffers from phase coverage s+ipping

-

8/15/2019 source synchronous intf

24/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !424

!estin" Embedded Clock (EC) ./O (c)' +0!estin" Embedded Clock (EC) ./O (c)' +0

.5 cloc+ recovery #.0 =itter tolerance/trac+ing test

&he compliance =itter tolerance mas+ is derived from .5 #. &" &he mas+ sets the lower limit for pass/fail test

,e able to tolerant/trac+ more lower fre2uency =itter is a +ey re2uirement for

.5 #.

-

8/15/2019 source synchronous intf

25/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !#25

!estin" Embedded Clock (EC) ./O (c)' +0 (Cont’d)!estin" Embedded Clock (EC) ./O (c)' +0 (Cont’d)

Corst case signaling is a .5 subsystem test

It covers .5 cloc+ recovery e2uali3ation sensitivity and internal =itter andnoise generation

,oth focused and subsystem test are important depending on the test goals

and needs

R,

orst .#se e&e

orst .#se

e&e ope$i$'

Ide#l

e&e

Jitter)

$oise

-

8/15/2019 source synchronous intf

26/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !$26

!estin" Embedded Clock (EC) ./O (c)' +0 (Cont’d)!estin" Embedded Clock (EC) ./O (c)' +0 (Cont’d)

! generic .5 test functional bloc+ diagram

#apable of providing both focused worst case signaling and full coverage.5 tolerance/stress test

,e able to emulate all =itter components and signal signatures with

controllability for magnitude and fre2uency band are critical

-

8/15/2019 source synchronous intf

27/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !%27

!estin" Embedded Clock (EC) ./O (d)' +e# Clock!estin" Embedded Clock (EC) ./O (d)' +e# Clock

;eriod or cycle-to-cycle =itter are not suitable metrics for reference cloc+ in

the common cloc+ architecture

;hase =itter after the reference cloc+ &" is called for

.eference cloc+ &" is a band-pass filter function

.eference cloc+ &" is determined by &5 ; .5 ; and transport delay

between them

! dB

f/ f "

Fre0%e$.&

* # ' $ i t %

d e ( d B

Pe#1i$'

-

8/15/2019 source synchronous intf

28/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !&28

!estin" Embedded Clock (EC) ./O (d)' +e# Clock (Cont’d)!estin" Embedded Clock (EC) ./O (d)' +e# Clock (Cont’d)

;hase =itter spectrum before and after the ref cloc+ &" is applied

;hase =itter spectrum after &" is what the .5 sees and related to .5 ,E.

Spread spectrum cloc+ SS#0 at : DD H3 is significantly suppressed by the

ref cloc+ &"

-

8/15/2019 source synchronous intf

29/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . !'29

System-e2el E+ EstimationSystem-e2el E+ Estimation

,E. can be estimated given the .5 input =itter spectrum and #. &" #. phase delay can cause the .5 ,E. to increase e.g ) region @0

&his method enables fast/high-through ,E. testing in production

R1 R2 R3 R4

Number of Samples

J i t t e r ( s e c o n d

s )

J i t t e r ( s e c o

n d s )

Number of Samples

Region 2Jitter characteristics

Region 3Jitter characteristics

-

8/15/2019 source synchronous intf

30/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "(30

!ester 3pparatus Considerations!ester 3pparatus Considerations

"ront-end bandwidth ,C0 needs to be high enough e.g ) Fth harmonic @)FG

the data rate0

% and . floor needs to be small enough to avoid margin loss due to the

tester =itter floor :ps for % and : sub-ps . at : 17 *bps data rate0 #loc+ recovery emulation is critical for &5 testing

&olerance and stressing is critical for .5 testing

'odel-assisted method e.g ) &ailfit =itter and ,E. e5trapolation method0

speeds-up the throughput of the tester

-

8/15/2019 source synchronous intf

31/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "131

III. "#-Assisted estIII. "#-Assisted est

-

8/15/2019 source synchronous intf

32/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "!32

3C ./O oopback Sel#-!est 3C ./O oopback Sel#-!est

d r i v e r

l a t c h

%5

S t r o b e

, u s # l o c +

b o a r d t r a c e d e l a y

w i r e d e l a y

w i r e d e l a y

b o a r d t r a c e d e l a y

s y s t e m c l o c +

c lo c + d o m a i n 1 c lo c + d o m a i n @d a t a

s t r o b e s

r e c e i v e r

l a t c h

Similar circuit as the receivingTesting hardware already exis

-- test for both drive/rec-- low overhead

Loop time = Tco (or Tvb Tsetup "# TvaThold

-

8/15/2019 source synchronous intf

33/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . ""33

S t r o b ed e l a y

s t r e s s t o f a i l b y

p u s h i n g

s t r o b e s t o t h e d a t a

e d g e

/ d r i v e r o r r e c e i v e r 0

b u f f e r g r o u p

s h o u l d h a v e t i g h t

d i s t r i b u t i o n

b u s g r o u p

f a u l t y b u f f e r

g o o d b u f f e r s d i s t r i b u t i o n

w i d e r d i s t r i b u t i o n A H l o c a l

d e f e c t i v e b u f f e r s

3C ./O oopback !est ased %e#ects 3C ./O oopback !est ased %e#ects

! widerspread ofdata validtime indicatefaults

-

8/15/2019 source synchronous intf

34/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "434

3C ./O oopback !est +esources and echanisms 3C ./O oopback !est +esources and echanisms

5i h S d S i l i k b k ! ti ( )5i h S d S i l i k b k ! ti ( )

-

8/15/2019 source synchronous intf

35/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "#35

5i"h-Speed Serial-ink oopback !estin" (a)' an5i"h-Speed Serial-ink oopback !estin" (a)' an

6nder-Samplin" ethod6nder-Samplin" ethod

$se a reference cloc+ close to the data fre2uency to strobe the data ratherthan the recovered cloc+

itter due to the channel carried in the received data bit timing

5i h S d S i l i k b k ! ti (b) ! t5i"h Speed Serial ink oopback !estin" (b) !est

-

8/15/2019 source synchronous intf

36/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "$36

5i"h-Speed Serial-ink oopback !estin" (b)' !est5i"h-Speed Serial-ink oopback !estin" (b)' !est

SetupSetup

$se the SE.%ES resources

;attern generation and data comparison/=itter analysis at the receiver can be

either on-chip or off-chip

5i h S d S i l i k b k ! ti ( ) ! t5i"h Speed Serial ink oopback !estin" (c) !est

-

8/15/2019 source synchronous intf

37/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "%37

5i"h-Speed Serial-ink oopback !estin" (c)' !est5i"h-Speed Serial-ink oopback !estin" (c)' !est

E7uali8ersE7uali8ers

%"& resources needed9 digital pattern generator D full-swing digital taps for

crosstal+ canceller and one shift-register chain

(o access of %"E output for testing %"E

Suited for production test

Slicer

%"E

#%.

G & a l +

#

a n c e l l e r

""E

%ata

%ata

&G

.G

;attern

*enerator

' $

G

.5;

.5(

#loc+

;attern

4erification

&5(

&5;

;

-

8/15/2019 source synchronous intf

38/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "&38

I$. S%ste&-'ee Interconnect estingI$. S%ste&-'ee Interconnect esting

. t t ! ti ith d S. t t ! ti ith d S

-

8/15/2019 source synchronous intf

39/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . "'39

.nterconnect !estin" 9ith oundary Scan.nterconnect !estin" 9ith oundary Scan

IEEE 114)1 boundary-scan standard developed for testing board-level

manufacture defects

Chip 1

TAP

TCK

TMS

T!

T"

Chip 2

-

8/15/2019 source synchronous intf

40/44

. t t ilt . S l# ! t. t t ilt . S l# ! t

-

8/15/2019 source synchronous intf

41/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 4141

.nterconnect uilt-.n Sel#-!est .nterconnect uilt-.n Sel#-!est

,uilt-in reference and programmable &5 and .5

$se the reference &5 to test .5 %$& or use the reference .5 to test &5 %$&

arious pattern generation support is a +ey for system-level test

-

8/15/2019 source synchronous intf

42/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 4!42

$. #uture *haenges$. #uture *haenges

& t Ch ll&uture Challen"es

-

8/15/2019 source synchronous intf

43/44

EE141System-on-Chip Test Architectures Ch. 14 – High-Speed I/O Interface - . 4"43

&uture Challen"es&uture Challen"es

%ata rate +eeps increasing

in+ =itter margin gets smaller device components and tester have to be

more accurate Eye-will be closed at the .5 input reference &5 and .5 will be mandatory for

testing

!dvanced signaling/e2uali3ations &5 .5 continuous discrete linear

adaptive0

'ore comple5 lin+ system &5 and .5 subsystems means more comple5 testre2uirements

"emto second fs0 accuracy is coming for 17 *bps and higher

&est solution should be optimi3ed for accuracy throughput parallelism fault

coverage and cost re2uirements somewhat conflicting0 for both on-chip

%"&/,IS& and off-chip !&E/instruments

'ore analog %"&/,IS& adaptive design and test with low power

Insuring (, test 2uality from design characteri3ation to high-volume

production with high-confidence and low cost

Concludin" +emarksConcludin" +emarks

-

8/15/2019 source synchronous intf

44/44

44

Concludin" +emarksConcludin" +emarks &hree leading I/O architectures9

• *lobal cloc+ *#0 source synchronous SS0 and embedded

in+ architecture determines the relevant test parameters and

methods) ey parameters include9• %ata valid to cloc+/strobe setup/hold times for *# and SS> =itter noise and

,E. (,0 for embedded

• #loc+ recovery and e2uali3ation must be included in test %"E-assisted test methods9

•

argely rely on loopbac+9 !# loopbac+ under-sampling loopbac+ ande2uali3er testing System-level test methods9

• ,oundary scan for testing manufacturing defects

• ,IS& for testing &5 and .5 and lin+ system "uture challenges9

• Higher data rate smaller =itter margin higher channel counter betteraccuracy

• 'ore comple5 test re2uirements and platform more %"&/,IS& to address

cost and avoid tester-%$& interface bandwidth bottlenec+