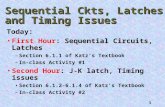

Sequential ckts

Transcript of Sequential ckts

-

8/13/2019 Sequential ckts

1/24

1

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Circuits

Combinational Circuits

Outputs depend on the current inputs

Sequential Circuits

Outputs depend on current and previous inputs

Requires separating previous, current and future

Calledstatesortokens

Example: Finite State Machines (FSMs), Pipelines

CL

clk

in out

clk clk clk

CL CL

PipelineFinite State Machine

-

8/13/2019 Sequential ckts

2/24

2

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Circuits

If tokens moved through pipeline at constant speed, no sequencing elements will be needed

Ex: Fibre-optic cable, called wave pipeliningin circuits

However, dispersion is high in most circuits

We need to delay fast tokens, so that they don't catch up with slow tokens

Use flip-flops to delay fast tokens so that they move through exactly one stage per cycle

Inevitably adds some delay to slow tokens

Makes circuit slower than just the logic delay

Called sequencing overhead

Sometimes called clocking overhead

But it applies to asynchronous circuits too

Inevitable side effect of maintaining sequence

-

8/13/2019 Sequential ckts

3/24

3

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements

Latch

Level sensitive

Transparent latch

D latch

Flip-Flop

Edge triggered

Master-slave flip-flop

D flip-flop, D register

DFlop

Latch

Q

clk clk

D Q

clk

D

Q (latch)

Q (flop)

-

8/13/2019 Sequential ckts

4/24

4

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements: Latch

Pass Transistor Latch

Pros:

Tiny

Low clock loads

Cons:

Vtdrop

nonrestoringbackdriving

output noise sensitivity

dynamic

diffusion input

D Q

-

8/13/2019 Sequential ckts

5/24

5

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements: Latch

Transmission Gate Latch

No Vtdrop

Requires inverted clock

Inverting Buffer

Pros:

Restoring

No backdriving

Fixes either:output noise sensitivity

Or diffusion input

Cons:

Inverted output

D Q

D

XQ

D Q

-

8/13/2019 Sequential ckts

6/24

6

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements: Latch

Tristate feedback

Static

Backdriving risk

Static latches are now essential

Buffered Input

Fixes diffusion input

Noninverting

QDX

QDX

-

8/13/2019 Sequential ckts

7/24

7

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements: Latch

Buffered Output

Non backdriving

Widely used in standard cells

Very robust (important feature)Rather large

Rather slow (1.5 - 2 FO4 delays)

High clock loading

Datapath Latch

Smaller, faster

Unbuffered input

Q

DX

Q

DX

-

8/13/2019 Sequential ckts

8/24

8

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements: Flip-Flop

Flip-Flop

Built as a pair of back-to-back latches

D Q

X

D

X

Q

Q

-

8/13/2019 Sequential ckts

9/24

9

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements

Enable

Ignore clock when enable is inactive

Mux: increase latch D-Q delay

Clock-gating: increase enable setup time, skew

D Q

Latc

h

D Q

en

en

Latc

hD

Q

0

1

en

Latc

h

D Q

en

DQ

0

1

enD Q

en

Flop

Flop

Flop

Symbol Multiplexer Design Clock Gating Design

-

8/13/2019 Sequential ckts

10/24

10

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements

Reset

Force output low when reset is asserted

Synchronous vs. asynchronous

D

Q

Q

reset

D

Q

D

reset

Q

D

reset

reset

reset

SynchronousReset

AsynchronousReset

Symbol F

lop

D QLatch

D Q

reset reset

Q

reset

-

8/13/2019 Sequential ckts

11/24

11

Principles of VLSI Design CMPE 413Sequential Circuits

Sequential Elements

Set / Reset

Set forces output high when asserted

Flip-Flop with asynchronous set and reset

D

Q

reset

set

reset

set

-

8/13/2019 Sequential ckts

12/24

12

Principles of VLSI Design CMPE 413Sequential Circuits

Timing Diagrams

Flop

A

Y

tpd

Combinational

LogicA Y

D Q

clk clk

D

Q

Latc

h

D Q

clkclk

D

Q

tcd

tsetup t

hold

tccq

tpcq

tccq

tsetup

thold

tpcq

tpdqtcdq

Latch/Flop Hold Timethold

Latch/Flop Setup Timetsetup

Latch D-Q Cont. Delaytpcq

Latch D-Q Prop Delaytpdq

Latch/Flop Clk-Q Cont. Delaytccq

Latch/Flop Clk-Q Prop Delaytpcq

Logic Cont. Delaytcd

Logic Prop. Delaytpd

Latch/Flop Hold Timethold

Latch/Flop Setup Timetsetup

Latch D-Q Cont. Delaytpcq

Latch D-Q Prop Delaytpdq

Latch/Flop Clk-Q Cont. Delaytccq

Latch/Flop Clk-Q Prop Delaytpcq

Logic Cont. Delaytcd

Logic Prop. Delaytpd

Contamination

propogation delaysand

-

8/13/2019 Sequential ckts

13/24

13

Principles of VLSI Design CMPE 413Sequential Circuits

Sequencing Methods

Flip-Flops

2-Phase latches

Pulsed latches

Flip-Flops

F

lop

Latch

F

lop

clk

1

2

p

clk clk

Latch

Latch

p

p

1

1

2

2-PhaseTrans

parentLatches

P

ulsedLatches

Combinational Logic

Combinational

Logic

Combinational

Logic

Combinational LogicLatch

Latch

Tc

Tc/2

tnonoverlap

tnonoverlap

tpw

Half-Cycle 1 Half-Cycle 1

-

8/13/2019 Sequential ckts

14/24

14

Principles of VLSI Design CMPE 413Sequential Circuits

Max-Delay: Flip-Flops

F1

F2

clk

clk clk

Combinational Logic

Tc

Q1 D2

Q1

D2

tpd

tsetup

tpcq

TC

tpcq

tpd

tsetup

+ +=

tpd

TC

tsetup

tpcq

+( )

sequencing delay

-

8/13/2019 Sequential ckts

15/24

-

8/13/2019 Sequential ckts

16/24

16

Principles of VLSI Design CMPE 413Sequential Circuits

Max-Delay: Pulsed Latches

Tc

Q1 Q2D1 D2

Q1

D2

D1

p

p

p

Combinational LogicL1

L2

tpw

(a) tpw

> tsetup

Q1

D2

(b) tpw

< tsetup

Tc

tpd

tpdq

tpcq

tpd

tsetup

TC max tpdq tpdtpcq tpd tsetup tpw+ +,+( )

tpd

TC

max tpdq

tpcq

tsetup

tpw

+,( )

sequencing delay

-

8/13/2019 Sequential ckts

17/24

17

Principles of VLSI Design CMPE 413Sequential Circuits

Min-Delay: Flip-Flops

CL

clk

Q1

D2

F1

clk

Q1

F2

clk

D2

tcd

thold

tccq

tcd

thold

tccq

-

8/13/2019 Sequential ckts

18/24

18

Principles of VLSI Design CMPE 413Sequential Circuits

Min-Delay: 2 Phase Latches

CL

Q1

D2

D2

Q1

1

L1

2

L2

1

2

tnonoverlap

tcd

thold

tccq

tcd1

tcd2

, thold

tccq

tnonoverlap

Hold time reduced by nonoverlap

Paradox: Hold applies twice each cycle

vs. only once for flops

But flops have two latches !!!

-

8/13/2019 Sequential ckts

19/24

19

Principles of VLSI Design CMPE 413Sequential Circuits

Min-Delay: Pulsed Latches

CL

Q1

D2

Q1

D2

p t

pw

p

L1

p

L2

tcd

thold

tccq

tcd

thold

tccq

tpw

+Hold time increased by pulse width

-

8/13/2019 Sequential ckts

20/24

20

Principles of VLSI Design CMPE 413Sequential Circuits

Time Borrowing

In a flip-flop based system

Data launches on one rising/falling edge

Must setup before next rising/falling edge

If it arrives late, system failsIf it arrives early, time is wasted

Flops have hard edges

In a latch-based system

Data can pass through latch when transperent

Long cycle of logic can borrow time into the next cycle

As long as each loop completes in one cycle

This mechanism is calledtime borrowing

-

8/13/2019 Sequential ckts

21/24

21

Principles of VLSI Design CMPE 413Sequential Circuits

Time Borrowing

Latch

Latch

Latch

Combinational LogicCombinational

Logic

Borrowing time across

half-cycle boundary

Borrowing time across

pipeline stage boundary

(a)

(b)Latch

Latch

Combinational LogicCombinational

Logic

Loops may borrow time internally but must complete within the cycle

1

2

1 1

1

2

2

-

8/13/2019 Sequential ckts

22/24

22

Principles of VLSI Design CMPE 413Sequential Circuits

Time Borrowing

Q1L1

1

2

L2

1 2

Combinational Logic 1Q2D1 D2

D2

Tc

Tc/2

Nominal Half-Cycle 1 Delay

tborrow

tnonoverlap

tsetup

How much borrowing?

2 phased latches:

pulsed latches:

tborrow

TC

2------- t

setup t

nonoverlap+( )

tborrow

tpw

tsetup

-

8/13/2019 Sequential ckts

23/24

23

Principles of VLSI Design CMPE 413Sequential Circuits

Clock Skew

F1

F2

clk

clk clk

Combinational Logic

Tc

Q1 D2

Q1

D2

tskew

CL

Q1

D2

F1

clk

Q1

F2

clk

D2

clk

tskew

tsetup

tpcq

tpdq

tcd

thold

tccq

We have assumed zero clock skew

Clock really have uncertainty in arrival time

decrease max-delay

increases min-delay

decreases time borrowing

Clock Skew: Flip-flops

tpd

TC

tpcq

tsetup

tskew

( )

tcd thold tccq tskew+

-

8/13/2019 Sequential ckts

24/24

24

Principles of VLSI Design CMPE 413Sequential Circuits

Clock Skew: Latches

Q1L1

1

2

L2

L3

1 12

Combinational

Logic 1

Combinational

Logic 2

Q2 Q3D1 D2 D3

2 phased latches

tcd1

tcd2

, thold

tccq

tnonoverlap

tskew

+

tpd

Tc

2tpdq

( )

tborrow

TC

2------- t

setup t

nonoverlap t

skew+ +( )

pulsed latches

t

pd

T

C

max t

pdq

t

pcq

t

setup

t

pw

+, t

skew

+( )

tcd

thold

tccq

tpw

tskew

+ +

tborrow

tpw

tsetup

tskew

+( )

![Eee-III-Analog Electronic Ckts [10es32]-Notes](https://static.fdocuments.in/doc/165x107/577cd5561a28ab9e789a820d/eee-iii-analog-electronic-ckts-10es32-notes.jpg)