Real-time phase-locked loops

Transcript of Real-time phase-locked loops

-

8/19/2019 Real-time phase-locked loops

1/48

2006:284 CIV

M A S T E R ' S T H E S I S

Real Time PhaseLocked Loops

Hans Eklund

Luleå University of Technology

MSc Programmes in Engineering

Electrical EngineeringDepartment of Computer Science and Electrical Engineering

Division of Signal Processing

2006:284 CIV - ISSN: 1402-1617 - ISRN: LTU-EX--06/284--SE

-

8/19/2019 Real-time phase-locked loops

2/48

Real Time Phased Locked Loops

HANS EKLUND

Department of Computer Science and Electrical Engineering

Lulea University of Technology

September 2004 to March 2005

mailto:@student.luth.se

-

8/19/2019 Real-time phase-locked loops

3/48

-

8/19/2019 Real-time phase-locked loops

4/48

Abstract

This report covers a master thesis in signal processing. It deals with solving aproblem in a special type of audio encoder used in the Swedish speech newspapersystem. However, design methods and algorithms developed or investigated arerather general. A large part of the report covers the fundamental theory of phase locked loops and can be regarded as a beginners introduction to the field.Along the way, the theory aims at a software implementation, and thereforetries to deal with such specific matters. Also the issues with implementing atime critical system in digital hardware is outlined and a custom method forachieving phase-lock is presented. A successful implementation was made on adigital signal processor based hardware platform.

-

8/19/2019 Real-time phase-locked loops

5/48

-

8/19/2019 Real-time phase-locked loops

6/48

Contents

1 Introduction 1

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.2 The audio encoder . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.3 Ob jectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21.4 Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 Phase locked loops 5

2.1 Building blocks of the LPLL . . . . . . . . . . . . . . . . . . . . . 62.2 Phase signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72.3 A linear model . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.3.1 Phase detector . . . . . . . . . . . . . . . . . . . . . . . . 92.3.2 Voltage controlled oscillator . . . . . . . . . . . . . . . . . 102.3.3 Divide by N circuit . . . . . . . . . . . . . . . . . . . . . . 112.3.4 The loop filter . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3.5 The final linear model . . . . . . . . . . . . . . . . . . . . 162.4 Non linear properties . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.4.1 Unlocked behavior . . . . . . . . . . . . . . . . . . . . . . 192.4.2 Design criterion from a non-linear point of view . . . . . . 21

2.5 The Software Phase Locked Loop . . . . . . . . . . . . . . . . . . 222.5.1 Discretizing the LPLL . . . . . . . . . . . . . . . . . . . . 222.5.2 Hardware specific issues . . . . . . . . . . . . . . . . . . . 24

3 Results 29

3.1 Matlab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293.2 Real-time hardware implementation . . . . . . . . . . . . . . . . 30

3.2.1 Hardware specification . . . . . . . . . . . . . . . . . . . . 303.2.2 Developing environment . . . . . . . . . . . . . . . . . . . 303.2.3 Measurements . . . . . . . . . . . . . . . . . . . . . . . . 32

4 Conclusion 35

A Program code 36

iii

-

8/19/2019 Real-time phase-locked loops

7/48

iv

-

8/19/2019 Real-time phase-locked loops

8/48

List of Figures

1.1 Functional description of the coder. . . . . . . . . . . . . . . . . . 2

1.2 Spectral contents of baseband FM-radio, the MPX signal. . . . . 2

1.3 Scrambling audio by Vestigial sideband modulation. . . . . . . . 3

2.1 Complex representation of two signals. The arrows move aroundsince their phase (angle) is a function of time. The speed of therotation is the frequency of the sinusoids. . . . . . . . . . . . . . 5

2.2 Block diagram of a linear PLL. . . . . . . . . . . . . . . . . . . . 6

2.3 A few signals applied to a PLL. Observe the relationship betweenfrequency and phase signals. (a) Frequency step. (b) Frequencyramp. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.4 A simple control system with a regulator, process and feedback. . 9

2.5 Bode diagram of the filter types mentioned. (top) Passive lagfilter. (mid) Active lag filter with K a = 10. (bottom) PI-filter,

observe the high gain near DC. . . . . . . . . . . . . . . . . . . . 142.6 Linear model of the PLL. . . . . . . . . . . . . . . . . . . . . . . 14

2.7 Step response of the LPLL error function for various dampingfactors ζ when system is set to follow at half the frequency of theinput. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.8 Amplitude response of the LPLL for various damping factors, ζ ,plotted against normalized frequency ω/ωn . . . . . . . . . . . . 18

2.9 The various ranges of interest for a linear PLL. . . . . . . . . . . 20

2.10 The pull-in process for a LPLL implemented in software. it fi-nally settled at 21 × π = 65.97 radians out of phase. . . . . . . . 21

2.11 Analog PI filter and its digital counterpart created using the

bilinear transform. . . . . . . . . . . . . . . . . . . . . . . . . . . 232.12 An SPLL with secondary oscillator controlled by a phase ad-

justing subsystem. The dashed line is the adjustments made atspecific times decided by the parameter decision block, and notat system sampling instances. . . . . . . . . . . . . . . . . . . . . 26

2.13 Improvement in signal quality due to a slower loop filter switchedin when system is locked in frequency. . . . . . . . . . . . . . . . 28

3.1 The signals of importance in a discrete linear PLL. It is lockedto a noisy input of 4.1 kHz. . . . . . . . . . . . . . . . . . . . . . 31

3.2 Spectrogram of input and output to the SPLL implemented on

a DSP. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

v

-

8/19/2019 Real-time phase-locked loops

9/48

3.3 Oscilloscope dump of the SPLL input at 19 kHz and the in phaselocked half frequency output. . . . . . . . . . . . . . . . . . . . . 34

3.4 Oscilloscope dump of the FFT of the SPLL output. 10dBV pers q u a r e . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

vi

-

8/19/2019 Real-time phase-locked loops

10/48

Acknowledgement

Thanks goes to the Rubico AB founders Anders and Per for havingme as their Master Thesis student and for their support in everyaspect. Thanks to James Leblanc for valuable insights and patiencein this long drama. Also, hats off for Robert Selberg for actingas the thesis opponent. Thanks to the percolator for keeping thecoffee warm and aromatic. Finally, thanks to all the staff, currentand past, at Rubico for being around for support and laughter.

Hans Eklund, September 2006.

vii

-

8/19/2019 Real-time phase-locked loops

11/48

viii

-

8/19/2019 Real-time phase-locked loops

12/48

Chapter 1

Introduction

Engineering is all about development. This master thesis uses new technologyto improve an old system. In this case the new technology are digital signalprocessors - DSP. The system in need of improvement is the Swedish speechnewspaper distribution system.

1.1 Overview

The speech newspaper system has been available since mid nineteen eightiesand makes newspapers available to the visually impaired. Newspaper staff readand record the written articles, advertisements, radio and TV tableaus etc. The

speech newspapers are distributed by mail on a tape, or via an ordinary FMnetwork, taking advantage of unused channel capacity during night.

The technique used in several parts of the current system were developedduring that time. One part sits in between the recording studio and the FMlink. That part scrambles the speech in a certain way to ensure only subscribersof the speech newspaper can listen to it. Currently, the scrambling is performedby analog electronics that has to be tuned once a year. It has now been proposedthat the old audio encoder may be replaced by a more flexible digital system.Using a digital method to scramble the audio is attractive in several aspects.First and foremost, the aspect of quality. Using the old analog equipmentrequires regular service and tuning of parameters. With a digital platform the

way the audio gets encoded does not change with time. Second, the new coderplatform is flexible and will be easy to upgrade for future demands.

1.2 The audio encoder

The audio encoder consists of a few interconnected filters and a modulationmethod as shown in Fig. 1.1. First, the audio is band limited by a sharp band-pass filter. The filter cancels frequencies below 40 Hz and above 6.3 kHz. Thesignal can now be modulated onto a 9.5 kHz carrier and then low pass filteredto suppress the upper sideband, this scheme of modulation is called Vestigial

Sideband (VSB) modulation. VSB modulation is basically a compromise be-tween Single Sideband (SSB) and Dual Sideband (DSB) modulation. All three

-

8/19/2019 Real-time phase-locked loops

13/48

2

are common in analog communications theory, see [1] for details. The effectis that the frequency contents will be reversed if not decoded correctly, highpitch sound will become low and vice versa, as seen in Fig. 1.3. Before sendingthe modulated audio to the external FM network, a disturbing 1 KHz tone isadded to further decrease the hearability. At the heart of the scrambling al-

40 Hz - 7 kHzbandpass

PLL 1 kHz

tone

Audioinput

MPXinput

Lowpassfilter

VSB Modulation

Encodedoutput

9.5 kHztone

Figure 1.1: Functional description of the coder.

gorithm is the VSB modulation that shifts the spectrum, as described earlier.The audio has to be modulated upon a signal at half the frequency of a 19 KHztone available in the so called MPX signal. The MPX signal is the basebandinformation signal in the FM system with spectral contents roughly as seen in

Fig. 1.2. How do we generate a signal, locked in phase, at exactly half thefrequency? And what method is suitable for a software implementation?

P i l

o t

c a r r

i e r

RDSDSB-SCAudio (Mono)

L- R (lower sideband)

L-R (upper sideband)

0 15 19 23 38 53 57 f in kHz

L+R

Figure 1.2: Spectral contents of baseband FM-radio, the MPX signal.

1.3 Objectives

The coding method in the system is obsolete in many ways. The coding isperformed in a way that is really sub par when it comes to security, but forthe application it works. If the system would be replaced by an entirely digital

one, the coding method would be of another kind. However since the coder hasto be backward compatible with old receivers, the new coder has to be able to

-

8/19/2019 Real-time phase-locked loops

14/48

1.3 Objectives 3

−1 −0.8 −0.6 −0.4 −0.2 0 0.2 0.4 0.6 0.8 1

x 104

−20

0

20

40Baseband information signal after 40−7KHz bandpass.

−2 −1.5 −1 −0.5 0 0.5 1 1.5 2

x 104

−20

0

20

40Spectrum of signal after modulation upon 9.5Khz carrier.

M a g n i t u d e [ d B ]

−2 −1.5 −1 −0.5 0 0.5 1 1.5 2

x 104

−20

0

20

40Spectrum of signal after VSB filter.

Frequency[Hz]

Figure 1.3: Scrambling audio by Vestigial sideband modulation.

implement the analog scrambling described above. Most of the blocks in thecoder are more or less trivial to implement, such as filters and the modulation.

As hinted above, the block that needs extra attention is the synchronizationblock used to synthesize the 9.5 kHz signal before the VSB modulation scheme.

The company that wanted this thesis to be made initially had experience,equipment and software already available for a specific platform. So the solutionhad to be tailored for that particular target. Therefore, the main objective of the thesis was to investigate the possibility of implementing the synchronizationblock in a DSP for a real time application.

The specifications on what to be accomplished where quite clear though.The audio input was to be modulated onto a carrier at exactly half the frequencyof the 19 kHz MPX-signal and at a specific phase shift. Early on a possible

solution to the problem was seen. It was concluded that a phase locked loopmight do the job, if properly designed. However, the field of phase-locked loops

-

8/19/2019 Real-time phase-locked loops

15/48

4

is deep and somewhat intricate. A thorough study on the subject was made tolay the foundation to the design.

1.4 Outline

The report is structured into two main blocks. An introduction and designguide to phase locked loops with en emphasis on software implementation comesfirst. The chapter after is shorter and provide a presentation of a workingimplementation of the theory. Last of all the results are discussed and furtherwork are suggested.

-

8/19/2019 Real-time phase-locked loops

16/48

Chapter 2

Phase locked loops

A Phase-locked loop is a device that makes one system track another. It syn-chronizes an output signal with a reference in frequency and in phase. Hereone system is the pilot tone from the MPX-signal and the other is our own syn-thesized signal. Both are periodic functions of time, sinusoids or square waves.However, instead of viewing the two signals as functions of time, think of themas phasors in the complex plane. As complex phasors, the two signals are twovectors rotating around the plane. Fig. 2.1 demonstrates the concept. The

Im{z }n

Re{z }n

z = e1

j( t)

z = e2 j( t)

Figure 2.1: Complex representation of two signals. The arrows move around since theirphase (angle) is a function of time. The speed of the rotation is the frequencyof the sinusoids.

phase at any instant is a function of time, in general

θn(t) =

t−∞

ωn(t)dt.

The phase is the property of interest for the PLL designer. As an example,

assume the first vector is rotating at constant angular frequency ω1(t) = ωc. Tomake the new, generated signal follow the input signal, the new one has to adjust

-

8/19/2019 Real-time phase-locked loops

17/48

6 Phase locked loops

its phase to minimize the distance to the reference, that is the phase error ,denoted as θe. Adjusting its phase is done by either increasing or decreasing itsangular frequency. When both vectors are moving about at the same rate wesay they are locked to each other. In the locked state the phase error betweenthe two systems are zero or constant, depending on the system design. If thereference signal deviates from its current angular frequency and a phase errordevelops, a control system acts upon the second system to make the phase errorsmaller. The control system locks the phase of the output to the input, hencethe name - Phase locked loop.

Phase locked loops are used mainly in two fields of application. Whenanalog signals are modulating a high-frequency carrier the PLL is needed todemodulate the received signal back to the baseband. Classical modulationschemes include amplitude modulation (AM), frequency modulation (FM) andphase modulation (PM). An important application was found in 1950, the colorsubcarrier in television systems was recovered with the use of a PLL.

The other important application is in the field of frequency synthesis, that iscreating a signal with correct and stable frequency. The synthesis applicationis commonly found in the sending part of communication systems where thecarrier is created for bandpass signaling. By synthesis we mean that a signalfrom an oscillator is fed to the PLL and the output is a signal with anotherfrequency.

In this thesis, the application is frequency synthesis and the PLL describedbelow is designed for that purpose. It does not differ much from the PLL used in

receivers, the main difference is a parameter used to set a multiplication/divisionratio of the input frequency.

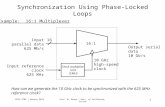

2.1 Building blocks of the LPLL

Lets have a closer look at the first class of PLLs - Linear PLLs (LPLL). Thereare other types of PLLs, digital PLLs (DPLL) and All-digital PLLs (ADPLL).All of which can be implemented as the last class - the Software PLL (SPLL)- a phase locked loop that is running on a processor controlled by a suitableprogram. Linear PLLs consists mainly of four components as seen in Fig. 2.2.First the phase of the generated signal and the phase of the reference input

Loopfilter

VCO

uin(t)

Frequencydivider

u (t)outPhasedetector

ufb(t)

Figure 2.2: Block diagram of a linear PLL.

-

8/19/2019 Real-time phase-locked loops

18/48

2.2 Phase signals 7

has to be compared somehow. One way of achieving that is to do a simplemultiplication and a subsequent filtering operation done by the loop filter, whichis the second component of the LPLL. The filter poles and zeros has to be chosencarefully to make the PLL act as desired. The filtered phase signal is then fed toa voltage controlled oscillator (VCO). The VCO is an oscillator working arounda quiescent frequency. The deviation from that frequency is determined by thecontrol-signal fed to it. The last block is the frequency divider, it divides (ormultiplies) the frequency that is fed back to the phase detector. It is oftencalled ’divide by N circuit’.

To make a PLL cope with design specifications, care has to be taken whenchoosing the three components. When implementing a LPLL using analogcomponents, the designer is most often left with pre manufactured mixers andVCO. In that case the filter becomes the main design issue. Assuming that,lets have a look at a model of the LPLL. Despite its name, the Linear PLL isnot as linear as one may think. However, a linear model can be made as a firstapproximation. But before delving into a linear model we must make a fewthings clear.

2.2 Phase signals

As pointed out by Best [2], phase signals are a source of much trouble whenunderstanding phase locked loops. For the PLL designer a signal such as

A1 sin(ω1t + θ1(t)) (2.1)

carries its information, not in the amplitude A1, not in its frequency ω1, butin the phase θ1(t). To clarify what happens in phase when the frequency ischanged in a certain way, a few examples might help. Assume that the frequencyis constant, ω0 for t

-

8/19/2019 Real-time phase-locked loops

19/48

8 Phase locked loops

−1 0 1−1

0

1

A m p l i t u d e

(a) − Frequency step

−1 0 10

0.01

0.02

r a d / s

Frequency of signal

−1 0 1−50

0

50

r a d

time

Phase of signal

−1 0 1−1

0

1

(b) − Frequency ramp

−1 0 10

0.1

0.2Frequency of signal

−1 0 1−200

0

200

Phase of signal

time

Figure 2.3: A few signals applied to a PLL. Observe the relationship between frequency andphase signals. (a) Frequency step. (b) Frequency ramp.

2.3 A linear model

Considering input and the output of the PLL are phase signals, we can do thesystem analysis using the transfer function H(s). Hence, we consider the systemlinear with respect to phase relationships. We also assume that the LPLL islocked and remains so in the near future. The Laplace transforms of the inputand output phase functions, θin(t) and θout(t) respectively, defines the transferfunction

H (s) = Θout(s)

Θin(s) . (2.4)

The function H(s) is now a phase transfer function, and the model is only validfor small changes in phase of the reference, if the phase error becomes too bigtoo fast, the LPLL will unlock and a non-linear process takes place. Althoughthat process is described by a cumbersome non-linear differential equation itcan be understood on an intuitive level.

To express H(s) we must know the transfer functions of the three buildingblocks of the LPLL, as seen in Fig. 2.2. As stated earlier, a PLL is nothing buta control system for phase signals, therefore we can rely on basic control theorywhen explaining the linear model. A control system with a regulator in series

with a process has a well known transfer function when the process output isfed back and subtracted from the system input as in Fig. 2.4.

-

8/19/2019 Real-time phase-locked loops

20/48

2.3 A linear model 9

Regulator

G(s)r

Process

G (s) p+

-

u (t)in e(t)

G (s)g

Feedback system

u (t)out

u (t)fb

Figure 2.4: A simple control system with a regulator, process and feedback.

Let the regulator have the transfer function Gr(s) and the process in needof regulation have the transfer function G p(s). The system transfer function isthen described by

H (s) = Gr(s)G p(s)

1 + Gr(s)G p(s)Gg(s). (2.5)

Such a relationship is derived by any basic text on control theory, such as [3]. Inthe PLL case the regulator is the loop filter and the process in need of regulationis the VCO.

2.3.1 Phase detectorReviewing Fig. 2.2, and as earlier stated the input to the LPLL is usually asine wave,

uin(t) = U in sin(ωint + θin).

The signal generated by the VCO, fed back through the divider is anothersinusoid,

ufb(t) = U fb sin(ωfbt + θfb).

The phase difference between the two signals are obtained by multiplying thetwo signals and then filtering the result. That is the sole operation of the phasedetector. The behavior has to be modeled in a linear fashion. Assuming thePLL is close to locked or locked in frequency, we have ω = ωin = ωfb and theoperation becomes

ud(t) = U in sin(ωt + θin)U fb sin(ωt + θfb) (2.6)

By trigonometric simplification using the relation

sin(α)sin(β ) = 1

2(cos(α − β ) − cos(α + β )),

the output of the phase detector becomes

ud(t) = U inU fb

2 (cos(θin − θfb) − cos(2ωt + θin + θfb)). (2.7)

-

8/19/2019 Real-time phase-locked loops

21/48

10 Phase locked loops

The first term is the wanted ”dc” component. The higher order componentcos(2ωt + θin + θfb) will be canceled by the subsequent filter, hence they can beneglected in the linear model. The output can then be simplified to

ud(t) = K d cos(θe) (2.8)

Where K d = U inU fb/2 and θe = θin − θfb. This is a non-linear relation. Zerophase error should correspond to zero output of the detector. Likewise, smallerrors in phase should correspond to small outputs from the detector. A solutionto this is obtained by making uin(t) and ufb(t) π/2 radians out of phase, that is,replacing ufb(t) for example with a cosine function. The trigonometric relation

sin(α)cos(β ) = 1

2

(sin(α − β ) + sin(α + β ))

explains the operation. In place of Eq. 2.35, the input/output relationship of the phase detector will be

ud(t) = U inU fb

2 (sin(θin − θfb) + sin(2ωt + θin + θfb)). (2.9)

Again neglecting the higher order component, the simplified input/ouput rela-tionship becomes

ud(t) = K d sin(θe). (2.10)

And for small errors in phase, the assumption

ud(t) ≈ K dθe (2.11)

is valid. The LPLL simulated in Chapter 3 below behaves as predicted by theabove theory; the feedback ufb(t) is always π radians out of phase with theinput uin(t) when the phase error θe is close to zero.

Concluding the phase detector discussion, the linearized model is just a zero-order block having gain K d = U inU fb/2. Remark: the loop filter is actually apart of the phase detector in the linear model since it cancels the higher ordercomponents. We will deal with the filter properties right after the derivation of the VCO model.

2.3.2 Voltage controlled oscillator

The VCO generates a square or sinusoidal signal, which frequency depends onthe input signal level. It operates around a quiescent frequency ωc, preferablyclose to the signal that we want to lock on. If the VCO output u(out), issinusoidal it depends on the input uf (filter output, not to be confused withthe feedback signal, ufb) in the following way:

uout = cos((ωc + K ouf (t))t). (2.12)

The parameter K o is called VCO gain, and is specific to the selected VCO. It

has to be considered when designing PLLs in hardware when the VCO is notdesigned from scratch, but chosen suitably. K 0 has the dimension rad s−1V −1.

-

8/19/2019 Real-time phase-locked loops

22/48

2.3 A linear model 11

When designing the PLL in software it can be arbitrarily chosen since the filterdesign will accommodate for it. More on determining constants in section 2.3.5.However, what we need is the transfer function of the VCO. As seen in Eq. 2.12the angular frequency of the VCO is

ωout(t) = ωc + K ouf (t)

But we do not want to express the VCO frequency, we want the phase transferfunction. Therefore, by definition, the phase θout(t) is given by integration of the frequency variation K 0uf (t).

θout =

K 0uf dt = K 0

uf dt

The laplace transform for integration over time is 1/s. The laplace transformfor the output phase θout is then

Θout(s) = K 0

s U f (s) (2.13)

The transfer function of the VCO is then simply

Θout(s)

U f (s) =

K 0s

(2.14)

Therefore the VCO is nothing but an integrator for phase.

2.3.3 Divide by N circuit

The classical linear PLL used for frequency synthesis is suppose to generate aperiodic signal of frequency

ωout(t) = N

M ωin(t). (2.15)

Where N and M are integers. Analog linear PLL implements the integer divi-sion in frequency by counting and triggering on every N pulses, and there bygenerating a square wave at N times lower frequency. That is not a problemsince the fundamental component of the square wave is the one that locks to thereference input, remembering that the loop filter cancels the higher componentsin the square wave as well. A divider before the PLL input makes the signalhave M times lower frequency in the same way. Selecting the divide ratios Nand M suitably, any division ratio can be obtained.

In this thesis another method is used since the PLL is implemented insoftware. With that method the M-divider can be discarded since N can be afractional number. When locked, ωfb = ωin, therefore

ωout(t) = N ωfb(t). (2.16)

The relationship described by Eq. 2.16 has to be modeled for the phase signalsin the linear model. The relationship is simple, but the derivation is done forthe sake of completeness. From

θ(t) =

ω(t) dt,

-

8/19/2019 Real-time phase-locked loops

23/48

12 Phase locked loops

and integrating both sides of Eq. 2.16

θout(t) = N θfb(t)

The transfer function for the N-divider is then

θfb(t)

θout(t) =

1

N = K n (2.17)

Acting upon the phase signal in the feedback is simply a gain factor K n.

2.3.4 The loop filter

So far we have assumed that a filter exists in the LPLL to cancel higher order

components so the wanted dc term, the phase error, can be used to control theVCO. However the loop filter has another function. Viewing the LPLL as acontrol system for phase signals, the loop filter is the regulator. Bertil Thomas[4] mentions that in control theory the regulator mainly has two tasks. One isto compensate for disturbances that affects the system. The other is to takenecessary actions when the desired value is changed. In the PLL case, thedesired value is the current phase of the input signal. When determining howwell a regulator can cope with the two tasks several properties can be studied.Properties such as static accuracy, speed and stability.

As this paper deals with the design of an audio coder and its clear specifi-cations, the discussion will be taken to solve that problem and not the general

one since it is beyond the scope of this thesis.

Closed loop performance demands

The choice of the loop filter is critical to the system performance. Beginningwith the specifications of the coder a few hard demands has to be met. Thecoder has to modulate the audio input onto a carrier operating at exactly half the frequency of the FM pilot tone. The divide by N-circuit described abovemake that behavior possible.

Static accuracy Since we can only tolerate a small phase difference or driftbetween the pilot tone input and the half frequency output we have defined thedemand of static accuracy: zero remaining error when the input is changed.It has to be asymptotically zero independently how the input is changed. Theregulator has to cope with whatever action is done at the input.

Speed Another important property of a control system is the speed. Whenthe desired value is changed in some manner, it takes some time for the outputof the system to change and finally settle at the new value. Several measuresof speed exists and one common is the rise time . The rise time is definedas the time it takes for the output to go from 10% to 90% of its final value.Remembering that we are dealing with a linearized model of an actual system,

other non-linear properties of the LPLL defines the settling speed when thesystem unlocks and has to work towards a locking state. More on such effects

-

8/19/2019 Real-time phase-locked loops

24/48

2.3 A linear model 13

below. Also speed and stability are contradictory demands, higher speed impliessmaller stability margins and vice versa. I let the speed demand be defined as:as fast as possible when stability demands are met . Defining the speed of thesystem comes down to make the closed loop system have a suitable dampingfactor.

Stability This is probably the most important, and therefore the most com-plex part of the entire paper. As hinted above the actual behavior of the LPLLis described by a non linear differential equation. The complete system stabil-ity and how the filter affects it in all situations is not theoretically derived orpredicted by this thesis due to its high complexity. Instead testing and simula-

tions of the system is made to ensure that the system is stable even when in itsnon-linear mode of operation. The linear part of the stability problem however,can be analyzed using the properties of linear systems using the model derivedin this chapter. Stability issues is discussed further below, once the filter typeis selected.

Selecting a filter

The selection of the correct loop filter implies the selection of the type andorder of the filter so the closed loop system type and order can accommodate

the above demands. Type refers to the number of poles in the transfer function,the order is the same as the highest degree of the characteristic equation. Best[2] mentions three basic filter types common in PLL applications, seen in Fig.2.5. Clearly they are all low pass filters with different cutoff frequencies. Thefirst is called passive lag filter . Its transfer function F(s) is given by

F 1(s) = 1 + sτ 1

1 + s(τ 1 + τ 2) (2.18)

The second type has a similar transfer function, but has an additional gain termK a, given by

F 2(s) = K a1 + sτ 21 + sτ 1

(2.19)

The last type of filter suggested is commonly referred to as a ”PI” filter. PIstands for proportional and integrating action, taken from control theory. Itstransfer function is

F 3(s) = 1 + sτ 2

sτ 1(2.20)

But how do we motivate the selection of one and not the other? The criterion

of static accuracy is zero phase error. A filter that fulfills that criterion will bea strong candidate. The phase is defined as Θe = Θin − Θfb, seen in Fig. 2.6.

-

8/19/2019 Real-time phase-locked loops

25/48

14 Phase locked loops

10−3

10−2

10−1

100

101

102

−30

−20

−10

0

M a g n i t u d e ( d B

)

Frequency (rad/sec)

10−3

10−2

10−1

100

101

102

−10

0

10

20

M a g n i t u d e ( d B )

Frequency (rad/sec)

10−3

10−2

10−1

100

101

102

−10

0

10

20

30

40

M a g n

i t u d e ( d B )

Frequency (rad/sec)

Figure 2.5: Bode diagram of the filter types mentioned. (top) Passive lag filter. (mid) Activelag filter with K a = 10. (bottom) PI-filter, observe the high gain near DC.

Phase detecor Loop filter

F(s)

VCO

K 0s _

K d+

-

in(s)

(s)fb

e(s) U (s)d U(s)f

K n

Feedback gain

out(s)

Figure 2.6: Linear model of the PLL.

-

8/19/2019 Real-time phase-locked loops

26/48

2.3 A linear model 15

By looking at the error signal Θe as a system output, we can define a phaseerror transfer function as

E (s) = Θe(s)

Θin(s) =

1

1 + K dF (s)K 0s

K n. (2.21)

Knowing the error transfer function, we can find the error function θe(t) for anygiven input θin(t) since

Θe(s) = Θin(s)E (s), (2.22)

by inverse transformation of Θe(s). But since we want to find the error as timegoes to infinity, the final error, we can take a shortcut by using the final valuetheorem of laplace transforms:

Assume that g is causal and that G = L{g} is rational. If all poles to sG(s)has negative real part, then

limt→+∞

g(t) = lims→+0

sG(s)

It gives us the opportunity to find the error as time goes to infinity withouthaving to transform Θe(s) back to the time domain.

Tracking frequency means that the frequency of the feedback signal ufb(t)has to be adjusted correctly by the VCO if a new frequency suddenly appearsin the reference uin(t). That is, the system senses a frequency step. Now recallthat a frequency step, as in Fig. 2.3, really is a phase ramp for our linear system.Therefore we know what our system has to deal with to follow specifications.

The laplace transform of the a phase ramp input is

Ri(s) = C v

s2 ,

as given by any laplace transform table, or derived by any text on linear systemssuch as [5]. C v is the frequency difference in radians per second at the phasedetector. If a the phase ramp is applied to our error transfer function as in Eq.2.22, we have the Laplace transform of the error as

Θe(s) = Θin(s)E (s) = C v

s21

1 + K dF (s)K 0s

K n=

C vs2 + K dK 0F (s)K ns

(2.23)

Now following the final value theorem we get

limt→+∞

θe(t) = lims→+0

sΘe(s) = lims→+0

s C v

s2 + K dK 0F (s)K ns (2.24)

The final expression is then

limt→+∞

θe(t) = lims→+0

C vs + K dK 0F (s)K n

(2.25)

Any filter transfer function F (s) can now be inserted in Eq. 2.25 to obtain thefinal error when the system is subject to a phase ramp. A generalized filtertransfer function can be expressed as

F (s) = N (s)D(s)sn

. (2.26)

-

8/19/2019 Real-time phase-locked loops

27/48

16 Phase locked loops

Where N (s) and D(s) are the nominator and denominator polynomials respec-tively. in the laplace domain, sn are poles at s = 0. Inserting Eq. 2.26 into Eq.2.25 gives us

θe(∞) = lims→+0

C v

s + K dK 0N (s)D(s)sn K n

= lims→+0

C vD(s)sn

sn+1D(s) + K dK 0K dN (s) (2.27)

Inspection of Eq. 2.27 tells us that if n ≥ 1 the limit will approach zero as timegoes to infinity. We can therefore state that if we want our LPLL to track thereference phase with zero phase error, a filter pole in s = 0 is needed.

For example,the first filter suggested by Best [2]. Inserting Eq. 2.18 into2.25 gives us

limt→+∞ θe(t) = lims→+0

C v

s + K dK 01+sτ 1

1+s(τ 1+τ 2)K n

= C

vK dK 0K n

, (2.28)

by observing that 1+sτ 11+s(τ 1+τ 2) → 1 as s → 0. That filter does not reduce the

error to zero, however it may very well do if the loop gain(K dK 0K n) is kepthigh enough. The second filter, F 2 has a similar transfer function and yields asimilar final error, reduced by the amplification factor K a. The third suggestedfilter, the ”PI filter” of Eq. 2.20 has a pole in s = 0 and should be a candidatecapable of reducing final error to zero. The error is calculated as

limt

→+

∞

θe(t) = lims

→+0

C v

s + K dK 01+sτ 2

sτ 1

K n= 0 (2.29)

by observing that the filter part 1+sτ 2sτ 1

→ ∞ as s → 0. The pole in s = 0provides the filter with, at least theoretically, infinite gain at DC and thereforethe system reduces any remaining phase error to zero eventually.

Concluding the filter discussion, as motivated above the filter type for thisparticular LPLL application will be of the ”PI” type,

F (s) = 1 + sτ 2

sτ 1

What remains in the filter design is selecting the constants τ 1 and τ 2 appropri-ately. This will be done in the next section.

At this point, we have covered the four main blocks of the linear modelof the LPLL. By closing the loop and seeing it as a feedback control system,the final analysis can be made. The filter and amplification constants can beselected to give the system its desired overall characteristics.

2.3.5 The final linear model

Summarizing the blocks covered above, as depicted in Fig. 2.6, the phasetransfer function is

H (s) = Θout(s)

Θin(s) = K dF (s)

K 0

s1 + K nK dF (s)

K 0s

=K d

1+sτ 2

sτ 1

K 0

s1 + K nK d

1+sτ 2sτ 1

K 0s

(2.30)

-

8/19/2019 Real-time phase-locked loops

28/48

2.3 A linear model 17

by remembering the general transfer function for control theory as in Eq. 2.5.When analyzing the closed loop it is convenient to put the transfer function ona special form, the so called normalized form, by making the dominator be

D = s2 + 2ζωns + ω2n

where ωn is the natural frequency and ζ is the damping factor. Simplifying Eq.2.30 further,

H (s) = K dK 0(1 + τ 2s)τ 1s + K dK nK 0(1 + τ 2s) =

K d

K 0

(1+τ 2s)

τ 1

s2 + K dK nK 0τ 2τ 1

s + K dK nK 0τ 1

(2.31)

Then the substitution can be made:

ωn =

K 0K dK n

τ 1ζ =

ωnτ 22

(2.32)

The final phase transfer function can then be written as

H (s) =1K n

(2ωnζs + ω2n)

s2 + 2ωnζs + ω2n(2.33)

Also, the phase error transfer function, Eq. 2.21 can be rewritten in terms of the defined damping factor and natural frequency as

E (s) = 1 − H (s) = 1K ns

2

s2 + 2ωnζs + ω2n(2.34)

From this point, using Eq. 2.33 it is easy to investigate the transient responseof the PLL as we would on any control system. The parameters ωn - the naturalfrequency, and ζ - the damping factors, are key design parameters. Once theyare determined, the filter parameters τ 1 and τ 2 can be obtained and the PLLdesign is complete. A system with a high damping factor is said to be overdamped and the response may become sluggish. If the damping factor is toolow, as in an under damped system, the system may become oscillatory. Settingζ = 1

√ 2 is usually a good tradeoff between speed and stability. We see how the

damping factor ζ affects the step response of the error function in Fig. 2.7.

-

8/19/2019 Real-time phase-locked loops

29/48

18 Phase locked loops

0 0.05 0.1 0.15 0.20

0.2

0.4

0.6

0.8

1

←ζ=0.05

←ζ=0.30

←ζ=0.71←ζ=2.00 θ

e

Time[sec.]

Figure 2.7: Step response of the LPLL error function for various damping factors ζ whensystem is set to follow at half the frequency of the input.

How about criterions for determining a suitable natural frequency? Whendesigning a PLL for frequency synthesis purposes it is vital that the signal

generated is pure. Looking at the amplitude response of the closed loop in Fig.2.8, we could view the PLL as a filter. Recall that the double frequency tone

10−1

100

101

102

−40

−30

−20

−10

0

10

20

←ζ=0.05

←ζ=0.30←ζ=0.71

←ζ=2.00

| E ( j ω ) | ( d B )

ω / ωn

Figure 2.8: Amplitude response of the LPLL for various damping factors, ζ , plotted againstnormalized frequency ω/ωn

generated by the phase detector is nothing but noise for this application. The

-

8/19/2019 Real-time phase-locked loops

30/48

2.4 Non linear properties 19

tone will affect the VCO and make it tremble around its desired frequency.Therefore we may want to narrow down the bandwidth of the system to makethe damping high at that double frequency. This is where the noise criterioncomes into the picture.

A low loop bandwidth will reject high frequency noise fed into, or created inthe system. But how low can it be set? For this particular PLL implementationthe input signal is most likely to be stable and it does not contain any basebandinformation that needs to be preserved. If we were to design an FM receiver wewould have to consider the bandwidth of the baseband signal when determiningthe natural frequency.

Determining a correct natural frequency ωn implies determining some im-portant non linear properties of the LPLL. A brief overview of non linear LPLL

behavior will be covered in the next section and if it has any implications onhow the filter parameters will be calculated.

2.4 Non linear properties

A linear phase-locked loop actually has important non linear properties as wellas linear ones. When the reference frequency and the VCO has different fre-quencies we say that the LPLL is in its unlocked mode and the linear modelderived above is not valid. We will not derive the non linear equation since itis quite intricate.

As Best [2] states, it is not of major concern to know exactly what the LPLLdoes when it is in the unlocked state. He mentions three important questionsthough.

• Under what conditions will the LPLL get locked?

• How much time does the lock-in process need?

• Under what conditions will the LPLL lose lock?

The answers to those questions are not given by theoretical derivation of math-ematical relations, instead experiments was conducted to ensure that the LPLLperformed well enough for the task. However the question of a suitable naturalfrequency of the system still remains to be answered.

2.4.1 Unlocked behavior

The LPLL has four important stability regions. The regions are defined ascertain deviations in frequency from the quiescent frequency of the VCO and

how fast the reference frequency changes, as seen in Fig. 2.9. The followingdefinitions are taken from [2], with additional comments:

-

8/19/2019 Real-time phase-locked loops

31/48

20 Phase locked loops

L

PO

P

H

Lock range

Pull-out range

Pull-in range

Hold range

Figure 2.9: The various ranges of interest for a linear PLL.

1. The hold range ∆ωH . This is the range where the PLL can staticallymaintain phase tracking. That is, if the reference frequency deviates thisfar from the designed quiescent frequency the LPLL will unlock and thephase error will go to infinity. This is independently of the speed the

frequency was changed.

2. The pull-in range ∆ωP . This is the range within which an LPLL willalways become locked if unlocked. This range can be infinite if the correctfilter is used. The pull-in process is slow and will be explained below.

3. The pull-out range ∆ωPO This is the dynamic limit for stable operationof a PLL. If tracking is lost within this range, an LPLL normally will lockagain. This process is slow if it is a pull-in process. This defines how largea frequency step the LPLL can handle without unlocking.

4. The lock range ∆ωL. This is the frequency range within which a PLL

locks within a single-beat note between reference frequency and outputfrequency. It is independent of the speed the phase was changed, just aslong as it does not exceed this range.

The definitions are not specific to his book, but are standard terms among PLLdesigners. However they do not apply to the other types of PLLs mentioned,the digital PLL and the all-digital PLL.

As a vivid example of the non-linear behavior, an actual pull-in processsimulated in Matlab is shown in Fig. 2.10. The LPLL is initially locked inphase (π/2 rad out of phase as explained above). At t = 1 a large frequency step(larger than the pull-out range) is applied and the LPLL loses phase tracking,

but since the reference is within the pull-in range, the LPLL will try to pull theVCO closer to the reference.

-

8/19/2019 Real-time phase-locked loops

32/48

2.4 Non linear properties 21

0.9 1 1.1 1.2 1.3 1.4 1.5 1.6

10

20

30

40

50

60

Difference between input phase and feedback phase

Time[s]

P h a s e [ r a d ]

Figure 2.10: The pull-in process for a LPLL implemented in software. it finally settled at21× π = 65.97 radians out of phase.

After the pull-in process, the linear locking phase takes place and it settles

at N × π out of phase, which is a true phase lock. In the unlocked state,the phase detector modulates the VCO in a nonharmonic way. That impliesthat the output of the VCO is nonharmonic. The frequency of the VCO isthen sometimes closer to the reference, and sometimes further from it. Thatis, we have a time dependent frequency difference. But the frequency of theVCO varies in such way that is more often closer to than further from thereference. Therefore, in each cycle, the average frequency is slightly shiftedtowards the reference. This asymmetry of the VCO causes it to change theaverage frequency even faster towards the reference. The VCO is pulling itself in.

2.4.2 Design criterion from a non-linear point of view

Depending on the choice of filter, the PLL will stay unlocked or slowly worktowards its locked state. It can be shown that a LPLL designed with filterhaving a pole in s = 0 always becomes locked eventually. We can state that ithas infinite pull-in range. If speed is never an issue, the afore mentioned naturalfrequency parameter ωn can be set very low to make the system minimize thephase jitter noise. However if speed is crucial a trade off has to be found betweennoise and speed. For the application under consideration the bandwidth will beset low, making it slow and low noise. For quite stable 19 kHz input, a natural

frequency of around 20-50 hz proved to produce a pure input and still providea fast enough lock-in process.

-

8/19/2019 Real-time phase-locked loops

33/48

22 Phase locked loops

2.5 The Software Phase Locked Loop

2.5.1 Discretizing the LPLL

After covering the theory of linear PLLs, a discrete model can now be made,suitable for implementation on a digital signal processor. The fundamental ruleto follow when digitizing a signal or system is the Nyquist criterion. It states:the sampling frequency has to be at least twice the highest frequency of thesignal if we want to avoid aliasing.

When moving from a continuous to a discrete model a discrete model of acontinuous system, we take one step closer to a working software implementa-tion. However, it is not the final step. The target hardware platform has tobe taken into consideration. The hardware specific issues will be covered in the

next section, right after dealing with the discretized models.

Discrete phase detector

The phase detector is the part where aliasing effects may occur if we are notcareful. Since the phase detector is a multiplier, the output when subject totwo sinusoids is, as defined above,

ud(t) = U inU fb

2 (cos(θin − θfb) − cos(2ωt + θin + θfb)). (2.35)

By observing the second term, cos(2ωt + θin + θfb), the sampling frequencyhas to be extended. The phase detector doubles the bandwidth requirements.

Therefore, the sampling frequency has to be four times the highest frequencyin the system to avoid aliasing. Depending on the frequency characteristicsof the input we may or may not have to extend the criterion. If it is puresinusoid and the resulting aliased frequency content does not affect the followingsystems negatively it might suffice with twice the sampling frequency after all.Problems arise when the aliased contents comes close to DC. It will then affectthe Software Controlled Oscillator (SCO) since the signal passes the discretelow pass filter.

Discrete low pass filter

The loop filter has to be discretized in a suitable manner. Since minimumcomplexity from a computational time viewpoint is wanted, an Infinite ImpulseResponse (IIR) filter is the filter type to use. Also, since an analog filter modelis readily available, the design of the IIR filter is straightforward. An analog-to-digital transformation has to be performed. Several such transformation exists,among them are the Impulse Invariant Transform, The Backward DifferenceMethod and the Bilinear Transform. Porat[6] explains the theory behind themand concludes that the bilinear transform is superior to other methods. It issuitable for all filter types since it preserves the order and stability of the analogfilter. Also, the continuous frequency and phase responses is directly mappedto the discrete ones. The bilinear transform is defined by the substitution

s ← 2T

· z − 1z + 1

(2.36)

-

8/19/2019 Real-time phase-locked loops

34/48

2.5 The Software Phase Locked Loop 23

An additional operation called pre-warping is also performed when using thebilinear transform to overcome the frequency warping introduced since the bi-linear transform maps ω = ±∞ to θ = ±π, see [6] for details. Any filter designtool or the MATLAB command bilinear takes care of the transform correctly.For example, when transforming the PI-filter suggested above to the z-domain,the result becomes

F (z) = b0 + b1z

−1

1 + a1z−1 . (2.37)

Where the wanted discrete filter coefficients are calculated as

a0 = 1

a1 = −1

b0 = T

2τ 1

1 +

1

tan(T /2τ 2)

b1 = T

2τ 1

1 −

1

tan(T /2τ 2)

After transforming Eq. 2.37 back to the discrete time domain, the followingdifference equation is the result,

a0uf [n] = b0ud[n] + b1ud[n − 1] + a1uf [n − 1]. (2.38)

The filtered output uf [n] is then used to control the total phase in the SCO. The

expression ’total phase’ will be explained below. The analog PI filter describedabove and its digital version can be seen in Fig. 2.11.

10−5

100

105

−50

0

50

100Amplitude resp.

Frequency [Hz]

M a g n i t u d e [ d B ]

10−5

100

105

−100

−50

0

50Phase resp.

Frequency [Hz]

P h a s e [ d e g ]

Analog

Digital

Figure 2.11: Analog PI filter and its digital counterpart created using the bilinear transform.

-

8/19/2019 Real-time phase-locked loops

35/48

24 Phase locked loops

Software controlled oscillator and divide-by-N block

The SCO is implemented in a quite specific manner. Instead of directly con-trolling an oscillator as in the analog case above, it is possible to count the total phase of the synthesized signal. That can be achieved by initiating a variableto zero and then add phase to it. Recall from the LPLL theory in section 2.3.2,the VCO is nothing but an integrator for phase and also recall that discreteintegration is simply a sum. The total phase can therefore, in the discrete case,be written as

φ2[n + 1] = φ2[n] + (ω0T ) + (K 0uf [n]T ) (2.39)

Equation 2.39 extrapolates the phase at the next sample instance by addingmore phase to the current phase. The phase contribution of the center frequency

term is ω0T . The last term K 0uf [n]T represents the additional phase neededto decrease the phase error detected by the phase detector. The time step isT = 1/F S . The SPLL output will be synthesized by letting u2[n] = sin(φ2[n])and feeding that signal to the digital to analog converter.

Before the extrapolated SCO feedback in discrete time is created, the modelis slightly adjusted to incorporate the divide by-N block at this point. It isdone by letting u2[n + 1] = sin(K n φ2[n + 1]). This will ensure that the outputphase is always N=1/K n times the input as derived in section 2.3.3.

2.5.2 Hardware specific issues

Up to this point, neither the LPLL design discussion nor the SPLL extension hastaken any of the hardware related problems into account. When implementingalgorithms for a specific hardware, another layer of problems have to be solved.In the following subsections the most important problems are outlined and if possible, dealt with.

Fixed point number representations

Only a finite number can be represented on any hardware platform and thishas to be considered at all time. Floating point hardware have many upsides.Large numbers or small numbers with high precision can be represented. In

addition algorithms tend to be easier to implement in contrary to a fixed pointenvironment. However floating point hardware tend to be more costly. Thetarget for this particular implementation is a less expensive fixed point DSPplatform. Therefore the algorithm has to take that into consideration.

In the SCO case, if we add more phase to that highest value, the variableoverflows and the largest negative number will be the result. One solution tothis is to wrap the phase by subtracting 2π from the total phase when it exceeds2π, because

sin(φ2 n) = sin((k2πφ2) n).

Where k is an integer number of revolutions around the unit circle. Another

solution is to take advantage of the overflow effect and use that for wrapping.By representing the highest positive number by π and the most negative number

-

8/19/2019 Real-time phase-locked loops

36/48

2.5 The Software Phase Locked Loop 25

by −π the wrapping is done by the overflow, since

sin(π + a) = sin(−π + a).

See [7], or any basic textbook on digital systems for details on the subject of number representation and overflow.

Another problem when dealing with fixed point hardware is the limited pre-cision in fractional numbers, mainly concerning filter coefficients. Roundingoff a high precision filter coefficient from a filter design tool may result in amalfunctioning filter. This is an important subject and the depth is beyondthe scope of this report. Filter of higher order are more likely to fall into thiscategory and it is vital to implement the filter in a manner that reduces therisk with low precision coefficients. The question of suitable filter structures

comes up. The direct form of IIR filters are seldom used directly in implemen-tations, instead the filter is reordered into a sequence of second order sections.Such an arrangement is called Cascade form. The loop filter implementationin this thesis is of second order only and hence the filter cannot be reduced incomplexity.

Computation time

This is simply the question of available computing time versus the time neededby the algorithm. In a system like a PLL, the entire algorithm has to berun at each sampling instance. An accurate prediction of the execution time

needed by the algorithm is probably cumbersome to do on beforehand. Insteadimplementing the algorithm in a high level language and then measuring thecycles needed in a suitable simulation/test environment, or on a general purposeCPU, like a workstation. If it does not meet the timing requirements, suitableoptimizations in low level assembly might be needed or as a last resort, changethe target hardware to a faster one.

A sample-by-sample based algorithm that does not finish in time is easilydetected. Since each sample arrives at a fixed rate, and will be processed by aprioritized interrupt, the processor will have to stop the algorithm calculationsfor the previous sample to serve the interrupt. Serving the interrupt most likelyimplies running a new cycle of the algorithm. Therefore the algorithm will never

be run completely on any sample, also the interrupt call stack will be full andresults will be undefined at best, probably the processor will hang. At any case,the PLL output will speak for itself.

If other tasks is to be run on the hardware at the same time, a user interfacefor example, the designer may want to consider using a real-time operatingsystem that handle resources and help the algorithm with timing issues. Thesubject of real-time systems cover this, and an in depth study is beyond thescope of this text.

Codec delay

The hardware interfacing with the outer world feeds the processor with samplesat a fixed sample rate. This hardware is in this case called a codec and consists

-

8/19/2019 Real-time phase-locked loops

37/48

26 Phase locked loops

of one or several Analog to Digital Converters (ADC) and Digital to AnalogConverters (DAC). The ADC employs oversampling and digital anti-alias fil-tering. This takes time. In data sheets it is mentioned as ’Codec group delay’.In addition, an SPI (Serial Peripheral interface) bus is used for communicationwith the host processor. Therefore the delivery of samples is done with a no-ticeable delay. The delay is fixed for all frequencies within the operating rangeand may extend to hundreds of microseconds. Remember that a fixed groupdelay corresponds to a linear phase shift. For example, a group delay of 1 msat 19 kH z shifts the phase by 19 cycles or 6840 degrees, clearly not negligible.In the case of a software PLL that has to be locked in phase at all time thisproved to be a quite troublesome issue.

The solution to the problem actually made the internal SPLL demands to

be relaxed to only be locked in frequency, since locking in phase becomes a falsetruth when compared to the external signal. The solution became to connecta phase adjusting system behind the SPLL, comparing the original signal withthe one generated by the SPLL and then simply adjust a final output to matchthe phase of the main input, compensated for any divisions/multiplications of phase made in the feedback. Practically it was solved by feeding the SPLLfeedback signal to the DAC and then sample it again using the ADC.

The phase adjusting system makes use of the phase accumulator in theSPLL, as seen in Fig. 2.12. It works by making subtractions or additions when

uin(t)

u (t)out

Phasedetector

u [fb n] Frequencymultiplier

Loopfilter

SCO( [n])2

uin[n]ADCdelay

DACdelay

Phasedetector

Slow MAfilter

Parameter decision

DACdelay

ADCdelay

SPLLSampled domain

u [n]out

SCO( [n]+ ) 2 m

Frequencymultiplier

m

Figure 2.12: An SPLL with secondary oscillator controlled by a phase adjusting subsys-tem. The dashed line is the adjustments made at specific times decided by theparameter decision block, and not at system sampling instances.

needed to the total phase defined by Eq. 2.39. With this method of an external

phase adjustment, any phase differences introduced, inside or outside the SPLLis compensated for. The phase of the final output is therefore an adjusted

-

8/19/2019 Real-time phase-locked loops

38/48

2.5 The Software Phase Locked Loop 27

version of Eq. 2.39:

φ3[n + 1] = φ3[n] + (ω0T ) + (K 0uf [n]T ) + φm, (2.40)

But since φ2, the accumulator for the SPLL, can not be touched, we keep aseparate accumulator φ3. It will really be φ2 + Σφm since both are set to zeroat start. In plain text, this means that φ3 follow φ2 in frequency but adds asmall correcting phase shift. The adjusted phase is then fed to a sine generatorthat generates the final output.

The parameter decision block is implemented as a threshold device, makingthe phase corrections be

φm = K Lug[m], ug > |L|

andφm = 0, ug[m]

-

8/19/2019 Real-time phase-locked loops

39/48

-

8/19/2019 Real-time phase-locked loops

40/48

Chapter 3

Results

This report has up to this point covered the theory of linear phase locked loopsand an additional discussion on how to implement them in software. A work-ing SPLL was designed using the methods presented in the previous chapter.To gain understanding in how the SPLL operates, tests and experiments wereconducted using Matlab mostly. However, as the SPLL design began to lookpromising, the developing process where continued on the target hardware sim-ulation platform.

3.1 Matlab

The Matlab implementation began with allocations of signals and result datavectors. Main design parameters such as SCO center frequency and filter nat-ural frequency were set. Before simulation the analog filter design were dis-cretized using Matlabs bilinear command. Also the filter constants wererounded off to emulate the 16-bit fixed point environment on the target hard-ware. The piece of commented MATLAB program code below show how it wasimplemented. It shows the sample-by-sample loop where the SPLL is running.

for(n=2:indEnd-1)

% Phase detector, uin - noisy input sinusoid

ud(n)=uin(n)*ufb(n);

% IIR Filter, fac depends on the accuracy used in the filter

% design, filter constants where rounded off to emulate fixed

% point problem pointed out.

%a(1)*y(n) = b(1)*x(n) + b(2)*x(n-1) + ... + b(nb+1)*x(n-nb)

uf(n)=(b0*ud(n)+b1*(ud(n-1))-a1*uf(n-1))/fac;

% Estimate phase

phi2(n+1)=phi2(n)+w0*Ts+uf(n);

% Non wrapped phase for measurements

phi3(n+1)=phi3(n)+w0*Ts+uf(n);

-

8/19/2019 Real-time phase-locked loops

41/48

30 Results

% Wrap phase

if(phi2(n+1)>pi)

phi2(n+1)=(phi2(n+1)-2*pi);

end

% SCO

uout(n+1)=sin(phi2(n+1));

% Feedback

ufb(n+1)=Uf*sin(Kn*phi2(n+1));

end

The signals in the program code can be seen in Fig. 3.1. The center frequency of

the SCO was set to 4 kHz in the example and the input kept a stable frequencyduring the first second. After one second the input were stepped up to 4.1 kHzand the SPLL where allowed to settle. A DC offset can be seen in the signaluf [n] due to the offset from the center frequency of the SCO.

3.2 Real-time hardware implementation

3.2.1 Hardware specification

When the matlab model proved to be accurate and working, the SPLL wasimplemented on a real-time hardware platform, the Analog Devices ADSP-

BF533 EZ-KIT LITE REV 1.5, based upon the Blackfin 533 DSP.The EZ-KIT LITE has a high quality audio codec built in, the AD1836 is

also made by Analog Devices. It supports four ADCs and 6 DACs at a maxi-mum sampling frequency of 96 kHz with a resolution of 24-bits. It utilizes highoversampling and low pass filtering to avoid aliasing. However the same filteringoperation is specified to take up to 1 ms according to the data sheet. At thispoint the codec delays, mentioned earlier were discovered. The delay made itimpossible for the SPLL to gain phase lock between the two analog signals(maininput to codec, and output at divided frequency) without an additional phasecorrecting system.

3.2.2 Developing environment

The language used for programming the DSP was C exclusively. An excessivepart of the SPLL performance where evaluated on the target hardware using thedebugging tools in VisualDSP++ IDE(Integrated Developing Environment).

In addition, the PC communicated with the DSP via a piece of externalhardware called an In-Circuit Emulator or ICE. ICE hardware is used to debugthe software of an embedded system. The ICE hardware communicated inturn with the DSP via the JTAG interface. When using the ICE hardware,debugging went more smooth, stepping code was easy, and data transfer rateswere improved.

-

8/19/2019 Real-time phase-locked loops

42/48

3.2 Real-time hardware implementation 31

0 5 10 15 20 25 30 35 40−1

0

1

uin[n] − Noisy input(4Khz)

0 5 10 15 20 25 30 35 40−pi

0

pi

phi2[n] − Wrapped phase

0 5 10 15 20 25 30 35 40−0.5

0

0.5

ufb

[n] − Feedback to phase detector

0 5 10 15 20 25 30 35 40−1

0

1

uout

[n] − Output at divided frequency

0 5 10 15 20 25 30 35 40−0.5

0

0.5

ud[n] − Phase detector output

0 5 10 15 20 25 30 35 400

0.005

0.01

uf

[n] − Filtered phase detector output

Figure 3.1: The signals of importance in a discrete linear PLL. It is locked to a noisy inputof 4.1 kHz.

-

8/19/2019 Real-time phase-locked loops

43/48

-

8/19/2019 Real-time phase-locked loops

44/48

3.2 Real-time hardware implementation 33

Figure 3.2: Spectrogram of input and output to the SPLL implemented on a DSP.

-

8/19/2019 Real-time phase-locked loops

45/48

34 Results

Figure 3.3: Oscilloscope dump of the SPLL input at 19 kHz and the in phase locked half frequency output.

Figure 3.4: Oscilloscope dump of the FFT of the SPLL output. 10dBV per square.

-

8/19/2019 Real-time phase-locked loops

46/48

Chapter 4

Conclusion

The theory of linear PLL were studied and the most relevant parts were outlinedin this report, as well as design methods for implementing one in software fora real-time application. A working implementation were tested in both Matlaband in real-time. The report deals with subjects such as control theory, analogand digital filter design, C programming and writing of a technical report. Thesolution to the codec delay problem were custom made, but proved to work wellfor the particular application.

The thesis was very rewarding from both a theoretical and a practical pointof view. Knowledge from a broad range of courses studied during my engineeringeducation was used throughout the work. Nothing was obvious to start with,

and i find the solution to be creative rather than close to optimal.As a valuable bonus to the thesis work; i was hired by the firm Rubico andhas by the time of writing worked there for over a year.

-

8/19/2019 Real-time phase-locked loops

47/48

Appendix A

Program code

The complete source code used in the thesis is not included since it is ownedby the company that offered this thesis. However, questions regarding theimplementation in general is best answered by sending the author an e-mail.

-

8/19/2019 Real-time phase-locked loops

48/48