Prior: ITT Defense, Plantronics/Wilcom, Airex · Prior: ITT Defense, Plantronics/Wilcom, Airex....

Transcript of Prior: ITT Defense, Plantronics/Wilcom, Airex · Prior: ITT Defense, Plantronics/Wilcom, Airex....

About the presenter:

CJ Clark is the CEO of Intellitech Corp.

Prior: ITT Defense, Plantronics/Wilcom, Airex

IEEE Standards Medallion 2013 Award - Dec 2013 For vision, leadership and exceptional dedication in enabling IEEE standards to lower costs for the electronics industry

Elected IEEE 1149.1/JTAG Chairperson 1996-2001 & 2010-2013

Active member of P1838, P1687, P1149.6, etc

VTS 2012 Best Special Session Award - "IEEE P1149.1-2013…"

Co-inventor on 40+ US/foreign patents related to FPGA/JTAG

UNH CEPS Advisory Board Member (2000 - 2013 Emeritus )

1

www.intellitech.com

The Future of Test Automation - Where Should We Place Our

Bets?

CJ Clark, Intellitech CEO

Copyright © 2013 Intellitech Corp. All rights reserved. 2

www.intellitech.com

• Where have we been? (what's this guy's track record?)

• The Role of Standards • What's hot now • Where will we be in 5 years?

3

Outline

www.intellitech.com

4

Where have we been? Intellitech Tcl JTAG script circa 1997

• Protocol agnostic • Dotted Hierarchy • Mnemonics • Re-usable

www.intellite

ch.com

5

Where have we been? Intellitech Tcl JTAG script circa 1997

• Protocol agnostic • Dotted Hierarchy • Mnemonics • Re-usable

Tcl "with JTAG" now In 1149.1-2013 and P1687 Different commands but

Concept the same Maybe 85% right?

www.intellitech.com

6

Fast Access Controller (2000) - Early TAP based Silicon Instrument - US #6,594,802 and foreign counterparts - Resides in FPGA or SoC - Programs external Flash

www.intellitech.com

7

Fast Access Controller (2000) - Early TAP based Silicon Instrument - US #6,594,802 and foreign counterparts - Resides in FPGA or SoC - Programs external Flash

- Licensed by several - FPGA vendors. (see

Intellitech website)

- Most widely adopted instrument (thousands use it per day)?

www.intellitech.com

10

DATE 2003 CEO Panel - past slides

- Maybe 80% right? - "Instruments" used not

"On-chip IP" - Many monitors and

instruments accessible via TAP

- One standard 1149.1-2013

and one proposal in the works P1687

www.intellitech.com

11

2005 - TMW Cover Story - early instruments Polycom use of Intellitech DDR-IP+ BERT-IP

www.intellitech.com

12

Need continues to grow - Customer proven - IEEE 1149.1-2013 compliant - Addressable silicon instruments - Rates @ 6.5Gb/s

www.intellitech.com

13

Need continues to grow BERT-IP library and PDL descriptions read by NEBULA tool

www.intellitech.com

14

• Where have we been? • The Role of Standards • What's hot now • Where will we be in 5 years?

www.intellitech.com

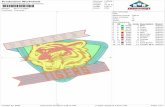

SysReset

IC1

BOUNDARY REGISTER

TAP

INIT-DATA REGISTER

IR & Decode & Muxing

User Defined Chain(s)

DACADC

0

1

0

1

On-chipReset via

TAP

PRBS

Swing

CMMV

UniqueECID

AC/DC

MemoryBIST

PLL

Volt.Mon

Protocol

LogicBIST

10

USBRegister Segmentation and

Power domain controlDC

Input

1149.1-2013 adds depth to the other half of the standard - Standard Test Access Port and Boundary Scan architecture

"Boundary Scan" has always been a misnomer, it's only a part of the standard. Standardization for internal JTAG registers via the Test Access Port Hierarchical language for On-chip IP (Silicon Instruments) Synergy with IEEE 1500 and IEEE 1801 - re-use popular IEEE 1500 structures - TDRs can cross power domains - TSV Maps for 3D-IC 444 Pgs vs. 208 pgs in 1149.1-2001

15

www.intellitech.com

16

IEEE Std. 1149.1-2013 lowers industry costs by enabling test re-use through all phases of the IC life-cycle

- Specifies best practices for Infrastructure IP test interfaces - Specifies rules for describing IP operation - Enables one description to be used in all test stages - Enables defect correlation between system failures and IC ATE Note: doesn’t require production IC test through TAP

www.intellitech.com

17 Courtesy of Phil Nigh, IBM ITRS "Adaptive Test" section chair

IEEE 1149.1-2013 plays a role in ITRS Adaptive Test - LPC (Tap, clocks, compliance enable) - ECID, Isolation from ecosystem, TAP based reset

www.intellitech.com

18

JEDEC Standards WIO and HBM Supported by IEEE 1149.1-2013

(Intellitech Demo at 3D-SIC Workshop)

www.intellitech.com

19

• Where have we been? • The Role of Standards • What's hot now • Business Model changes • Where will we be in 5 years?

www.intellitech.com

20

For board test: JAF® Test - JTAG Assisted Functional Test

CPU JAF® Test FPGA JAF® Test

www.intellitech.com

21

Development Environment for 1149.1 Silicon Instruments FREE NEBULA tool - reads 1149.1-2013 BSDL and PDL http://www.intellitech.com/ijtag

www.intellitech.com

ISIS for Win/Linux-64

JTAG Driver

Simulator

Instrument

Instrument

SoC Design

TAP

NEBULA JTAG

Debugger

Pre-silicon Validation of 1149.1-2013 IP package and PDL

www.intellitech.com

24

• Where have we been? • The Role of Standards • What's hot now • Where will we be in 5 years?

www.intellitech.com

1149.1-2013 ECID used for tracking and anti-counterfeiting

Problem: Supply chain re-marking of parts to alter speed grade or Temp (C/I) - 3rd parties have little resources to test/validate

Wafer SI SO

Tracking/Correlation ECID can be defined or made private - shown for convenience - Can also be encrypted/scrambled Grading information should be made public Values programmed during test/binning/burn-in by trusted OSAT (Out Sourced Assembly and Test) house

DIEXY FAB

Tracking/Correlation ECID

Speed Temp

Solution: IEEE 1149.1-2013 ECID programmed with rated temp/speed in OTP efuse/NVM

Grading

STS Pass /Fail

www.intellitech.com

TAP

PC S

Re-use Mission mode PHY/PMA/PCS PMA= Physical Media Access PCS = Physical Coding Sublayer - 8/10/16/20/32/40 width Re-direct to P1149.10 packet to (En/De)code and distribution matrix Test of P1149.10 circuitry via TAP or other means EDA tools see just "design logic" As traditional IEEE 1500 design (No new ATPG needed) On-chip control & timing ~25 or so in study group

Init_data

Packet (En/De)code

Distribute

WS P 0

WS P 1

WS P n

Design

26

WPP

…

C & T

www.intellitech.com