Powering Collaboration and Innovation in the Simulation ... · 3.125 Gbps PRBS 231 10-15 Contour...

Transcript of Powering Collaboration and Innovation in the Simulation ... · 3.125 Gbps PRBS 231 10-15 Contour...

Powering Collaboration and Innovationin the Simulation Design Flow

Agilent EEsof Design Forum 2010

EEsof 2010Page 1

Channel Simulator and AMI model support within ADS

EEsof 2010

Contributors to this Paper

José Luis Pino, Agilent Technologies

Amolak Badesha, Agilent Technologies

Fangyi Rao, Agilent Technologies

Sanjeev Gupta, Agilent Technologies

Chad Morgan, Tyco Electronics

Page 2

Special thanks to Chad Morgan, Tyco Electronics for

providing measured and simulated data for STRADA

Whisper and HM-Zd backplanes

EEsof 2010Page 3

Agenda

• Introduction to Channel Simulation

• Brief introduction to IBIS AMI Model

• AMI model simulation in ADS2010

• AMI model Generation using System Vue

EEsof 20104

Introduction to Serial Link

Channel

∑

Jitter

EQ

RX

Received

Signal

∑

JitterXTalk1

PRBS EQ

∑

JitterXTalkN

PRBS EQ

∑

JitterTX

PRBS EQ

•Behavioral models

•Transistor level models

•IBIS AMI

•Behavioral models

•Transistor level models

•IBIS AMI

Passive

Interconnect

EEsof 20105

Comparison of Simulation Techniques in ADS 2009

Transient

Simulator

Channel Simulator:

Bit-by-bit mode

Channel Simulator:

Statistical mode

Method Modified nodal

analysis of Kirchoff’s

current laws for

every time step

Bit-by-bit

superposition of step

responses

Statistical

calculations based

on step response

Applicability Linear and non-

linear circuits

LTI, any specific bit

pattern, adaptive eq.

taps, IBIS AMI

LTI, fixed (general)

bit pattern, fixed eq.

taps

BER floor in one

minute

simulation

~10-3 ~10-6 Arbitrarily low

EEsof 2010

6

Channel Simulator Methodology

ISI

Step response is calculated Bit by bit mode : Superposition of bits

Statistical mode : Statistical techniques

EEsof 20107

Channel Simulator: Bit-by-bit and

Statistical ModesIntegrate layout

artwork into

schematic

EEsof 20108

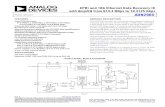

STRADA Whisper 11.5” System (w/ Cables)

Short, High-Quality Channel

• Eyes measured with Scope

• S-parameters measured and run in fast statistical

simulators

6.25 Gbps

PRBS 231

10-15 Contour

Scope ADS Overlay (Red Contour)

Height: 33%

Width: 63%

Height: Closed

Width: Closed12.5 Gbps

PRBS 231

10-15 Contour

Height: 40%

Width: 74%

Height: 6%

Width: 28%

Verification of Simulated data

EEsof 2010

3.125 Gbps

PRBS 231

10-15 Contour

Scope ADS Overlay (Red Contour)

6.25 Gbps

PRBS 231

10-15 Contour

Height: 37%

Width: 66%

Height: 4%

Width: 21%

Height: 42%

Width: 76%

Height: 7%

Width: 30%

9

STRADA Whisper 27” System (w/ Cables)

Long, High-Quality Channel

• Eyes measured with Scope

• S-parameters measured and run in fast

statistical simulators

Verification of Simulated data

EEsof 201010

Crosstalk Validation : Synchronous Noise

HM-Zd 10” System ‘In-Row’ Near- and Far-End Crosstalk

• Highest magnitude crosstalk in available systems

• 6.25 Gbps, PRBS 231, no EQ, & no induced jitter

Measured NEXT ADS NEXT ADS Overlaid on Test Data

Both 5%p-p NEXT

ADS Overlaid on Test Data

Both 4%p-p FEXT

Measured FEXT ADS FEXT

Verification of Simulated data

EEsof 201011

Crosstalk Validation: Asynchronous Noise

HM-Zd 10” System ‘In-Row’ Near- and Far-End Crosstalk

• Highest magnitude crosstalk in available systems

• 6.25 Gbps, PRBS 231, no EQ, & no induced jitter

ADS Overlaid on Test Data

Both 5%p-p NEXT

ADS Overlaid on Test Data

Both 4%p-p FEXT

Measured FEXT

Measured NEXT ADS NEXT

ADS FEXT

Verification of Simulated data

EEsof 201012

STRADA Whisper 11.5” System (w/ Cables)

Short, High-Quality Channel

• ADS (statistical mode) optimize 3 FFE taps automatically

• Sim taps used with Oscilloscope

6.25 Gbps

PRBS 231

10-15 Contour

t(0) = +0.825

t(1) = -0.145

t(2) = -0.030

Scope ADS Overlay (Red Contour)

12.5 Gbps

PRBS 231

10-15 Contour

t(0) = +0.762

t(1) = -0.202

t(2) = -0.036

Height: 39%

Width: 82%Height: 46%

Width: 85%

Height: 21%

Width: 63%

Height: 23%

Width: 68%

Verification of Simulated data

EEsof 201013

STRADA Whisper 27” System (w/ Cables)

Long, High-Quality Channel

• ADS (statistical mode) optimize FFE taps

automatically

• Sim taps applied to Scope

3.125 Gbps

PRBS 231

10-15 Contour

t(0) = +0.810

t(1) = -0.165

t(2) = -0.025

Scope ADS Overlay (Red Contour)

6.25 Gbps

PRBS 231

10-15 Contour

t(0) = +0.745

t(1) = -0.222

t(2) = -0.033

Height: 41%

Width: 79%

Height: 20%

Width: 62%

Height: 46%

Width: 88%

Height: 27%

Width: 76%

Verification of Simulated data

EEsof 2010

Algorithmic Modeling Interface (AMI): Introduction and

Ecosystem

14

AMI model

AMI simulator

System company

SerDes Vendor

EDA vendor

• Customized IC models representing actual device behavior

• Compiled models protects vendor IP

• Portable and supported by EDA tools

• Two aspect

• Model Generation (mostly semiconductor vendors)

• Model Simulation (mostly system companies)

EEsof 2010

Introduction to Algorithmic Modeling

Interface (AMI)

• System is simplified to three blocks: TX + channel + RX

• TX and RX models: regular IBIS model + AMI extension

• AMI extension: DSP blocks that model equalization (EQ) and CDR

TX AMI

(EQ)

TX backend

(VT table+Pkg)

channel RX frontend

(Pkg)

RX AMI

(EQ+CDR)clock ticks

100110

Impulse response

• Assumption 1: linear time invariant (LTI) system

• Assumption 2: zero impedance at TX AMI output and infinite load at RX AMI input

• Simulation is reduced to TX DSP + channel impulse convolution + RX DSP

• Orders of magnitudes faster than transistor level SPICE simulation

EEsof 201016

Simulation Flow

Initialization

Time domain simulation

TX Init RX Init

channel impulse modified impulse modified impulse

TX GetWave Impulse convolution RX GetWaveclock ticks

100110

AMI Models implement three interface functions:

Init: takes channel impulse response as input, performs initialization, allocates memory, and

returns modified impulse (optional).

GetWave: takes input waveform and returns modified waveform. RX also returns clock times.

Close: free memory.

EEsof 201017

AMI Model Files

Each model includes following files:

• DLL or/and shared object (so): three functions

Init(char * params_in, …)

GetWave(waveform_in,

waveform_out,

clock_tick_array)

Close()

• .ami file: an ASCII file specifies model parameters input to Init()

• .ibis file: specifies file names of .ami and DLL and compilation

platform

EEsof 201018

.ibis File

…

[Algorithmic Model]

Executable Windows_VisualStudio_32 IBIS_AMI_Tx.dll IBIS_AMI_Tx.ami

Executable linux_gcc_64 libIBIS_AMI_Tx.so IBIS_AMI_Tx.ami

[End Algorithmic Model]

…

The file specifies:

• Platform_Compiler_Bits

• DLL file name

• Parameter file name

EEsof 2010

AMI Model Simulation within ADS

Supported in ADS2010

EEsof 2010

The AMI Model Lifecycle…disconnected flows

SerDes DesignHDL, Verilog-A/AMS, Matlab, C/C++, Spice

AMI ModelingMatlab, C/C++, Code

Generation

AMI Testing/Validation

Channel Simulators, Correlation with Spice &

Measurements

End CustomerChannel Simulators

System Architect, IC Designer

Modeling Engineer

SI/Application Engineer

System Design Engineer

AMI-Modeling adds significant engineering requirement for coding, without any major benefit for IC vendor

Platform & Compiler Version dependencies, Correlation with Spice and Measurements

EEsof 2010

#1 AMI-Modeling BarrierModel Generation Time

AMI Modeling suppose to Speed-up System Design Cycle,BUT, Model-generation takes Significant Time & Resources

….System Vendors have to wait a LONG time before Vendor models become available

Note: Vendors with NO experience in AMI modeling are spending 8-16+ months to come up with first-generation models

Models come very late in Design Cycle used only for Validation, NOT Design

0 months

4 months

8 months

12 monthsNightmare Begins

AMI 101, Decipher Code

Early Model prototypes

First-model to Customer

EEsof 2010

In-house AMI Model Development: Why and How?

AMI model generation key requirements:- Efficient Tops-down “Electronic-System-Level” Design Methodology- Basic (customizable) system algorithmic building blocks representing SERDES- Integration with HSPICE based data- Efficient simulation and validation of system Performance before model creating- Automatic and efficient C++ Code-generation along .dll compilation- Auto .ami file generation

-Algorithmic

IP - TX

Algorithmic

IP - RX

AMI

Model

Generation

SerDes

Measurement

ESL Design Flow with Automatic AMI model-generation

IBIS-AMI

TX

Channel

Simulation

IBIS-AMI

RX

Channel Simulator

Physical Channel

Modeling

ESL Simulator

Protect your SERDES IP with heart and Soul: Do not leave it loose

EEsof 2010

Introduction to “System Vue” (ESL) and AMI Model

Generation Design Flow

EEsof 2010

TX Modeling Example (1)

Step-1: Starting Architecture Design with Generic Model

FIR/IIR filter n-tapFFE

Gain

Different blocks represent high-level TX architecture

EEsof 2010

More on FIR Filter…How to bring in Spice or Measured data?

Challenges:1. Typical Simulation and Measured Data is not equally time-stepped

Low Sampling Rate

High Sampling RateFIR model should support “Arbitrary” Sampling Rate

Sampling Rate determines Simulation Accuracy

EEsof 2010Page 26

SERDES and Channel Modeling using System Vue

•TX De-emphasis

•TX Jitter

•RX Equalization (CTLE+DFE)

EEsof 2010Page 27

6.25 Gbps Channel : Eye Diagram Verification

Integrated Flex DCA software

EEsof 2010Page 28

Eye Diagram @TX O/P Eye Diagram @Channel O/P

Eye Diagram @ After CTLEEye Diagram @ After CTLE +DFE

6.25 Gbps Channel : Eye Diagram @ Various Probe Points

EEsof 2010Page 29

6.25 Gbps Channel Simulation : Jitter Analysis

EEsof 2010

System Vue: TX Modeling Example (2)

Step-2: Customize IP -> Bring in M-code or C++ Code

Fine-tune and Customize models with Matlab Syntax and/or C++ code

EEsof 2010

System Vue: TX Modeling Example (3)

Step-3: One-click AMI Code-Generation

Define Reserved and Model Specific Parameters -> Automatically configure appropriate AMI wrapper

One-click AMI Code-generation

EEsof 2010

System Vue: TX Modeling Example (4)

Step-4: Automatically Generated .ami and Visual-Studio project

The visual studio project automatically created -> One click to create .dll

EEsof 2010

Benefits of System Vue Design FlowAutomated AMI-Model Generation

1. Complete “Automation” of Code-generation and Model Compilationa task that routinely takes months because of its

complexity2. Basic building blocks that can used to start model

developmentFIR/IIR filters, FFE, DFE, CDR etc.

3. Easily customize models in include custom IPCustom C++ and M-code

4. Easy to use5. Link with Flex DCA

EEsof 2010

Next steps: Go to EEsof.com to evaluate ADS

Page 34