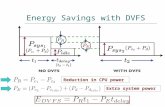

Power Savings Vary the K value Power savings between 13% and 28% Best savings of 70%

description

Transcript of Power Savings Vary the K value Power savings between 13% and 28% Best savings of 70%

Power SavingsPower SavingsVary the K valuePower savings between 13%

and 28%Best savings of 70%

Reducing Dynamic Power Reducing Dynamic Power Using Technology Dependent Using Technology Dependent

Delay Elements in ASIC Delay Elements in ASIC SynthesisSynthesisColin J. IhrigColin J. Ihrig

Gerold J. DhanabalanGerold J. DhanabalanDr. Alex K. JonesDr. Alex K. Jones

University of PittsburghUniversity of Pittsburgh

Simulation ExampleSimulation Example

Individual Node Power Individual Node Power ConsumptionConsumptionRed nodes are high powerBlue nodes are low power

MotivationMotivationChips designed for cell phones,

iPods, etc. must be low powerPrimary source of power

consumption comes from transistor switching

Characterization Results Characterization Results Standard cells in IBM 0.13um

Parasitic annotated HSPICE

netlist

Characterization automation

ConceptConceptInsert delay elements in graphs

Control latchesDelayed nodes don’t switching

Insertion AlgorithmInsertion AlgorithmDelay output of K nodesEnergy based heuristic

Considers node powerConsiders switching timeH(n)

Compute set of strict dominatorsSet S

Select K nodes from SHighest H(si) value

Delay Element CircuitDelay Element CircuitCMOS Thyristor basedReduced leakage powerDelays only rising edge

Multiplier switches for 9.25 ns

Delay element saves 5 ns of switching

Large amounts of switching activity

Control delay elements and latches

Reduced switching activity

Delay elements and latches inserted

Visible power reduction for delayed nodes

Schematic

Layout