Channel width tapering of serially connected MOSFET's with ...

Optimum design of power MOSFET's

Transcript of Optimum design of power MOSFET's

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. ED-31, NO. 12, DECEMBER 1984 1693

Optimum Design of Power MOSFET‘s CHENMING HU, SENIOR MEMBER, IEEE, MIN-HWA CHI, AND VIKRAM M. PATEL

Abstract-We present a model for the on-state resistance of power vertical, double-diffused MOS (VDMOS) transistors with emphasis on cell layout optimization and supporting experimental data. Essentially the same minimum Ron can be achieved using any of six different cellu- lar cell geometries including square and hexagonal cells. Specifically, the on-resistances of all cellular designs are essentially identical if they have the Same p-well width and the same ratio of well area to cell area. Cellular designs yield lower on-resistance than linear-cell designs unless the latter, through clever layout perhaps, allows at least 1.6 times smal- ler well width than the former. Design examples and experiments illus- trate a simple optimization procedure, which starts with choosing the minimum p-well width and. depth compatible with production tech- nology and then finding the optimum spacing between the p-wells.

I. INTRODUCTION

P OWER MOSFET’s lhave achieved better performance in switching speeds, thermal stability, and input impedance

than bipolar power transistors. The single ominous weakness is their relatively large on-state resistances [ l ] , [2]. Power MOSFET’s considered in this paper havc: the self-aligned double-diffused p-well alnd n+ source and a lightly doped epi- layer as shown in Fig. 1. This structure results in vertical cur- rent flow which eliminates the need for drain metalization on the top surface of the chip. The epi-layer supports the applied drain voltage in the off-state. This double-diffused structure has by and large replaced the older V-groove structure. The on-resistance of the two structures have been compared theo- retically in earlier works [3].

The on-resistance consists of several distinguishable compo- nents 141 : channel resistance (Rch), accumulation layer resis- tance (&), JFET or neck resistance (Ri), and epi-resistance (Repi) as shown in Fig. l(a). In higher breakdown-voltage devices, the epi-layers are thick and lightly doped, resulting in higher on-resistances. The most important design trade-off for power MOSFET’s is that between on-resistance and break- down voltage. The minimization of on-resistance at a given breakdown voltage has been studied in the literature in terms of the optimum design of dopant density and thickness of the epi-layer [ I ] , [4] and the optimum doping profile in the epi- layer [SI , [6]. The on-resistance can further be minimized, as will be shown in this paper, by proper cell layout design.

Manuscript received February 9 , 1984; revised June 13, 1984. This study is partially supported by a grant from Fairchild Camera and Instrument Corporation.

C. Hu is with the Department of Electrical Engineering and Compu- ter Sciences, University of California, Berkeley, CA 94720.

M.-H. Chi was with the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA 94720. He is now with EXCEL Microelectronics, San Jose, CA.

V. M. Pate1 was with Fairchild Camera and Instrument Corporation, Palo Alto, CA 94304. He is now with Avantek, Inc., Santa Clara, CA.

+-- s’+a’+- ~‘-4 +-s-a+--s-I

n+

(b) Fig. 1. (a) The four components of on-resistance are shown for a power

VDMOS transistor. (b) Definition of Rj and R@. Current is assumed

JFET. to flow in the shaded region. The narrowest part 1s the neck of the

Different power MOSFET manufacturers have adopted dif- ferent cell geometries-stripes, square wells in square cell, and hexagonal or square wells in hexagonal cell. Although the impact of layout design on on-state resistance has been ana- lyzed before [7] - [ l o ] , it is not clear which if any of these geometries is superior and how the cell dimensions can be op- timized. The present paper differs from other studies by pro- viding experimental data and design procedure and equations and by theoretically examining a nearly exhaustive collection of cell geometries.

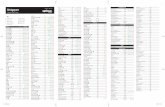

The p-well and unit cell geometrj.es together with some parameters used in this paper are shown in Fig. 2. Some clever designs such as serpentine geometries can be approximated as linear geometry having some effective dimensions. All resis- tances are expressed in ohms for 1 cm2 of active chip area, i.e., in units of C2 cm2. Models of on-resistance will be developed. Calculated on-resistance will be compared with experimental data. Relative merit of various geometries is then discussed. Finally, a general layout design procedure for the minimiza- tion of on-resistance is proposed and illustrated with examples.

0018-9383/84/1200-1693$01.00 0 1984 IEEE

1694 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. ED-31, NO. 12, DECEMBER 1984

C O E F F I E N T

CELL AREA O,is+O)

AREA OUTSIDI

I 0 ~ 0.0862 ! 0 9306 ~ 1.0746 I 0 9523 ~ I o Ap$Lble

o!/(s+a, NECK AREA

1 1 I

RATIO OF

l - [ g s ' / ( s + o l ] ~ T O C E L L

- RATIO OF

1-[gr/(s+a)]' W E L L TO

,

CHANNEL AREA

UNIT AREA

, , I I I , , WIDTH PER Z/ l z+o i 4 g z S / ( O + O l ~

I I I I

Fig. 2. Various well and unit-cell geometries and some useful quantities.

11. EPITAXIAL LAYER RESISTANCE In this paper, Repi is defined as the resistance between the n'

substrate and an imaginary electrode covering the "neck" area of the JFET. In Fig. l(b), this imaginary or effective e l w trode is represented by the dotted lines and is of width a' a:ld spacing s'. Two other quantities in Fig. 1 (b), a and s, are easier to understand. s is the width of the p-wells and a (for accumulation region) is the distance between the wells. a' a:ld s' are related to a and s by

a 1 = a - 2 A , s ' = s t 2 A

A = 0, or depletion region width (1)

a and s are known or measurable, but A can only be estimated as suggested in (1). A is usually much smaller than s and a ( in good designs) such that it can be neglected ((1)). On the otfer hand, one may assign A its upper limit, the depletion region width, and thus overestimate &pi and Ri. Each designer may make h s own estimate for A. Similarly, each designer mxy make his own estimate of y , the depth at which the ne:k occurs. We suggest

J4$ = p-well junction depth.

Repi is always larger than the ideal resistance

where A is the total active device (array) area, W is the thick- ness of the epi-layer, and p is the resistivity. The epi-resistance normalized with respect to Rided, i.e.,

repi = - Repi

RideaJ

is called the spreading resistance factor.

A. Repi of Linear Designs repi has been calculated for linear (interdigitated) layout

using 1) approximate formula [ l ] , 2 ) the assumption tkat current spreads out uniformly within a trapezoid with vari:d spreading angle [4] , and 3) exact analysis by conformal msp- ping, which results in an infinite series in elliptic integrals ['i] , [ l l ] . Fig. 3 shows repi calculated by these methods versus s ' / W for a' = s'. Repi calculated with the approximate formula

I I 1 1 1 I I I I I I t I 1 I I l l 1 1 I

0.1 0.5 1.0 2.0 5.0 10.0 51/ w

Fig. 3. repi calculated with three methods described in text (solid curves) as well as the fixed-spreading-angle model (broken curves) for a linear-geometry design with the neck area equal to 50 percent of the total cell area.

b

- to fatal ce l l area R o t l o of n e c k ore0

as a parameter 1.8 -

- Exact soIu11on

1 I I I I I I I , , I I , , , . 0. I 0.2 0.5 I .O 2.0 5.0 I O

st/ w

Fig. 4. repi calculated with 45'-spreading-angle model for linear geom- etry. The percentage of neck area is a parameter.

is low when compared with the exact solution. The trapezoid model with the spreading angle varying as a function of a', s', and W [4] overestimates repi.

We also examined a model assuming uniform current distri- bution within a trapezoid (the shaded region in Fig. 1 (b)) having a fixed spreading angle, a. The results are also plotted in Fig. 3. It was found that if a fixed 45" spreading angle is used, the results are within 5 percent of the exact solution. Furthermore, the expression for repi is relatively simple

where W ' (= s'/2 for 45" spreading angle) is the depth below the surface at which adjacent trapezoids merge together as shown in Fig. l(b). If adjacent trapezoids do not touch each other (i.e., W < s ' /2) , W' = W. Fig. 4 plots re,i calculated with (3) as well as the exact solutions with the ratio of the neck area to the total cell area, a'/(s' + a ' ) , as a parameter. The new model, clearly, is accurate over the whole range of a' and s'. In addition, the 45" spreading angle model has been shown to achieve good agreement with experimental data [ 121 .

IHU et al.: OPTIMUM DESIGN OF POWER MOSFET'S 1695

Square well geometry in hexagonal ce l l

Fig. 5. repi of cellular power MOSFET such as this one with square p-wells in hexagonal cells will be calculated using the 45"-spreading angle model.

B. Repi of Cellular Designs Almost all commercial power MOSFET's use cellular designs.

'The designs are summarized in Fig. 2 , where various p-well geometries (square, circle, and hexagon) and unit cell geom- etries (square and hexagon) are included. The only other possible unit cell is a triangular unit cell; it is judged unattrac- tive and hence is excluded.

We propose that the epi-resistance of cellular design VDMOS- FET be calculated using the 45"-spreading-angle model also as illustrated in Fig. 5 for a square well in hexagonal unit cell design. This assumption is inspired by the observation that the fixed-spreading-angle model worked well over a wide range of a' and s ' in Fig. 4. Later, limited three-dimensional simulation results also support this proposed model.

Referring to Figs. 2 and 5 , the epi-resistance of a design having square-wells in hexagonal unit cells is, as calculated using the 45'-spreading-angle model

+ lW'q PdX

- (s + a)' - (s' - 2 tan 45')' 2

where (fi/2)(s + a)z is the area of a hexagonal unit cell. The ratio of Repi to Rided

y . = ep' o w

fi - ( s + a)' 2

s + a [ ( s t a ) - g ( s ' - 2 W ' ) = [I - %I +Tw 1' (s + a) +g(s ' - 2 w ' )

( s + a ) +gs' ( s + a) - gs' 1

where g = .\/2/fi = 1.0746 for this cell geometry. Coeffi- cient g has a geometrical meaning: g is the square root of the ratio of the p-well area (square) to the unit cell area (hexagon)

d

0 1 1 ce l l u la r geornetrles /'neck orea/cell area = 50%

I ,oL 0 1.0 Z O 3.0 4.0 5.0

1

5 $ / w

Fig. 6. Solid curves show the calculated repi for both linear and various

the cellular geometries with a' adjusted for each geometry so that the cellular geometries with a' = s'. The brok'en curve is the repi for all

neck area is 50 percent of cell area.

for a = 0, i.e.,

Equation (4) and the meaning (not the numelrical value) of g hold true for all other cellular designs. Coefficient g for other geometries are shown in Fig. 2.

The solid curves in Fig. 6 show calculated repi for both linear and various cellular cell-geometries with a' = s'. All cellular geometries result in lower repi than the linear geometry for the same a' and s'. One reason for the differences in repi is that, some geometries leave larger areas for the "top electrode" (the neck area) than others. When a' is adjusted (according to the formula in Fig. 2 ) for each cellular design so that the ratio of neck area to cell area is 50 percent for all designs, repi of cellular designs becomes essentially independent of the cell geometries as indicated by the broken curve in Fig. 6. Using (4), it can be shown that the largest difference exists between square-well-in-hexagonal-cell and circular-well-in-square-cell. The latter has lower repi by at most 0.1 percent in the range of a' and s ' plotted in Figs. 6 and 7. Fig. 7 shows more curves of re,i with the percentage neck area as a parameter. The only three-dimensional simulation results [ 131 for cellular VDMOS- FET's (square-well-in-square-cell) agree well with the calcu- lation as shown in Fig. 7.

The universal cellular-geometry repi curves are compared with the repi of linear designs in Fig. E;. The linear-geometry curves in Fig. 8 can be made to coincide with the cellular- geometry curves with 3 percent difference at most by shifting the former to the right by a factor of 1.6. In other words, the percentage of gate-drain overlap is a universal parameter for both linear and cellular geometries if s ' is 1.6 smtiller for the linear geometry.

Here are some conclusions from this Repi analysis. 1) A 45"- spreading-angle model is both simpler and more accurate than other analytical models for linear geometry. 2 ) This model has been extended to cellular cell geometries and the results agree

1696 IEEE TRANSACrlONS ON ELECTRON DEVICES, VOL. ED-31, NO. 12, DECEMBER 1984

I . o c 10 i

s / A 0 . I 0 . 5 1.0 5 . 0 10.0 Fig. 9. Calculated Rj/p Wi versus s/A for linear and cellular geometries.

5 ’ / w

Fig. 7. repi for all cellular geometries with the percentage of neck ,uea as a parameter. Also shown are the only available three-dimensional linear geometry simulation results for 35- and 50-percent neck area.

I , 1 1 1 1 1 * 0 .2 0 . 5 1.0 2 5 I O

511 w Fig. 8. repi for linear and cellular geometries. For the same Wand per-

centage neck area, a linear design needs to have 1.6 times smal3:r s than a cellular design in order to achieve the same Repi.

well with limited three-dimensional simulations. 3) For the same well width s and the same percentage of neck area all cellular geometry designs yield essentially the same resista.r.ce. In other words, no one cellular geometry is noticeably bel.ter than the others. 4) Cellular geometries can result in lower vepi than linear geometry for the same percentage of neck area, unless the linear geometry allows a 1.6 times smaller s, j s . , tighter design rules.

For cellular geometries

A and y have been discussed with (1) and (2). If A is negli- gible compared to a’ (5) and (6) become

R. = ’ a/(s + a )

R. = PY 1 - [gs/(s + a)]

(cellular geometries).

As expected, the denominator of (7) or (8) is the ratio of area outside the well to total cell area, as shown in Fig. 2 .

Fig. 9 plots R j / p y versus s‘/A calculated from ( 5 ) and (6) for linear and cellular geometries with the percentage of neck area as a parameter. As in the case of Repi, all cellular geom- etries result in the same set of curves with less than 0.1 percent difference in values. In other words, for the same s and per- centage of neck area Ri is also the same for all the cellular geometries. Fig. 9 shows that cellular geometries can result in lower Ri than linear geometry at the same s f and percentage of neck area. The asymptotic values of R i / p y when s‘/A is large are predicted by (7) and (8).

111. JFET RESISTANCE IV. ACCUMULATION LAYER RESISTANCE

Contrary to the shape suggested before [4], [ 7 ] , the deple- tion region is absent at the surface and becomes thicker below the surface as shown in Fig. 1 (b). The depletion regicm is largely extended into the n- epi-region because of its lojver doping density than that of the p-well. The “neck” t lus formed between adjacent depletion regions pinches current flow and increases Ri. The region contributing to Ri starts from the surface and ends at the level of the neck (a distuce h$ below the surface). This “JFET” region is a matter of clef- inition and the present definition is adopted for mathemat: cal simplicity.

A trapezoid model is used for the calculation of Ri. For

There is an accumulation layer underneath the gate at the surface of the epi-layers when the device operates in the linear region. Due to the voltage drop along the accumulation layer, the resistance between the end of the channel and the drain at the bottom is larger than the sum of Repi and Ri as calcu- lated by the trapezoid models. There is no simple way to analyze the impact of the accumulation layer on the on-state resistance in general short of employing numerical simulation [7]. However, when the voltage drop along the accumulation is much smaller than that across the entire epilayer (Ra << Ri + Repi), the accumulation layer may be assumed to be an equipotential surface for the calculation of Ri and Repi as was

HU et al . : OPTIMUM DESIGN OF POWER MOSFET’S 1691

W e l l dimension, s (,urn) - Fig. 10. Calculated R,/p , versus s for linear and cellular geometries.

done in Section I11 as well as in all previous studies. As a per- turbation, an additional resistance called the accumulation layer resistance (R,) [ l ] or the depletion-transistor resistance [4] is inserted. Three models have been used to estimate R,. The “constant current density” model [ l ] assumes a constant density of current flowing downward toward the drain from the accumulation layer. With this model, the maximum vol- tage drop along the accumulation iayer can be calculated. R, can then be estimated by dividing this voltage drop by the drain current. For linear geometry

where ps is the surface resistivity of the accumulation layer. C,, is the oxide thickness, pna is the electron mobility in the accumulation layer [14] , and V,, is the flat-band voltage over the n-eiptaxial layer. Another model [4] , based on a transmis- sion line analysis, predicts for the linear geometry

R, = - (s t a)a. Ps 12

The third model [lo] uses (10) when a/2 is smaller than I, the characteristic attenuation length of the current flowing in the accumulation layer; and, when a/2 is larger than this length, assumes the current t o be uniformly distributed with a band, whose width is equal to I , around the well peripheral. The constant-current-density assumption of ti:: .c model is con- sistent with the Ri and Repi models and can be easily applied to some cellular geometries. The same cannot be said for the “transmission-line” models. In this paper we adopt the first model. The first two models are accurate only when a/2 is smaller than 1, i.e., R, << Ri + Repi, a condition that can be easily checked (see Fig. 12 below). This condition appears to be satisfied by most optimized designs [ 101.

Using the constant-current-density model, it can be shown that, for the square-well-in-square-cell design and the hexa- gonal-well-in-hexagonal-well design

x ” t

0% 20% 40% 60% 80% 100% percentage of cell area outside wel l

Fig. 11. Channel width per unit area (multiplied by s) versus the per- centage of cell area that is outside the welL

centage is given by the formula in Fig. 2. Other cellular geom- etries lack symmetry and their R,’s assume more complex functional forms. Equation (1 1) or Fig. 10 will be used as a good approxima.tion for all cellular designs.

V. CHANNEL RESISTANCE The channel resistance is

where Z is the channel width per unit area, pni is the electron mobility in the inversion layer, V, is the threshold vohge, and L is the channel length. The channel width per unit area, Z can be shown to be

Z = 2/(s t a) (linear geometry) (1 3)

z = 4gas/(s t (cellular geometries). (14)

In (14), the channel width is taken to be the circumference of the p-wells. This assumption is satisfactory when the chan- nel length is much smaller than the well dimension s, although more accurate formulae for Rck can be derived if desired.

Fig. 11 shows the product of s and the channel width per unit area versus the percentage of cell outside well. The linear geometry results in exactly one half of the channel width per unit area of the cellular geometries at the same s and percen- tage of cell area outside the weli.

VI. TOTAL ON-STATE RESISTANCE The total on-state resistance, R,, is simply the sum of Repi,

Ri, R,, and Rch, which can be individually calculated as de- scribed in the previous sections. An example is shown in Fig. 12. Note that the broken curves are universally applicable to all the cellular geometries illustrated in Fig. 2. Ron is mini- mized at a certain ratio of neck area to cell a.rea. For the set of parameters assumed, this ratio is about 63 percent. T h s ratio corresponds to a particular well spacing a for each cellu- lar cell geometry according to the formula in Fig. 2. The top horizontal scale in Fin. 12 indicates that the optimal well -

4 = PS . (S + a)’ . [(s + In (1 + 4) - as - $1 spacing for square-well-in-square-cell and hexagonal-well-in- 8 a(a + 2s) hexagonal-cell designs is about 19 pm. At this optimal well -

spacing R, is indeed much smaller than Ri + Repi as assumed in (’ Section V. The minimum Ron of the linear-geometry MOSFET ps is defined in (9). Fig. 10 plots R,/p, versus s with the per- is higher than the minimum Ron of ce:llular MOSFET’s having centage of cell area outsnde the well as a parameter. This per- the same well width, s.

1698 IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. ED-31, NO. 12, DECEMBER 1984

w e l l s p a c i n g , a ( p m ) square In hexagon

hexagon In hexagon- 8.7 or

linear cell- 20 17.4 37.1

- 8 0 E

c - 60 E

8 2

$ 4 0

l

c v)

v1

t 1

R a t i o o f neck orea to cel l ore0

Fig. 12. An example showing the Ron's and their components f o r lin- ear and all cellular designs. See Section VI1 for the other pararn{:ters used.

hexaqonal well in hexagonal Cell square well In square cell or

\ W = 5 5 p m P = 0 . 9 n c m

W 1 = 5 . 5 @ m

I , I I I I ? . .

3 4 5 6 7 8 9 Wel l spac lng, a(pm)

Fig. 13. Ron versus a for two types of cellular cells. Minimum R,, is always smaller a t smaller s for all cell geometries.

An important conclusion from the equations derived her: is that all components of Ron decreases with decreasing well width s for a fixed ratio of a/s. The minimum Ron (at o:,ti- mized Q or area ratio) is thus always smaller for smaller s as shown in Fig. 13.

VII. EXPERIMENTS Power MOSFET's were fabricated and the measured resis-

tances are compared with the theoretical calculations in Fig. 14. All vertical and horizontal dimensions and the epi-la yer resistiviiq were determined using scanning electron microsc:ope and spreadingresistance probe. The agreement between ,:he experiments and the model is good. Specifically, the mod1:l's predictions of the impact of well size s and spacing a onli,,,

200 I I I I

2-square in square / s = 3 5 p m

190 - p = 2 6 i l c m

W = 4 0 p m

A = O 180- W j = 6 p m

lmear ce l l

150-square

140 0 10 20 30 40 50

WELL SPACING a ( p m )

Fig. 14. Experimental and theoretical Ron as a function of well spacing (a), well dimension (s), and cell design (square versus linear).

t w- 200 - E

c: 1 5 3 - E

l

I

0

IL loo;

- a i l cellular geornetrles, t heo ry

0' square well m square cel l 0 : square wel l in hexagonal ce l l

t # 3

percentage of cell area outslde wel l

2 0 Y o 40 % 60 % 80 %

Fig. 15. Experimental and theoretical Ron. The theoretical curve ob- viously applied to these two cellular geometries and is expected to apply to all the cellular geometries listed in Fig. 2.

and the difference between square and linear cell designs are verified. Other parameters used are L = 2 pm, Cox = 3.5 X 1 O-' f/cm2, V, - V, = 7 V, pn 700 cm2/s . V in the inversion layer and 1050 cm2/s . V in the accumulation layer [14],

Similar data of Ron is plotted against the percentage of cell area outside the well in Fig. 15. When plotted in this way, the theoretical curve should apply to all the cellular cell geom- etries. Here, it obviously does apply to the two geometries studied experimentally: square-well-in-square-cell and square- well-in-hexagonal-cell.

VIII. A DESIGN PROCEDURE Based on the on-resistance model presented here, we propose

a simple procedure for design and optimization. First, let us review the optimization of W and p.

The minimization of the ideal n- epitaxial layer resistance ( ( 2 ) ) for a given desired breakdown voltage VB has been ana- lyzed before [l] . Assuming a uniform doping level in the n- epi-layer, the optimum doping level Nd, the thickness W , and the resistivity p are

HU k t a l . : OPTIMUM DESIGN OF POWER MOSFET’S 1699

cell area outside the well, 0 1 1 cel lular cel ls

1101 , ’ 0% 30% 50% 70% 80%

I

90 -

eo ~

.I 50 - E . C E 4 0 - I

VI - a 30-

j0l 10

S = 3 4 p W,= 5.5pm I

P = 2 . l n c m

O h 0 IO 20 30 40 50

Well Spacing, a (pm), square well In squall cell or hexagonal well In hexagonal cell

Fig. 16. Examples of the last step in the optimization of cell design: to determine the well spacing that minimizes ROm The three curves are roughly for V, = 450, 200, and 100 V, respectively.

where E, is the critical ‘breakdown field of silicon, E is the permittivity of silicon, pn is the bulk electron mobility in the n- epi-layer. The critical electric field E, is a slowly varying function of V, such as E, = 8.52*105 VB-o.2V/cm [15]. pn is also a slowly varying function of Nd and hence of V, such as pn = 710*VB0*1 cm2/s * V. These values are acceptable in the breakdown voltage range of 100-1000 V. Therefore, (15)- (17) can be rewritten as

Nd = 1.935 . 10’’ ’ v ~ . - ~ ’ ~ Cm-3 (1 8)

W = 1.74 lo-’ . VB1*’ cm (1 9)

p = 4.55 . 1 0 - ~ V, l a 3 CL cm. (20)

Following are the steps of the proposed design/optimization procedure.

1) Choose W and p according to (19) and (20) for the de- sired breakdown voltage. Allow appropriate safety margins as (19) and (20) were derived for the breakdown of planar junctions.

2 ) Choose the minimum oxide thickness and L (in order to minimize Rch) and W j (in order to minimize Ri) that are consistent with manufacturing technology. (One also needs to meet the V, and punchthrough requirements [16] and

Choose the space that minimizes Ron. Some examples are shown in Fig. 16.

6 ) Prepare photomasks. Fine tune W and p by experimen- tation.

IX. DISCUSSIONS AND CONCLUSIONS A model of Ron for both linear and cellular MOSFET’s is

presented and shown to agree well with experiments. The model consists of four simple analytic functions for the four components of resistance. The most novel and critical part of the model is a 4S0-spreading-angle model for the calculation of spreading resistance. It agrees well with conformal-mapping solutions and 3-D simulations.

The best achievable Ron is a monotonic function of the well width, s. The smaller s is, the smaller Ron can be. For the same s, cellular cells can achieve lower Ron than linear cells. An illustration of this conclusion was recently provided by numerical simulations [7]. There are six attractive cellular-cell designs: square, hexagonal, or circular wells placed on square or hexagonal grid, i.e., placed in square or hexagonal unit cells. For the same s (defined in Fig. 2) , all six can achieve the same minimum Ron within one percent or so. Specifically, the square-well-in-square-cell design and the hexagonal-well-in- hexagonal-cell design (the HEXFET) yield identical Ron’s ac- cording to our model. Another theoretical model [lo], however, has found the latter t o yield lower (by up to 10 per- cent) Ron than the former. We must leave the resolution of this discrepancy to future experimental studies. I t is perhaps interesting to note that our conclusions can explain the de facto state of VDMOSFET design: linear designs have given way to cellular cell designs, of which several different types are currently used in commercial products.

Besides providing the formulae for calculating Ron, we have proposed a simple procedure for optimizing power MOSFET designs. Two key steps are to minimize the horizontal and vertical dimensions (s and junction depth) of the p-wells and to theoretically find the spacing between the wells that mini- mize Ron. For the same well width and depth, the various cellular cell geometries achieve essentially the same mini- mum Ron-this happening at the same ratio of well area to cell area but at different well spacings for the different cellular geometries.

This study has emphasized the minimization of Ron for a given chip area or, conversely, the minimization of chip area while meeting a given Ron requirement. Other requirements may require modifications to the simple design procedures proposed here. For example, one may wish to keep the gate input capacitance low as well. The modifications should be straightforward and the Ron models presented here should be a useful part of any design procedures.

consider the effect of p-diffusion resistance on second-break- down [ 171 .) ACKNOWLEDGMENT

3) Choose the minimum well dimension that is consistent The authors wish to thank P. Bacuvier and R. Bregar for with the lithography and etching and diffusion technologies. their comments.

ear geometry may be considered if s, perhaps through clever layout, is at least 1.6 times smaller than the s of cellular &.) [ 11 C. Hu, “A parametric study of power MOSFET’s,” in Record of

I979 IEEE Power Electronics Specialists Con$, pp. 385-395,

4) Choose any cellular cell geometry (see Section IX). (Lin- REFERENCES

5 ) Calculate Ron and plot it against the well spacing, a. 1979.

1.700 IEEE TRANSACTYONS ON ELECTRON DEVICES, VOL. ED-31, NO. 12, DECEMBER 1984

[2] M. Adler and S. R. Westbrook, “Power semiconductor switclling devices,” IEEE Trans. Electron Devices, vol. ED-29, p. 5‘47, 1982.

131 A. A. Tamer, K. Rauch, and J. L. Moll, “Numerical comparisons of DMOS, VMOS, and UMOS power transistors,” IEEE Tr,ws. Electron Devices, vol. ED-30, no. 1, p. 73, Jan. 1983.

I41 S. C. Sun and J. D. Plummer, “Modeling of the on-resistana: 3f LDMOS VDMOS, and VMOS power transistors,” IEEE Tfizns. Electron Dcvices, vol. ED-27, no. 2, p. 356, Feb. 1980.

[SI X. Chen and C. Hu, “Optimum doping profile of power MOWET epitaxial layer,” ZEEE Trans. Electron Devices, vol. ED-29, no. 6, pp. 985-987, June 1982.

[6] V. A. K. Temple, “Ideal FET doping profile,” IEEE Trans. .Elec- tron Devices, vol. ED-30, no. 6, p. 619, June 1983.

[7] K. Board, D. Byrne, and M. S. Towers, “The optimization of on- resistance in vertical DMOS power devices with linear and he::ag- onal surface geometries,” IEEE Trans. Electron Devices, vol. ED-31, no. 1, pp. 75-80, Jan. 1984.

[8] P. L. Hower and M. J. Geisler, “Comparison of various source- gate geometries of power MOSFET’s,” ZEEE Tvans. Electron Devices, vol. ED-28, no. 9, pp. 1098-1101, Sept. 1981.

&9] M-H. Chi and C. Hu, “Some issues of power MOSFETs,” inl!ec- ord of 1982 ZEEE Power Electronics Specialists ConJ, pp. 392- 399,1982.

[ 101 P. L. Hower, T. Heng, and C . Huang, “Optimum design of plDwer MOSFET’s,” inIEDM Tech. Dig., p. 81, 1983.

1111 F. L. Hower, Unitrode Inc., private communication. [I21 S. Kay, C. T. Trieu, and E. H. Yoh, “A new VMOS power FET,”

inZERM Tech. Dig., pp. 97-101, 1979. 131 D. Hu, “A design of power MOSFET with low on-resistarwe,”

Master’s thesis, Dept. of Electrical Engineering and Computer Sciences, University of California, Berkeley, June 1981.

141 S. C. Sun and J. D. Plummer, “Electron mobility in inversion md accumulation layers on thermally oxidized silicon surface,” I6EE Trans. Elechon Devices, vol. ED-27, pp. 1497-1508, 1980.

1-51 S. M. Sze and G. Gibbons, “Avalanche breakdown voltages of abrupt and linearly waded DII iunctions in Ge. Si. GaAs. md GaF,”AppL Phys. Le%, vol. s, p: 111, 1966.

[ I61 C. T. Wang and D. H. Navon, “Threshold and punchthrough be- havior of laterally nonuniformly-doped short-channel M3S- FET’s,” IEEE Trans. Electron Devices, vol. ED-30, no. 7, p. 776, 1983.

[ I71 C. Hu and M-H. Chi, “Second breakdown of vertical ponrer MOSFET’s,” IEEE Trans. Electron Devices, vol. ED-29, no. 8,

I ,

pp. 1287-1239, A u ~ . 1982.

* Chenming Hu (SY71-M’76-SM’83) was born in 1947. He received the B.S. degree from :he National Taiwan University in 1968 and :he M.S. and Ph.D. degrees in electrical engineering Bom the University of California, Berkeley in 1970 and 1973, respectively.

From 1973 to 1976, he was an Assistant PIO- fessor at the Massachusetts Institute of Techr ol- ogy. In 1976, he joined the University of California, Berkeley, where he is a Professor of electrical engineering and computer scient es.

Since 1973, he has served as a consultant to the electronics industry. On leave from the University in 1980-1981, he was manager of non- volatile memory development at National Semiconductor. He has conducted research on semiconductor devices and materials, electro- optics, solar cells, and power electronics. His present research areas include advanced IC technologies, VLSI devices, and power semicon- ductor devices. He has authored or coauthored one book and over 100 research journal articles.

*

*

Vikram M. Pate1 received the B.S. degree in electrical engineering from Gujarat University, Ahmedabad, India in 1967 and the M.S. degree from Stevens Institute of Technology, Hoboken, NJ in 1969.

In 1969, he joined Transition Electronics Corporation in Wakefield, MA where he worked as Process/Product Engineer for small signal and power transistor. He joined Fairchild Semicon- ductor, Mt. View in 1973 as Design/Device Engineer where he developed several switch-

mode transistors for switching applications and power Darlington traa- sistor for automobile ignition application. He held various engineering management positions during his nine years with Fairchild. He joined Avantek inc., Santa Clara in 1983, where he is Product Engineering Manager for Semiconductor Division manufacturing silicon and Galium Arsenide high frequency devices.