Nanoelectrochemical Switch for Programmable logic...32x32 programmable cells based on standard cell...

Transcript of Nanoelectrochemical Switch for Programmable logic...32x32 programmable cells based on standard cell...

1

Nanoelectrochemical Switch for

Programmable logic

Toshitsugu SAKAMOTO Low-power Electronics Association & Project (LEAP)

2nd Symposium for Energy Efficient Electronic Systems , 2011

2

Resistive switch technology using electrochemical reaction

Two terminal atom switch

Three terminal atom switch

Programmable cell arrays using atom switches

Performance gap between FPGA and ASIC

Chip size and power reduction

Conclusions

Outline

3

Ag atom precipitates when positive voltage is biased on Ag.

Formation and annihilation of atomic bridge changes

conductance in units of 2e2/h.

Atomic Switch with nanometer gap

+200

+100

+80

-260mV

Co

nd

ucta

nce

(2e

2/h

)sequence

K.Terabe, et al., REKEN Review 37, 7 (2001)

K.Terabe, et al., Nature 433, 47 (2005)

RT

Ag

Pt

Ag

Switch Off Switch On

Ag2S

4 Two-terminal Atom Switch

Anode voltage (V) -0.2 0 0.2

10-12

10-10

10-8

10-6

10-4

10-2

Ab

so

lute

cu

rre

nt (A

)

OFF

(Reset)

ON

(SET)

ON

OFF

Appl. Phys. Lett. 82, 3032 (2003)

Anode

Cathode

5 Three terminal Atom Switch

ON

OFF

Appl. Phys. Lett. 96, 252104 (2010)

Gate voltage, VG (V)

Cur

rent

(A

)

-0.2 -0.1 0 0.1 0.210-11

10-10

10-9

10-8

10-7

10-6

10-5

10-4

IG

ID

1mGate(Cu)

Drain(Pt)

Source(Ru)

Cu2S

Gate

Drain

6 Electrochemical switch in liquid (Triode)

OFF ON

Electrolyte (CuSO4 aq.)

Gate(Cu)

Drain (Pt)

Source (Pt)

S/D : Cu+ + e- → Cu

Gate : Cu → Cu+ + e-

7 Cycle endurance

VG=0V, VD=10mV, RT

ON

OFF Dra

in c

urr

ent, I

D (

A)

Cycle0 50 100

10-12

10-10

10-8

10-6

10-4

10-2

Appl. Phys. Lett. 96, 252104 (2010)

8

Issues

Thermal robustness of Cu2S

Process compatibility

2/3 terminal comparison

2 terminal 3 terminal

Ionic condutor Cu2S Cu2S

Integration - -

ON/OFF ratio 106 106

Cycling endurance 104 102

Switching voltage 0.1-0.2V 0.1-0.2V

Switching time ~1usec -

Switching current 1mA < 2uA

Retention 3 months -

Oxide ionic-conductor

9

Appropriate materials for Si LSI

Ionic conductor : Oxide

Inert electrode : Ru

Active electrode : Cu interconnect

Simple structure

Only two additional mask needed

Implemented in BEOL

M1

M2

M3

M4

M5

switch

90nm CMOS

M.Tada et al., IEEE IEDM (2010)

10 IV characteristics

M.Tada et al., IEEE IEDM (2010)

11 Origin of current path

Resistive switching is attributed to formation of Cu bridge.

Pt

Cu Ta2O5

B

HSQ

A

40nm 0 0

Si/Ta Cu

O

Pt

Cu/Ta Cu

Ta/Pt

10 2 4 6 8 Energy (keV)

Inte

nsity (

a.u

.)

A

B

Element analysis by EDX before turning ON

after turning ON

Appl. Phys. Lett. 91, 092110 (2007)

12 32x32 Xbar switch

Cell-select transistors are placed at each lines (32x2)

(not at each cells- 32x32).

VP applied to programmed cell and 0 or 1/2VP to the others.

VP 1/2VP 1/2VP 1/2VP

0

1/2VP

1/2VP

1/2VP

M.Miyamura, et al.,IEEE ISSCC (2011)

13 Programmability of Xbar

z Re-programming

X: Signal input

Y:

Sig

na

l o

utp

ut

X: Signal input

Y:

Sig

na

l o

utp

ut [Ω]

1e10

1e9

1e8

1e7

1e6

1e5

1e4

1e3

1e2

M.Miyamura et al.,IEEE ISSCC (2011)

14 Switching time

M.Tada et al., IEEE IEDM (2010)

15 Switch comparison

3 terminal 2 terminal

Cu2S Cu2S Oxide

Integration - - OK

ON/OFF ratio 106 106 106

Cycling endurance 102 104 104

Switching voltage 0.1-0.2V 0.1-0.2V 2-5V

Switching time - ~1usec 10nsec

Switching current 0.1uA 1mA 1mA

Retention - 3 months 10years

16

Application of atom switch

17 Taxonomy of Nonvolatile memory

Mature

Prototype

Emerging

Charge state Resistive state Magnetic state

STT RAM

PRAM

(Phase change)

ReRAM

- O-vacancy

- Metallic-Bridge

MRAM

(Magnetic Field)

NAND flash

NOR flash

(Floating gate)

SONOS/TANOS

(Charge Trap)

BEOL device

(Atom switch)

18 ON/OFF conductance ratio & Trade-off

Cycle Endurance

ON

/OF

F r

ati

o

NOR Switch

ReRAM

10 0 10 2 10 4 10 6 10 8 10 10 >10 16

10 0

10 2

10 4

10 6

10 8

MRAM

SRAM

19 Switch application

Advantages

Large ON/OFF resistance ratio

BEOL process +2PR

Switch size

Nonvolatile

Issues for programmable switch

Reliability /Switching model

SET/RESET current (~0.5mA)

SET voltage (~3.5V)

Variability

Programmable switch

20

Requirements for switch application

ON state reliability : pulsed AC current (50uA p-p)

OFF state reliability : DC voltage (1V)

10 years, 105ºC, 0.1%TTF(time to failure)

Reliability requirements for switch

21 ON state reliability & Trade-off

GON = 5 IReset

Switching current

(ISet or IReset)

ON conductance

(GON)

Allowable current

(IMAX)

Imax = 1.4x10-2 GON

Imax = 0.7x10-2 IReset

@0.1%TTF, 10year, 105oC

0.5mA

2.5mS (400Ω) 37uA@DC

N. Banno, et al., IEEE VLSI Symp., 115 (2010)

22 OFF state reliability & Trade-off

Set voltage

(VSET)

Allowable voltage

(VMAX)

VSET ≈ 3.5V

M.Tada et al., IEEE IEDM (2010)

23

Programmable cell arrays

24

ASIC (Cell based ASIC)

FPGA (Field Programmable Gate Array)

Fixed logic cells

& interconnection

Reconfigurable logic cells

& interconnection

ASIC vs FPGA

Circuit design (HDL)

Mask

Si chip production

Layout (CAD)

Circuit design (HDL)

Buy FPGA and Program it!

Short lead time

Low NRE

Logic

Cell

Logic

Cell

Logic

Cell

Logic

Cell

Logic

Cell

Logic

Cell

Logic

Cell

Logic

Cell

Pro

du

cti

on

flo

w

Str

uc

ture

Small chip

High performance

Large chip

Fair performance

Long lead time

High NRE

25

Time to Market

low developing cost or NRE (non-recurring engineering) cost

NRE for ASIC > 10M$

Performance gap

Area

Delay

Dynamic Power

SRAM issues

Increasing static power

Variability

Advantage / Disadvantage of FPGA

Net SalesAltera + Xilinx

Net

Sal

es (

bill

ion

$)

Year1996 2000 2004 2008

0

1

2

3

4

(Ref. Annual Rep.)

We accept gap & issues.

26

Reduced area to program connection

Non-volatility

Essence to narrow the gap

27 Switch over Logic

Sea of switches

Logic Cell

Logic Cell

Logic Cell

Logic Cell

Logic plane

Switch plane

Proposal Conventional FPGA

SRAM cell Pass tr. wire

SRAM switch Nonvolatile SW

Area:120F2 4F2

Small Cell

(>102F2) Large Cell

(>104F2)

Size:1/10

28

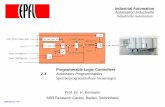

32x32 programmable cells based on standard cell design

(for reference)

MUX for configurable switch

Programmable logic using CMOS switch

32 x 32

programmable cell

array

Drivers and I/O buffers

M.Miyamura et al.,IEEE ISSCC (2011)

by courtesy of M.Miyamura, NEC

29

Logic cell

350,000 atom switches replace MUX

72% chip area reduction

70% dynamic power reduction

Programmable cell using atom switches

32 x 32

programmable cell

array

Drivers and I/O buffers

32 x 32 cell

array

Driver & I/O

Dri

ver

& I/O

switch

logic

M.Miyamura et al.,IEEE ISSCC (2011)

by courtesy of M.Miyamura, NEC

30

Nonvolalilty reduces Static Power.

Small capacitance of switch or interconnection reduce

dynamic power.

Reduction in power consumption

PINT f (CINT + CSW + C0 )

Wire length

Interconnect

M.Miyamura et al.,IEEE ISSCC (2011)

Pst

0 5 10 15 20 0

5

Dyn

am

ic

P [

mW

]

MUX base

AtomSW

Operational frequency (MHz)

~1/2 ~1/10

31

Boosts performance & functionality of Si chip

Does not affect CMOS integration & properties

Concept of BEOL Device

FE

OL

B

EO

L

45nm 32nm 22nm 15nm 11nm

Technology Node

No

. T

ran

sis

tors

/ C

hip

P

erf

orm

an

ce

, F

un

cti

on

ality

More than Moore

More Moore

BEOL devices

boost performance.

FEOL

BEOL device

32 Research consortium : LEAP

MRAM

Objective :

“Ultra low voltage device for Low-carbon society”

Member companies :

Ebara, Fujitsu, Fujitsu Semiconductor, Hitachi Kokusai Electric,

Hitachi, Mitsubishi Electric Corp, NEC Corp., Renesas Electronics

Corp., Tokyo Electron Ltd., Toshiba Corp.

PRAM CNT Via

Atom Switch

BEOL

• Shared test chip

• 65nm CMOS Logic

FDFET(SOTB)

33

Three terminal atom switch reduces the programming

current dramatically.

Two-terminal atom switch successfully embedded into a Cu

interconnect with two additional masks.

Novel switch improves performances of reconfigurable LSI

without scaling down.

72% reduction in chip size

70% reduction in dynamic power

Conclusions

34

Munehiro Tada (LEAP)

Makoto Miyamura

Naoki Banno

Koichi Okamoto

Noriyuki Iguchi

Hiromitsu Hada

Acknowledge