Msi interrupt reception as EP. Msi debug Based on sprugs6a.pdf, Keystone architecture Perpheral...

-

Upload

lesley-lamb -

Category

Documents

-

view

215 -

download

0

Transcript of Msi interrupt reception as EP. Msi debug Based on sprugs6a.pdf, Keystone architecture Perpheral...

Msi interrupt reception as EP

Msi debug

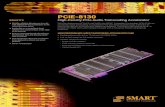

• Based on sprugs6a.pdf, Keystone architecture Perpheral Component Interconnect Express (PCIe)

• wrote 8 into MSI_IRQ (0x218000)

• MSI_EN is set in pcie_msi_cap (0x21801000+0x50)

• MSI0_IRQ_STATUS (0x21800104) is updated with 3 matching 8 in MSI_IRQ

• So the forced interrupt is detected by PCIe_MSI

HWI set up

• Configured the following in cfg, match the c-code in wiki

var hwi0Params = new Hwi.Params();hwi0Params.instance.name = "pcie_msi_core0";hwi0Params.eventId = 17;hwi0Params.priority = 3;Program.global.pcie_msi_core0 = Hwi.create(5, "&pcie_msi_isr", hwi0Params);

• Based on table 7-33 in TMS320c6657, event number 17 is PCIE_MSI_INTn (for core 0, it would be PCIE_MSI_INT0)

• In func pcie_msi_isr, there is counter and break point is not hit after writing into the MSI_IRQ register

• We plan to dedicate interrupt 5 for PCIe interrupt. We therefore do not have to use EventCombiner, right?

• It is expected all the enabling and matching is setup

• In func pcie_msi_isr, there is counter and break point is not hit after writing into the MSI_IRQ register

• Do we miss anything here?

Interrupt debugIER/IFR

• In CCS 5, under view/registers/control registers

• IE05 in IER is enabled, but IF5 in IFR is still 0

INTC registers

• In ccs5, under registers, we have INTC0, INTC1 and INTC2

• Does this mean that MSI_INTn is one of the 106 primary event to core 0 without going through INTC0?

• How do I match the interrupt with CIC0?

• Is there a specific enabling bit and status bit for event 17? If it is, where can I see it?