LT3434 Step-Down Switching Regulator with 100µ · The LT®3434 is a 200kHz monolithic buck...

Transcript of LT3434 Step-Down Switching Regulator with 100µ · The LT®3434 is a 200kHz monolithic buck...

LT3434

13434fb

APPLICATIO SU

FEATURES

TYPICAL APPLICATIO

U

DESCRIPTIO

U

High Voltage Power Conversion 14V and 42V Automotive Systems Industrial Power Systems Distributed Power Systems Battery-Powered Systems

Wide Input Range: 3.3V to 60V 3A Peak Switch Current Burst Mode® Operation: 100µA Quiescent Current** Low Shutdown Current: IQ < 1µA Power Good Flag with Programmable Threshold Load Dump Protection to 60V 200kHz Switching Frequency Saturating Switch Design: 0.1Ω Peak Switch Current Maintained Over

Full Duty Cycle Range* 1.25V Feedback Reference Voltage Easily Synchronizable Soft-Start Capability Small 16-Pin Thermally Enhanced TSSOP Package

High Voltage 3A, 200kHzStep-Down Switching Regulator

with 100µA Quiescent Current

The LT®3434 is a 200kHz monolithic buck switchingregulator that accepts input voltages up to 60V. A highefficiency 3A, 0.1Ω switch is included on the die along withall the necessary oscillator, control and logic circuitry.Current mode topology is used for fast transient responseand good loop stability.

Innovative design techniques integrated in a new highvoltage process achieve high efficiency over a wide inputrange. Efficiency is maintained over a wide output currentrange by employing Burst Mode operation at low currents,utilizing the output to bias the internal circuitry, and byusing a supply boost capacitor to fully saturate the powerswitch. Patented circuitry maintains peak switch currentover the full duty cycle range.* Shutdown reduces inputsupply current to less than 1µA. External synchronizationcan be implemented by driving the SYNC pin with logic-levelinputs. A single capacitor from the CSS pin to the outputprovides a controlled output voltage ramp (soft-start). Thedevice also has a power good flag with a programmablethreshold and time-out, and thermal shutdown protection.

The LT3434 is available in a 16-pin TSSOP package withExposed Pad leadframe for low thermal resistance.

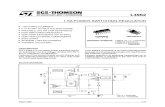

14V to 3.3V Step-Down Converter with100µA No Load Quiescent Current

Efficiency and Power Lossvs Load Current

LOAD CURRENT (A)0.00010

EFFI

CIEN

CY (%

)

25

0.001 0.01 0.1 1

3434 TA02b

100

50

75

0.001

POWER LOSS (W

)

0.01

10

0.1

1

10

TYPICAL POWERLOSS

EFFICIENCY

VIN = 12VVOUT = 5V

VOUT = 3.3V

Supply Current vsInput Voltage

INPUT VOLTAGE (V)0

0

SUPP

LY C

URRE

NT (µ

A)

50

100

10 20 30 40

3434 TA02a

50

150

25

75

125

60

VOUT = 3.3V

VIN

SHDN

VCVBIAS

FB

PGFB

PG

LT3434

4.7µF100VCER

470pF

0.68µF

0.1µF

33µH 4148

1µF SYNCCT

GND

100µF6.3VTANT

VOUT3.3V2A

VIN

30MQ100

4700pF

10k165k1%

100k1%

3434 TA01

27pF

SW

BOOST

CSS

, LTC and LT are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Burst Mode is a registered trademark of Linear Technology Corporation. *Protected by U.S. Patents including 6498466. **See Burst Mode Operation section for conditions.

LT3434

23434fb

(Note 1)VIN, SHDN, BIAS, PGOOD, SW ............................... 60VBOOST Pin Above SW ............................................ 35VBOOST Pin Voltage ................................................. 68VSYNC, CSS, PGFB, FB ................................................ 6VOperating JunctionTemperature Range

LT3434EFE (Note 2) ........................ – 40°C to 125°CLT3434IFE (Note 2) ......................... – 40°C to 125°C

Storage Temperature Range ................. –65°C to 150°CLead Temperature (Soldering, 10 sec).................. 300°C

ORDER PARTNUMBER

Consult LTC Marketing for parts specified with wider operating temperature ranges.

LT3434EFELT3434IFE

ABSOLUTE AXI U RATI GS

W WW U

PACKAGE/ORDER I FOR ATIOU UW

ELECTRICAL CHARACTERISTICS The denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at TJ = 25°C. VIN = 12V, SHDN = 12V, BIAS = 5V, FB/PGFB = 1.25V,CSS/SYNC = 0V unless otherwise noted.

TJMAX = 125°C, θJA = 45°C/W, θJC(PAD) = 10°C/W

EXPOSED PAD IS GND (PIN 17)MUST BE SOLDERED TO GND (PIN 8)

Order Options Tape and Reel: Add #TRLead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBFLead Free Part Marking: http://www.linear.com/leadfree/

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

VSHDN SHDN Threshold 1.15 1.3 1.45 V

ISHDN SHDN Input Current SHDN = 12V 5 20 µA

Minimum Input Voltage (Note 3) 2.4 3 V

IVINS Supply Shutdown Current SHDN = 0V, BOOST = 0V, FB/PGFB = 0V 0.1 2 µA

Supply Sleep Current (Note 4) BIAS = 0V, FB = 1.35V 170 250 µAFB = 1.35V 45 75 µA

IVIN Supply Quiescent Current BIAS = 0V, FB = 1.15V 3.2 6 mABIAS = 5V, FB = 1.15V 2.6 5 mA

Minimum BIAS Voltage (Note 5) FB = 1.15V 2.7 3.1 V

IBIASS BIAS Sleep Current (Note 4) 110 180 µA

IBIAS BIAS Quiescent Current SYNC = 3.3V 700 900 µA

Minimum Boost Voltage (Note 6) ISW = 3A 1.8 V

Input Boost Current (Note 7) ISW = 3A 65 85 mA

VREF Reference Voltage (VREF) 3.3V < VVIN < 60V 1.225 1.25 1.275 V

IFB FB Input Bias Current 75 200 nA

EA Voltage Gain (Note 8) 900 V/V

EA Voltage gm dI(VC)= ±10µA 400 650 900 µMho

EA Source Current FB = 1.15V 20 40 55 µA

EA Sink Current FB = 1.35V 15 30 40 µA

VC to SW gm 6 A/V

FE PARTMARKING

3434EFE3434IFE

FE PACKAGE16-LEAD PLASTIC TSSOP

1

2

3

4

5

6

7

8

TOP VIEW

16

15

14

13

12

11

10

9

NC

SW

VIN

VIN

SW

BOOST

CT

GND

PGOOD

SHDN

SYNC

PGFB

FB

VC

BIAS

CSS

17

LT3434

33434fb

ELECTRICAL CHARACTERISTICS The denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at TJ = 25°C. VIN = 12V, SHDN = 12V, BIAS = 5V, FB/PGFB = 1.25V,CSS/SYNC = 0V unless otherwise noted.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

VC High Clamp FB = 1.15V 2.1 2.2 2.4 V

IPK SW Current Limit 3 4.7 6.5 A

Switch On Resistance (Note 9) 0.1 0.25 Ω

Switching Frequency 180 200 230 kHz

Maximum Duty Cycle 90 92 %

Minimum SYNC Amplitude 1.5 2.0 V

SYNC Frequency Range 230 500 kHz

SYNC Input Impedance 45 kΩICSS CSS Current Threshold (Note 10) FB = 0V 7 13 20 µA

IPGFB PGFB Input Current 25 100 nA

VPGFB PGFB Voltage Threshold (Note 11) 88 90 92 %

ICT CT Source Current (Note 11) 2 3.6 5.5 µA

CT Sink Current (Note 11) 1 2 mA

VCT CT Voltage Threshold (Note 11) 1.16 1.2 1.26 V

PG Leakage (Note 11) 0.1 1 µA

PG Sink Current (Note 11) PGFB = 1V, PG = 400mV 120 200 µA

Note 1: Stresses beyond those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. Exposure to any AbsoluteMaximum Rating condition for extended periods may affect devicereliability and lifetime.Note 2: The LT3434EFE is guaranteed to meet performance specificationsfrom 0°C to 125°C junction temperature. Specifications over the –40°C to125°C operating junction temperature range are assured by design,characterization and correlation with statistical process controls. TheLT3434IFE is guaranteed and tested over the full –40°C to 125°Coperating junction temperature range.Note 3: Minimum input voltage is defined as the voltage where switchingstarts. Actual minimum input voltage to maintain a regulated output willdepend upon output voltage and load current. See ApplicationsInformation.Note 4: Supply input current is the quiescent current drawn by the inputpin. Its typical value depends on the voltage on the BIAS pin and operatingstate of the LT3434. With the BIAS pin at 0V, all of the quiescent currentrequired to operate the LT3434 will be provided by the VIN pin. With theBIAS voltage above its minimum input voltage, a portion of the totalquiescent current will be supplied by the BIAS pin. Supply sleep current isdefined as the quiescent current during the “sleep” portion of Burst Modeoperation. See Applications Information for determining application supplycurrents.

Note 5: Minimum BIAS voltage is the voltage on the BIAS pin when IBIAS issourced into the pin.Note 6: This is the minimum voltage across the boost capacitor needed toguarantee full saturation of the internal power switch.Note 7: Boost current is the current flowing into the BOOST pin with thepin held 3.3V above input voltage. It flows only during switch on time.Note 8: Gain is measured with a VC swing from 1.15V to 750mV.Note 9: Switch on resistance is calculated by dividing VIN to SW voltage bythe forced current (3A). See Typical Performance Characteristics for thegraph of switch voltage at other currents.Note 10: The CSS threshold is defined as the value of current sourced intothe CSS pin which results in an increase in sink current from the VC pin.See the Soft-Start section in Applications Information.Note 11: The PGFB threshold is defined as the percentage of VREF voltagewhich causes the current source output of the CT pin to change fromsinking (below threshold) to sourcing current (above threshold). Whensourcing current, the voltage on the CT pin rises until it is clampedinternally. When the clamp is activated, the output of the PG pin will be setto a high impedance state. When the CT clamp is inactive the PG pin willbe set active low with a current sink capability of 200µA.

LT3434

43434fb

TYPICAL PERFOR A CE CHARACTERISTICS

UW

FB Voltage Oscillator Frequency SHDN Threshold

SHDN Pin Current Shutdown Supply Current Sleep Mode Supply Current

Bias Sleep Current

1.20

VOLT

AGE

(V)

1.21

1.23

1.24

1.25

1.30

1.27

1.22

1.28

1.29

1.26

TEMPERATURE (°C)–50 0 50 75

3434 G01

–25 25 100 125TEMPERATURE (°C)

–50150

FREQ

UENC

Y (k

Hz)

160

180

190

200

250

220

0 50 75

3434 G02

170

230

240

210

–25 25 100 125

VOLT

AGE

(V)

1.35

3434 G03

1.20

1.10

1.05

1.00

1.40

1.30

1.25

0.15

TEMPERATURE (°C)–50 0 50 75–25 25 100 125

SHDN VOLTAGE (V)0

0

CURR

ENT

(µA)

1.5

2.5

3.5

10 20 30 40

3434 G04

50

4.5

5.5

1.0

2.0

3.0

4.0

5.0

60

TJ = 25°C

CURR

ENT

(µA)

3434 G05

20

10

5

0

25

15

TEMPERATURE (°C)–50 0 50 75–25 25 100 125

VIN = 60V

VIN = 42V VIN = 12V

CURR

ENT

(µA)

3434 G06

160

80

40

0

200

120

140

60

20

180

100

VBIAS = 0V

VBIAS = 5V

TEMPERATURE (°C)–50 0 50 75–25 25 100 125

CURR

ENT

(µA)

3434 G07

160

80

40

0

200

120

140

60

20

180

100

TEMPERATURE (°C)–50 0 50 75–25 25 100 125

PGFB Threshold

VOLT

AGE

(V)

3434 G08

1.16

1.08

1.04

1.00

1.20

1.12

1.14

1.06

1.02

1.18

1.10

TEMPERATURE (°C)–50 0 50 75–25 25 100 125

PG Sink Current

CURR

ENT

(µA)

3434 G09

200

100

50

0

250

150

TEMPERATURE (°C)–50 0 50 75–25 25 100 125

LT3434

53434fb

TYPICAL PERFOR A CE CHARACTERISTICS

UW

Switch Peak Current LimitSoft-Start Thresholdvs FB Voltage

Oscillator Frequencyvs FB Voltage

TEMPERATURE (°C)–50

3.0

3.5

4.0

PEAK

SW

ITCH

CUR

RENT

(A)

4.5

5.0

5.5

6.0

–25 –0 25 50

3434 G10

75 100 125FB VOLTAGE (V)

00

CURR

ENT

(µA)

10

20

30

0.2 0.4 0.6 0.8

3434 G11

1.0

40

50

5

15

25

35

45

1.2

SOFT-STARTDEFEATED

TJ = 25°C

FB VOLTAGE (V)0

0

FREQ

UENC

Y (k

Hz)

50

100

150

0.2 0.4 0.6 0.8

3434 G12

1.0

200

250

1.2

TJ = 25°C

Switch On Voltage (VCESAT)

LOAD CURRENT (A)0.5

0

VOLT

AGE

(mV)

50

150

200

250

500

350

1.5 2.5

3434 G13

100

400

450

300

1.0 2.0 3.0

TJ = 125°C

TJ = 25°C

TJ = –40°C

INPUT VOLTAGE (V)0

0

SUPP

LY C

URRE

NT (µ

A)

50

100

10 20 30 40

3434 G20

50

150

25

75

125

60

VOUT = 3.3V

Supply Current vs Input Voltage

LOAD CURRENT (A)0

3.0

INPU

T VO

LTAG

E (V

)

3.5

4.5

5.0

5.5

2.0

7.5

3434 G19

4.0

1.00.5 2.51.5 3.0

6.0

6.5

7.0

START-UP

VOUT = 5V

VOUT = 3.3V

RUNNING

START-UPRUNNING

Minimum Input Voltage

Burst Mode Threshold vs InputVoltage

Minimum On Time for ContinuousMode Operation Boost Current vs Load Current

INPUT VOLTAGE (V)5

0

LOAD

CUR

RENT

(mA)

100

300

500

10 15

3434 G21

700

900

200

400

600

800

20

BURST MODE EXIT(INCREASING LOAD)

BURST MODE ENTER(DECREASING LOAD)

VOUT = 3.3VL = 33µHCOUT = 100µF

TEMPERATURE (°C)–50

200

ON T

IME

(ns)

650

700

550

600

450

400

350

300

250

500

–25 –0 25 50

3434 G22

75 100 125

LOAD CURRENT = 0.5A

LOAD CURRENT = 1A

LOAD CURRENT = 2A

SWITCH CURRENT (A)0

0

BOOS

T CU

RREN

T (m

A)

10

20

30

40

60

0.5 1.0 1.5 2.0

3434 G23

2.5 3.0

50

LT3434

63434fb

UUU

PI FU CTIO SNC (Pin 1): No Connection.

SW (Pins 2, 5): The SW pin is the emitter of the on-chippower NPN switch. This pin is driven up to the input pinvoltage during switch on time. Inductor current drives theSW pin negative during switch off time. Negative voltageis clamped with the external catch diode. Maximum nega-tive switch voltage allowed is –0.8V.

VIN (Pins 3, 4): This is the collector of the on-chip powerNPN switch. VIN powers the internal control circuitry whena voltage on the BIAS pin is not present. High dI/dt edgesoccur on this pin during switch turn on and off. Keep thepath short from the VIN pin through the input bypasscapacitor, through the catch diode back to SW. All trace

inductance on this path will create a voltage spike at switchoff, adding to the VCE voltage across the internal NPN.

BOOST (Pin 6): The BOOST pin is used to provide a drivevoltage, higher than the input voltage, to the internalbipolar NPN power switch. Without this added voltage, thetypical switch voltage loss would be about 1.5V. Theadditional BOOST voltage allows the switch to saturateand its voltage loss approximates that of a 0.1Ω FETstructure.

CT (Pin 7): A capacitor on the CT pin determines the amountof delay time between the PGFB pin exceeding its thresh-old (VPGFB) and the PG pin set to a high impedance state.When the PGFB pin rises above VPGFB, current is sourced

No Load 2A Step Response Step Response

TYPICAL PERFOR A CE CHARACTERISTICS

UW

Burst Mode Operation

Burst Mode Operation

VOUT50mV/DIV

IOUT500mA/DIV

VIN = 12V 5ms/DIV 3434 G14

VOUT = 3.3VIQ = 100µA

VOUT50mV/DIV

IOUT500mA/DIV

VIN = 12V 5µs/DIV 3434 G15

VOUT = 3.3VIQ = 100µA

VOUT50mV/DIV

IOUT1A/DIV

VIN = 12V 500µs/DIV 3434 G17

VOUT = 3.3VCOUT = 100µF

VOUT50mV/DIV

IOUT1A/DIV

VIN = 12V 500µs/DIV 3434 G18

VOUT = 3.3VCOUT = 100µFILOAD(DC) = 500mA

3.3V Dropout Operation

INPUT VOLTAGE (V)0

OUTP

UT V

OLTA

GE (V

)

4.0

3.5

3.0

2.5

2.0

1.5

1.0

0.5

04

3434 G24

1 2 3 53.50.5 1.5 2.5 4.5

VOUT = 3.3VBOOST DIODE = DIODES INC B1100

LOAD CURRENT0.25A

LOAD CURRENT2.5A

INPUT VOLTAGE (V)0

OUTP

UT V

OLTA

GE (V

)

4

5

6

3 5

3434 G25

3

2

1 2 4 6

1

0

VOUT = 5VBOOST DIODE = DIODES INC B1100

LOAD CURRENT0.25A

LOAD CURRENT2.5A

5V Dropout Operation

LT3434

73434fb

UUU

PI FU CTIO Sfrom the CT pin into the external capacitor. When the volt-age on the external capacitor reaches an internal clamp(VCT), the PG pin becomes a high impedance node. Theresultant PG delay time is given by t = CCT • VCT/ICT. If thevoltage on the PGFB pin drops below VPGFB, CCT will bedischarged rapidly to 0V and PG will be active low with a200µA sink capability. If the CT pin is clamped (Power Goodcondition) during normal operation and SHDN is taken low,the CT pin will be discharged and a delay period will occurwhen SHDN is returned high. See the Power Good sectionin Applications Information for details.

GND (Pins 8, 17): The GND pin connection acts as thereference for the regulated output, so load regulation willsuffer if the “ground” end of the load is not at the samevoltage as the GND pin of the IC. This condition will occurwhen load current or other currents flow through metalpaths between the GND pin and the load ground. Keep thepath between the GND pin and the load ground short anduse a ground plane when possible. The GND pin also actsas a heat sink and should be soldered (along with theexposed leadframe) to the copper ground plane to reducethermal resistance (see Applications Information).

CSS (Pin 9): A capacitor from the CSS pin to the regulatedoutput voltage determines the output voltage ramp rateduring start-up. When the current through the CSS capaci-tor exceeds the CSS threshold (ICSS), the voltage ramp ofthe output is limited. The CSS threshold is proportional tothe FB voltage (see Typical Performance Characteristics)and is defeated for FB voltage greater than 0.9V (typical).See Soft-Start section in Applications Information fordetails.

BIAS (Pin 10): The BIAS pin is used to improve efficiencywhen operating at higher input voltages and light loadcurrent. Connecting this pin to the regulated output volt-age forces most of the internal circuitry to draw itsoperating current from the output voltage rather than theinput supply. This architecture increases efficiency espe-cially when the input voltage is much higher than theoutput. Minimum output voltage setting for this mode ofoperation is 3V.

VC (Pin 11): The VC pin is the output of the error amplifierand the input of the peak switch current comparator. It isnormally used for frequency compensation, but can also

serve as a current clamp or control loop override. VC sitsat about 0.65V for light loads and 2.2V at maximum load.During the sleep portion of Burst Mode operation, the VCpin is held at a voltage slightly below the burst thresholdfor better transient response. Driving the VC pin to groundwill disable switching and place the IC into sleep mode.

FB (Pin 12): The feedback pin is used to determine theoutput voltage using an external voltage divider from theoutput that generates 1.25V at the FB pin . When the FB pindrops below 0.9V, switching frequency is reduced, theSYNC function is disabled and output ramp rate control isenabled via the CSS pin. See the Feedback section inApplications Information for details.

PGFB (PIN 13): The PGFB pin is the positive input to acomparator whose negative input is set at VPGFB. WhenPGFB is taken above VPGFB, current (ICSS) is sourced intothe CT pin starting the PG delay period. When the voltageon the PGFB pin drops below VPGFB, the CT pin is rapidlydischarged resetting the PG delay period. The PGFB volt-age is typically generated by a resistive divider from theregulated output or input supply. See Power Good sectionin Applications Information for details.

SYNC (Pin 14): The SYNC pin is used to synchronize theinternal oscillator to an external signal. It is directly logiccompatible and can be driven with any signal between30% and 70% duty cycle. The synchronizing range isequal to maximum initial operating frequency up to 700kHz.When the voltage on the FB pin is below 0.9V the SYNCfunction is disabled. See the Synchronizing section inApplications Information for details.

SHDN (Pin 15): The SHDN pin is used to turn off theregulator and to reduce input current to less than 1µA. TheSHDN pin requires a voltage above 1.3V with a typicalsource current of 5µA to take the IC out of the shutdownstate.

PG (Pin 16): The PG pin is functional only when the SHDNpin is above its threshold, and is active low when theinternal clamp on the CT pin is below its clamp level andhigh impedance when the clamp is active. The PG pin hasa typical sink capability of 200µA. See the Power Goodsection in Applications Information for details.

LT3434

83434fb

BLOCK DIAGRA

W

12FB

VC

Σ

15

INTERNAL REF

UNDERVOLTAGELOCKOUT

THERMALSHUTDOWN

SOFT-START

FOLDBACKDETECT

SLOPECOMP

ANTISLOPECOMP

1.2V CTCLAMP

2.4V

–

+

1.3V

1.25V

SHDN

9CSS

14SYNC

10BIAS

4VIN

SHDNCOMP

–

+

–

+

ERRORAMP

11

13PGFB

CT

1.12V –

+PG

COMP

7

BURST MODEDETECT

200kHzOSCILLATOR

SWITCHLATCH

CURRENTCOMP

DRIVERCIRCUITRY

RQ

SW

SW

S2

BOOST6

PG16

GND 17

PGND

3434 BD

8

VCCLAMP

3VIN

5

The LT3434 is a constant frequency, current mode buckconverter. This means that there is an internal clock and twofeedback loops that control the duty cycle of the powerswitch. In addition to the normal error amplifier, there is acurrent sense amplifier that monitors switch current on acycle-by-cycle basis. A switch cycle starts with an oscilla-tor pulse which sets the RS latch to turn the switch on. Whenswitch current reaches a level set by the current compara-tor the latch is reset and the switch turns off. Output volt-age control is obtained by using the output of the erroramplifier to set the switch current trip point. This techniquemeans that the error amplifier commands current to be

delivered to the output rather than voltage. A voltage fedsystem will have low phase shift up to the resonant fre-quency of the inductor and output capacitor, then an abrupt180° shift will occur. The current fed system will have 90°phase shift at a much lower frequency, but will not have theadditional 90° shift until well beyond the LC resonant fre-quency. This makes it much easier to frequency compen-sate the feedback loop and also gives much quicker tran-sient response.

Most of the circuitry of the LT3434 operates from aninternal 2.4V bias line. The bias regulator normally draws

Figure 1. LT3434 Block Diagram

LT3434

93434fb

BLOCK DIAGRA

W

power from the VIN pin, but if the BIAS pin is connected toan external voltage higher than 3V bias power will bedrawn from the external source (typically the regulatedoutput voltage). This improves efficiency.

High switch efficiency is attained by using the BOOST pinto provide a voltage to the switch driver which is higherthan the input voltage, allowing switch to be saturated.This boosted voltage is generated with an external capaci-tor and diode.

To further optimize efficiency, the LT3434 automaticallyswitches to Burst Mode operation in light load situations.In Burst Mode operation, all circuitry associated withcontrolling the output switch is shut down reducing theinput supply current to 45µA.

The LT3434 contains a power good flag with a program-mable threshold and delay time. A logic-level low on theSHDN pin disables the IC and reduces input suppy currentto less than 1µA.

APPLICATIO S I FOR ATIO

WU UU

FEEDBACK PIN FUNCTIONS

The feedback (FB) pin on the LT3434 is used to set outputvoltage and provide several overload protection features.The first part of this section deals with selecting resistorsto set output voltage and the remaining part talks aboutfrequency foldback and soft-start features. Please readboth parts before committing to a final design.

Referring to Figure 2, the output voltage is determined bya voltage divider from VOUT to ground which generates1.25V at the FB pin. Since the output divider is a load on theoutput care must be taken when choosing the resistordivider values. For light load applications the resistorvalues should be as large as possible to achieve peakefficiency in Burst Mode operation. Extremely large valuesfor resistor R1 will cause an output voltage error due to the50nA FB pin input current. The suggested value for theoutput divider resistor (see Figure 2) from FB to ground(R2) is 100k or less. A formula for R1 is shown below. Atable of standard 1% values is shown in Table 1 forcommon output voltages.

R RV

R nAOUT1 2

1 251 25 2 50

=+

•– .

. •

More Than Just Voltage Feedback

The FB pin is used for more than just output voltagesensing. It also reduces switching frequency and con-trols the soft-start voltage ramp rate when output voltageis below the regulated level (see the Frequency Foldback

Table 1

OUTPUT R1 OUTPUTVOLTAGE R2 NEAREST (1%) ERROR

(V) (kΩ, 1%) (kΩ) (%)

2.5 100 100 0

3 100 140 0

3.3 100 165 0.38

5 100 300 0

6 100 383 0.63

8 100 536 –0.63

10 100 698 –0.25

12 100 866 0.63

SOFT-START

FOLDBACKDETECT

200kHzOSCILLATOR

–

+

ERRORAMP

1.25V

VC11

FB12

CSS

VOUT

9

SWLT3434

C1

R1

R2

3434 F02

2

Figure 2. Feedback Network

LT3434

103434fb

APPLICATIO S I FOR ATIO

WU UU

and Soft-Start Current graphs in Typical PerformanceCharacteristics).

Frequency foldback is done to control power dissipation inboth the IC and in the external diode and inductor duringshort-circuit conditions. A shorted output requires theswitching regulator to operate at very low duty cycles. Asa result the average current through the diode and induc-tor is equal to the short-circuit current limit of the switch(typically 4.7A for the LT3434). Minimum switch on timelimitations would prevent the switcher from attaining asufficiently low duty cycle if switching frequency weremaintained at 200kHz, so frequency is reduced by about4:1 when the FB pin voltage drops below 0.4V (seeFrequency Foldback graph). In addition, if the current inthe switch exceeds 1.5 times the current limitations speci-fied by the VC pin, due to minimum switch on time, theLT3434 will skip the next switch cycle. As the feedbackvoltage rises, the switching frequency increases to 200kHzwith 0.95V on the FB pin. During frequency foldback,external syncronization is disabled to prevent interferencewith foldback operation. Frequency foldback does notaffect operation during normal load conditions.

In addition to lowering switching frequency the soft-startramp rate is also affected by the feedback voltage. Largecapacitive loads or high input voltages can cause a highinput current surge during start-up. The soft-start func-tion reduces input current surge by regulating switchcurrent via the VC pin to maintain a constant voltage ramprate (dV/dt) at the output. A capacitor (C1 in Figure 2) fromthe CSS pin to the output determines the maximum outputdV/dt. When the feedback voltage is below 0.4V, the VC pinwill rise, resulting in an increase in switch current andoutput voltage. If the dV/dt of the output causes the currentthrough the CSS capacitor to exceed ICSS the VC voltage isreduced resulting in a constant dV/dt at the output. As thefeedback voltage increases ICSS increases, resulting in anincreased dV/dt until the soft-start function is defeatedwith 0.9V present at the FB pin. The soft-start functiondoes not affect operation during normal load conditions.However, if a momentary short (brown out condition) ispresent at the output which causes the FB voltage to dropbelow 0.9V, the soft-start circuitry will become active.

INPUT CAPACITOR

Step-down regulators draw current from the input supplyin pulses. The rise and fall times of these pulses are veryfast. The input capacitor is required to reduce the voltageripple this causes at the input of LT3434 and force theswitching current into a tight local loop, thereby minimiz-ing EMI. The RMS ripple current can be calculated from:

IIV

V V VRIPPLE RMSOUT

INOUT IN OUT( ) –= ( )

Ceramic capacitors are ideal for input bypassing. At 200kHzswitching frequency input capacitor values in the range of4.7µF to 20µF are suitable for most applications. If opera-tion is required close to the minimum input required by theLT3434 a larger value may be required. This is to preventexcessive ripple causing dips below the minimum operat-ing voltage resulting in erratic operation.

Input voltage transients caused by input voltage steps orby hot plugging the LT3434 to a pre-powered source suchas a wall adapter can exceed maximum VIN ratings. Thesudden application of input voltage will cause a largesurge of current in the input leads that will store energy inthe parasitic inductance of the leads. This energy willcause the input voltage to swing above the DC level of inputpower source and it may exceed the maximum voltagerating of the input capacitor and LT3434. All input voltagetransient sequences should be observed at the VIN pin ofthe LT3434 to ensure that absolute maximum voltageratings are not violated.

The easiest way to suppress input voltage transients is toadd a small aluminum electrolytic capacitor in parallel withthe low ESR input capacitor. The selected capacitor needsto have the right amount of ESR to critically damp theresonant circuit formed by the input lead inductance andthe input capacitor. The typical values of ESR will fall in therange of 0.5Ω to 2Ω and capacitance will fall in the rangeof 5µF to 50µF.

If tantalum capacitors are used, values in the 22µF to470µF range are generally needed to minimize ESR andmeet ripple current and surge ratings. Care should be

LT3434

113434fb

APPLICATIO S I FOR ATIO

WU UU

Unlike the input capacitor RMS, ripple current in theoutput capacitor is normally low enough that ripple cur-rent rating is not an issue. The current waveform istriangular with a typical value of 200mARMS. The formulato calculate this is:

Output capacitor ripple current (RMS)

IV V V

L f VRIPPLE RMSOUT IN OUT

IN( )

. –= ( )( )

( )( )( ) =0 29

12IP-P

CERAMIC CAPACITORS

Higher value, lower cost ceramic capacitors are nowbecoming available. They are generally chosen for theirgood high frequency operation, small size and very lowESR (effective series resistance). Low ESR reduces outputripple voltage but also removes a useful zero in the loopfrequency response, common to tantalum capacitors. Tocompensate for this a resistor RC can be placed in serieswith the VC compensation capacitor CC (Figure 10). Caremust be taken however since this resistor sets the highfrequency gain of the error amplifier including the gain atthe switching frequency. If the gain of the error amplifieris high enough at the switching frequency output ripplevoltage (although smaller for a ceramic output capacitor)may still affect the proper operation of the regulator. Afilter capacitor CF in parallel with the RC/CC network, alongwith a small feedforward capacitor CFB, is suggested tocontrol possible ripple at the VC pin. The LT3434 can bestabilized using a 100µF ceramic output capacitor and VCcomponent values of CC = 4700pF, RC = 10k, CF = 470pFand CFB = 27pF.

OUTPUT RIPPLE VOLTAGE

Figure 3 shows a typical output ripple voltage waveformfor the LT3434. Ripple voltage is determined by theimpedance of the output capacitor and ripple currentthrough the inductor. Peak-to-peak ripple current throughthe inductor into the output capacitor is:

IV V V

V L fOUT IN OUT

INP-P = ( )

( )( )( )–

taken to ensure the ripple and surge ratings are notexceeded. The AVX TPS and Kemet T495 series are surgerated AVX recommends derating capacitor operating volt-age by 2:1 for high surge applications.

OUTPUT CAPACITOR

The output capacitor is normally chosen by its effectiveseries resistance (ESR) because this is what determinesoutput ripple voltage. To get low ESR takes volume, sophysically smaller capacitors have higher ESR. The ESRrange for typical LT3434 applications is 0.05Ω to 0.2Ω. Atypical output capacitor is an AVX type TPS, 100µF at 10V,with a guaranteed ESR less than 0.1Ω. This is a “D” sizesurface mount solid tantalum capacitor. TPS capacitorsare specially constructed and tested for low ESR, so theygive the lowest ESR for a given volume. The value inmicrofarads is not particularly critical and values from22µF to greater than 500µF work well, but you cannotcheat Mother Nature on ESR. If you find a tiny 22µF solidtantalum capacitor, it will have high ESR and output ripplevoltage could be unacceptable. Table 2 shows sometypical solid tantalum surface mount capacitors.Table 2. Surface Mount Solid Tantalum Capacitor ESRand Ripple CurrentE CASE SIZE ESR MAX (Ω) RIPPLE CURRENT (A)

AVX TPS 0.1 to 0.3 0.7 to 1.1

D CASE SIZE

AVX TPS 0.1 to 0.3 0.7 to 1.1

C CASE SIZE

AVX TPS 0.2 0.5

Many engineers have heard that solid tantalum capacitorsare prone to failure if they undergo high surge currents.This is historically true and type TPS capacitors arespecially tested for surge capability but surge ruggednessis not a critical issue with the output capacitor. Solidtantalum capacitors fail during very high turn-on surgeswhich do not occur at the output of regulators. Highdischarge surges, such as when the regulator output isdead shorted, do not harm the capacitors.

LT3434

123434fb

APPLICATIO S I FOR ATIO

WU UU

For high frequency switchers the ripple current slew rateis also relevant and can be calculated from:

didt

VLIN=

Peak-to-peak output ripple voltage is the sum of a triwavecreated by peak-to-peak ripple current times ESR and asquare wave created by parasitic inductance (ESL) andripple current slew rate. Capacitive reactance is assumedto be small compared to ESR or ESL.

V I ESR ESLdidtRIPPLE = ( )( ) + ( )P-P

Example: with VIN = 12V, VOUT = 3.3V, L = 33µH, ESR =0.08Ω, ESL = 10nH:

IP-P = ( )( )( ) −( )( ) =

= =

3 3 12 3 312 33 6 200 3

0 362

123 3 5

3 63 5

. – ..

. –.

e eA

didt e

e

VRIPPLE = (0.362A)(0.08) + (10e – 9)(363e3)

= 0.0289 + 0.003 = 32mVP-P

MAXIMUM OUTPUT LOAD CURRENT

Maximum load current for a buck converter is limited bythe maximum switch current rating (IPK). The minimumpeak current rating for the LT3434 is 3A. Unlike most

current mode converters, the LT3434 maximum switchcurrent limit does not fall off at high duty cycles. Mostcurrent mode converters suffer a drop off of peak switchcurrent for duty cycles above 50%. This is due to theeffects of slope compensation required to preventsubharmonic oscillations in current mode converters.(For detailed analysis, see Application Note 19.)

The LT3434 is able to maintain peak switch current limitover the full duty cycle range by using patented circuitry tocancel the effects of slope compensation on peak switchcurrent without affecting the frequency compensation itprovides.

Maximum load current would be equal to maximumswitch current for an infinitely large inductor, but withfinite inductor size, maximum load current is reduced byone-half peak-to-peak inductor current. The followingformula assumes continuous mode operation, implyingthat the term on the right (IP-P/2) is less than IOUT.

I IV V V

L f VI

IOUT MAX PK

OUT IN OUT

INPK

P( ) –

––= ( )( )

( )( )( ) =2

-P2

Discontinuous operation occurs when:

IV V V

L f VOUT DISOUT IN OUT

IN( )

–( )( )( )

≤ ( )2

For VOUT = 5V, VIN = 8V and L = 20µH:

Ie e

A

OUT MAX( ) ––

–

– . .

= ( )( )( )( )( )

= =

35 8 5

2 20 6 200 3 8

3 0 24 2 76

Note that there is less load current available at the higherinput voltage because inductor ripple current increases. AtVIN = 15V, duty cycle is 33% and for the same set ofconditions:

Ie e

A

OUT MAX( ) ––

–

– . .

= ( )( )( )( )( )

= =

35 15 5

2 20 6 200 3 15

3 0 42 2 58

Figure 3. LT3434 Ripple Voltage Waveform

VOUT10mV/DIV

100µF75mΩ TANTALUM

VOUT10mV/DIV

100µF CERAMIC

ISW10V/DIV

ILOAD = 2A 1µs/DIV 3434 F03

LT3434

133434fb

APPLICATIO S I FOR ATIO

WU UU

To calculate actual peak switch current in continuousmode with a given set of conditions, use:

I IV V V

L f VSW PK OUT

OUT IN OUT

IN( )

–= +

( )( )( )( )2

If a small inductor is chosen which results in discontinousmode operation over the entire load range, the maximumload current is equal to:

II f L VV V VOUT MAXPK IN

OUT IN OUT( ) –

= ( )( )( )( )( )

222

CHOOSING THE INDUCTOR

For most applications the output inductor will fall in therange of 15µH to 100µH. Lower values are chosen toreduce physical size of the inductor. Higher values allowmore output current because they reduce peak currentseen by the LT3434 switch, which has a minimum 3A limit.Higher values also reduce output ripple voltage and reducecore loss.

When choosing an inductor you might have to considermaximum load current, core and copper losses, allow-able component height, output voltage ripple, EMI, faultcurrent in the inductor, saturation and of course cost.The following procedure is suggested as a way of han-dling these somewhat complicated and conflictingrequirements.

1. Choose a value in microhenries such that the maximumload current plus half of the inductor ripple current isless than the minimum peak switch current (IPK).Choosing a small inductor with lighter loads may resultin discontinuous mode of operation, but the LT3434 isdesigned to work well in either mode.

Assume that the average inductor current is equal toload current and decide whether or not the inductor

must withstand continuous fault conditions. If maxi-mum load current is 1A, for instance, a 1A inductor maynot survive a continuous 4A overload condition.

For applications with a duty cycle above 50%, theinductor value should be chosen to obtain an inductorripple current of less than 40% of the peak switchcurrent.

2. Calculate peak inductor current at full load current toensure that the inductor will not saturate. Peak currentcan be significantly higher than output current, especiallywith smaller inductors and lighter loads, so don’t omitthis step. Powdered iron cores are forgiving because theysaturate softly, whereas ferrite cores saturate abruptly.Other core materials fall somewhere in between. Thefollowing formula assumes continuous mode of opera-tion, but it errs only slightly on the high side for discon-tinuous mode, so it can be used for all conditions.

Table 3. Inductor Selection CriteriaVENDOR/ VALUE IDC DCR HEIGHTPART NO. (µH) (Amps) (Ohms) (mm)

Sumida

CDRH104R-150 15 3.6 0.050 4

CDRH104R-220 22 2.9 0.073 4

CDRH104R-330 33 2.3 0.093 4

CDRH124-220 22 2.9 0.066 4.5

CDRH124-330 33 2.7 0.097 4.5

CDRH127-330 33 3.0 0.065 8

CDRH127-470 47 2.5 0.100 8

CEI122-220 22 2.3 0.085 3

Coiltronics

UP3B-330 33 3 0.069 6.8

UP3B-470 47 2.4 0.108 6.8

UP4B-680 68 4.3 0.120 7.9

Coilcraft

DO3316P-153 15 3 0.046 5.2

DO5022p-683 68 3.5 0.130 7.1

LT3434

143434fb

APPLICATIO S I FOR ATIO

WU UU

I IV V V

f L VPEAK OUTOUT IN OUT

IN= + ( )

( )( )( )–

2

VIN = maximum input voltage

f = switching frequency, 200kHz

3. Decide if the design can tolerate an “open” core geom-etry like a rod or barrel, which have high magnetic fieldradiation, or whether it needs a closed core like a toroidto prevent EMI problems. This is a tough decisionbecause the rods or barrels are temptingly cheap andsmall and there are no helpful guidelines to calculatewhen the magnetic field radiation will be a problem.

4. After making an initial choice, consider the secondarythings like output voltage ripple, second sourcing, etc.Use the experts in the Linear Technology’s applicationsdepartment if you feel uncertain about the final choice.They have experience with a wide range of inductortypes and can tell you about the latest developments inlow profile, surface mounting, etc.

Short-Circuit Considerations

The LT3434 is a current mode controller. It uses the VCnode voltage as an input to a current comparator whichturns off the output switch on a cycle-by-cycle basis asthis peak current is reached. The internal clamp on the VCnode, nominally 2.2V, then acts as an output switch peakcurrent limit. This action becomes the switch current limitspecification. The maximum available output power isthen determined by the switch current limit.

A potential controllability problem could occur undershort-circuit conditions. If the power supply output isshort circuited, the feedback amplifier responds to the lowoutput voltage by raising the control voltage, VC, to itspeak current limit value. Ideally, the output switch wouldbe turned on, and then turned off as its current exceededthe value indicated by VC. However, there is finite responsetime involved in both the current comparator and turn-offof the output switch. These result in a typical minimum ontime of 250ns. When combined with the large ratio of VINto (VF + I • R), the diode forward voltage plus inductor I • Rvoltage drop, the potential exists for a loss of control.

Expressed mathematically the requirement to maintaincontrol is:

f tV I R

VONF

IN•

•≤ +

where:

f = switching frequencytON = switch on timeVF = diode forward voltageVIN = Input voltageI • R = inductor I • R voltage drop

If this condition is not observed, the current will not belimited at IPK but will cycle-by-cycle ratchet up to somehigher value. Using the nominal LT3434 clock frequencyof 200kHz, a VIN of 40V and a (VF + I • R) of say 0.7V, themaximum tON to maintain control would be approximately90ns, an unacceptably short time.

The solution to this dilemma is to slow down the oscillatorto allow the current in the inductor to drop to a sufficientlylow value such that the current doesn’t continue to ratchethigher. When the FB pin voltage is abnormally low therebyindicating some sort of short-circuit condition, the oscil-lator frequency will be reduced. Oscillator frequency isreduced by a factor of 4 when the FB pin voltage is below0.4V and increases linearly to its typical value of 200kHz ata FB voltage of 0.95V (see Typical Performance Character-istics). In addition, if the current in the switch exceeds 1.5• IPK current demanded by the VC pin, the LT3434 will skipthe next on cycle effectively reducing the oscillator fre-quency by a factor of 2. These oscillator frequency reduc-tions during short-circuit conditions allow the LT3434 tomaintain current control.

SOFT-START

For applications where [VIN/(VOUT + VF)] ratios > 10 orlarge input surge currents can’t be tolerated, the LT3434soft-start feature should be used to control the outputcapacitor charge rate during start-up, or during recoveryfrom an output short circuit thereby adding additionalcontrol over peak inductor current. The soft-start function

LT3434

153434fb

CCSS = 1000pF

CCSS = 0.01µF

CCSS = 0.1µF

APPLICATIO S I FOR ATIO

WU UU

limits the switch current via the VC pin to maintain aconstant voltage ramp rate (dV/dt) at the output capacitor.A capacitor (C1 in Figure 2) from the CSS pin to theregulated output voltage determines the output voltageramp rate. When the current through the CSS capacitorexceeds the CSS threshold (ICSS), the voltage ramp of theoutput capacitor is limited by reducing the VC pin voltage.The CSS threshold is proportional to the FB voltage (seeTypical Performance Characteristics) and is defeated forFB voltages greater than 0.9V (typical). The output dV/dtcan be approximated by:

dVdt

ICCSS

SS=

but actual values will vary due to start-up load conditions,compensation values and output capacitor selection.

average input current is greatly reduced resulting in higherefficiency.

The minimum average input current depends on the VIN toVOUT ratio, VC frequency compensation, feedback dividernetwork and Schottky diode leakage. It can be approxi-mated by the following equation:

I I IVV

I I IIN AVG VINS SHDN

OUT

IN

BIASS FB S( ) ≅ + + ⎛

⎝⎜⎞⎠⎟

+ +( )( )η

where

IVINS = input pin current in sleep modeVOUT = output voltageVIN = input voltageIBIASS = BIAS pin current in sleep modeIFB = feedback network currentIS = catch diode reverse leakage at VOUT

η = low current efficiency (non Burst Mode operation)

Example: For VOUT = 3.3V, VIN = 12V

I A AA A A

A A A A

IN AVG( ). . .

.= µ + µ + ⎛

⎝⎜⎞⎠⎟

µ + µ + µ( )( )

= µ + µ + µ = µ

45 53 312

125 12 5 0 50 85

45 5 44 99

Burst Mode OPERATION

To enhance efficiency at light loads, the LT3434 automati-cally switches to Burst Mode operation which keeps theoutput capacitor charged to the proper voltage whileminimizing the input quiescent current. During BurstMode operation, the LT3434 delivers short bursts ofcurrent to the output capacitor followed by sleep periodswhere the output power is delivered to the load by theoutput capacitor. In addition, VIN and BIAS quiescentcurrents are reduced to typically 45µA and 110µA respec-tively during the sleep time. As the load current increasestowards a no load condition, the percentage of time thatthe LT3434 operates in sleep mode increases and the

Figure 5. IQ vs VIN

INPUT VOLTAGE (V)0

0

SUPP

LY C

URRE

NT (µ

A)

50

100

10 20 30 40

3434 F05

50

150

25

75

125

60

VOUT = 3.3V

During the sleep portion of the Burst Mode cycle, the VCpin voltage is held just below the level needed for normaloperation to improve transient response. See the TypicalPerformance Characteristics section for burst and tran-sient response waveforms.

Figure 4. VOUT dV/dt

VOUT0.5V/DIV

VIN = 12V 1ms/DIV 3434 F04

VOUT = 3.3VILOAD = 500mA

LT3434

163434fb

Table 4. Catch Diode Selection CriteriaIQ at 125°C EFFICIENCY

LEAKAGE VIN =12V VIN =12VVOUT = 3.3V VF AT 1A VOUT = 3.3 VOUT = 3.3V

DIODE 25°C 125°C 25°C 125°C IL = 0A IL = 1A

IR 10BQ100 0.0µA 59µA 0.72V 0.58V 125µA 78.2%

Diodes Inc. 0.1µA 242µA 0.48V 0.41V 215µA 82%B260SMA

Diodes Inc. 0.2µA 440µA 0.45V 0.36V 270µA 82.8%B360SMB

IR 1µA 1.81mA 0.42V 0.34V 821µA 82.7%MBRS360TR

IR 30BQ100 1.7µA 2.64mA 0.40V 0.32V 1088µA 80.3%

APPLICATIO S I FOR ATIO

WU UU

If a no load condition can be anticipated, the supply currentcan be further reduced by cycling the SHDN pin at a ratehigher than the natural no load burst frequency. Figure 6shows Burst Mode operation with the SHDN pin. VOUTburst ripple is maintained while the average supply currentdrops to 15µA. The PG pin will be active low during the“on” portion of the SHDN waveform due to the CT capaci-tor discharge when SHDN is taken low. See the PowerGood section for further information.

lack of a significant reverse recovery time. Schottky diodesare generally available with reverse voltage ratings of 60Vand even 100V and are price competitive with other types.

The effect of reverse leakage and forward drop on effi-ciency for various Schottky diodes is shown in Table 4. Ascan be seen these are conflicting parameters and the usermust weigh the importance of each specification in choos-ing the best diode for the application.

The use of so-called “ultrafast” recovery diodes is gener-ally not recommended. When operating in continuousmode, the reverse recovery time exhibited by “ultrafast”diodes will result in a slingshot type effect. The powerinternal switch will ramp up VIN current into the diode in anattempt to get it to recover. Then, when the diode hasfinally turned off, some tens of nanoseconds later, the VSWnode voltage ramps up at an extremely high dV/dt, per-haps 5V to even 10V/ns! With real world lead inductancesthe VSW node can easily overshoot the VIN rail. This canresult in poor RFI behavior and, if the overshoot is severeenough, damage the IC itself.

BOOST PIN

For most applications the boost components are a 0.68µFcapacitor and a MMSD914 diode. The anode is typicallyconnected to the regulated output voltage to generate avoltage approximately VOUT above VIN to drive the outputstage (Figure 7a). However, the output stage dischargesthe boost capacitor during the on time of the switch. Theoutput driver requires at least 2.5V of headroom through-out this period to keep the switch fully saturated. If the

Figure 6. Burst Mode with Shutdown Pin

VOUT50mV/DIV

VSHDN2V/DIV

ISW500mA/DIV

VIN = 12V TIME (50ms/DIV) 3434 G16

VOUT = 3.3VIQ = 15µA

CATCH DIODE

The catch diode carries load current during the SW offtime. The average diode current is therefore dependent onthe switch duty cycle. At high input to output voltage ratiosthe diode conducts most of the time. As the ratio ap-proaches unity the diode conducts only a small fraction ofthe time. The most stressful condition for the diode iswhen the output is short circuited. Under this condition thediode must safely handle IPEAK at maximum duty cycle.

To maximize high and low load current efficiency a fastswitching diode with low forward drop and low reverseleakage should be used. Low reverse leakage is critical tomaximize low current efficiency since its value over tem-perature can potentially exceed the magnitude of theLT3434 supply current. Low forward drop is critical forhigh current efficiency since the loss is proportional toforward drop.

These requirements result in the use of a Schottky typediode. DC switching losses are minimized due to its lowforward voltage drop and AC behavior is benign due to its

LT3434

173434fb

APPLICATIO S I FOR ATIO

WU UU

output voltage is less than 3.3V it is recommended that analternate boost supply is used. The boost diode can beconnected to the input (Figure 7b) but care must be takento prevent the boost voltage (VBOOST = VIN • 2) fromexceeding the BOOST pin absolute maximum rating. Theadditional voltage across the switch driver also increasespower loss and reduces efficiency. If available, an inde-pendent supply can be used to generate the requiredBOOST voltage (Figure 7c). Tying BOOST to VIN or anindependent supply may reduce efficiency but it will re-duce the minimum VIN required to start-up with lightloads. If the generated BOOST voltage dissipates toomuch power at maximum load, the BOOST voltage theLT3434 sees can be reduced by placing a Zener diode inseries with the BOOST diode (Figure 7a option).

A 0.68µF boost capacitor is recommended for most appli-cations. Almost any type of film or ceramic capacitor issuitable but the ESR should be <1Ω to ensure it can be fullyrecharged during the off time of the switch. The capacitorvalue is derived from worst-case conditions of 4700ns ontime, 65mA boost current and 0.7V discharge ripple. Theboost capacitor value could be reduced under less de-manding conditions but this will not improve circuit opera-tion or efficiency. Under low input voltage and low loadconditions a higher value capacitor will reduce dischargeripple and improve start-up operation.

SHUTDOWN FUNCTION AND UNDERVOLTAGELOCKOUT

The SHDN pin on the LT3434 controls the operation of theIC. When the voltage on the SHDN pin is below the 1.2Vshutdown threshold the LT3434 is placed in a “zero”supply current state. Driving the SHDN pin above theshutdown threshold enables normal operation. The SHDNpin has an internal sink current of 3µA.

In addition to the shutdown feature, the LT3434 has anundervoltage lockout function. When the input voltage isbelow 2.4V, switching will be disabled. The undervoltagelockout threshold doesn’t have any hysteresis and ismainly used to insure that all internal voltages are at thecorrect level before switching is enabled. If an undervolt-age lockout function with hysteresis is needed to limitinput current at low VIN to VOUT ratios refer to Figure 8 andthe following:

V RV

RV

RI V

VV R

R

UVLOSHDN SHDN

SHDN SHDN

HYSTOUT

= + +⎛⎝⎜

⎞⎠⎟

+

= ( )

13 2

13

R1 should be chosen to minimize quiescent current duringnormal operation by the following equation:

RV VIIN

SHDN MAX1

21 5

= ( )( )–

. ( )

BOOST

LT3434

VBOOST – VSW = VOUTVBOOST(MAX) = VIN + VOUT

VIN VOUT

OPTIONAL

(7a)

VIN

SWGND

BOOST

LT3434

VBOOST – VSW = VDCVBOOST(MAX) = VDC + VIN

VIN VDC

DSS

3434 F07

VOUT

(7c)

VIN

SWGND

BOOST

LT3434

VBOOST – VSW = VINVBOOST(MAX) = 2VIN

VIN

VOUT

(7b)

VIN

SWGND

Figure 7. BOOST Pin Configurations

LT3434

183434fb

APPLICATIO S I FOR ATIO

WU UU

Example:

RA

M

RM

M

AM

k

112 2

1 5 51 3

35 1 3

16 5

1 1 36 49

408

=µ( ) = Ω

=Ω( ) = Ω Ω

Ωµ

Ω=

–.

.

..

– – ..

(Nearest 1% 6.49M )

R2 =1.3

7 – 1.31.3M

(Nearest 1% 412k)

See the Typical Performance Characteristics section forgraphs of SHDN and VIN currents verses input voltage.

SYNCHRONIZING

Oscillator synchronization to an external input is achievedby connecting a TTL logic-compatible square wave with aduty cycle between 30% and 70% to the LT3434 SYNCpin. The synchronizing range is equal to initial operatingfrequency up to 700kHz. This means that minimumpractical sync frequency is equal to the worst-case highself-oscillating frequency (230kHz), not the typical oper-ating frequency of 200kHz. Caution should be used whensynchronizing above 230kHz because at higher syncfrequencies the amplitude of the internal slope compen-sation used to prevent subharmonic switching is re-duced. This type of subharmonic switching only occurs atinput voltages less than twice output voltage. Higherinductor values will tend to eliminate this problem. See

Figure 8. Undervoltage Lockout

ENABLE

1.3V

3434 F08

3µA

SHDN

R2

2.4V

–

+SHDNCOMP

–

+VIN

COMP

15

VIN

VOUT

LT3434

4

R1R3

Frequency Compensation section for a discussion of anentirely different cause of subharmonic switching beforeassuming that the cause is insufficient slope compensa-tion. Application Note 19 has more details on the theoryof slope compensation.

If the FB pin voltage is below 0.9V (power-up or outputshort-circuit conditions) the sync function is disabled.This allows the frequency foldback to operate to avoid andhazardous conditions for the SW pin.

If the synchronization signal is present during Burst Modeoperation, synchronization will occur during the burstportion of the output waveform. Synchronizing the LT3434during Burst Mode operation may alter the natural burstfrequency which can lead to jitter and increased ripple inthe burst waveform.

If no synchronization is required this pin should be con-nected to ground.

POWER GOOD

The LT3434 contains a power good block which consistsof a comparator, delay timer and active low flag that allowsthe user to generate a delayed signal after the power goodthreshold is exceeded.

Referring to Figure 2, the PGFB pin is the positive input toa comparator whose negative input is set at VPGFB. WhenPGFB is taken above VPGFB, current (ICSS) is sourced intothe CT pin starting the delay period. When the voltage onthe PGFB pin drops below VPGFB the CT pin is rapidlydischarged resetting the delay period. The PGFB voltage istypically generated by a resistive divider from the regu-lated output or input supply.

The capacitor on the CT pin determines the amount ofdelay time between the PGFB pin exceeding its threshold(VPGFB) and the PG pin set to a high impedance state.When the PGFB pin rises above VPGFB current is sourced(ICT) from the CT pin into the external capacitor. When thevoltage on the external capacitor reaches an internal clamp(VCT), the PG pin becomes a high impedance node. Theresultant PG delay time is given by t = CCT • (VCT)/(ICT). Ifthe voltage on the PGFB pin drops below its VPGFB, CCT willbe discharged rapidly and PG will be active low with a200µA sink capability. If the SHDN pin is taken below its

LT3434

193434fb

APPLICATIO S I FOR ATIO

WU UU

Figure 9. Power Good

VOUT500mV/DIV

PG100k TO VIN

VCT500mV/DIV

VSHDN2V/DIV

TIME (10ms/DIV) 3434 F09

VIN

PG

PGFB

LT3434

PG at 80% VOUT with 100ms Delay

0.27µF

COUT

COUT

200k

VOUT = 3.3V

153k

12k

100kFB

CT

VIN

PG

PGFB

LT3434

VOUT Disconnect at 80% VOUT with 100ms Delay

0.27µF

200k

VOUT = 3.3V153k

12k

100kFB

CT

VIN

PG

PGFBLT3434

PG at VIN > 4V with 100ms Delay

0.27µF

VOUT = 3.3V

200k

511k

200k

100k

165k

FB

CT

VIN

PG

PGFB

LT3434

VOUT Disconnect 3.3V Logic Signal with 100µs Delay

270pF

200k

VOUT = 12V

3434 F10

866k

100kFB

CT

COUT COUT

Figure 10. Power Good Circuits

threshold during normal operation, the CT pin will bedischarged and PG inactive, resulting in a non Power Goodcycle when SHDN is taken above its threshold. Figure 9shows the power good operation with PGFB connected toFB and the capacitance on CT = 0.1µF. The PGFB pin hasa limited amount of driver capability and is susceptible to

noise during start-up and Burst Mode operation. If erraticoperation occurs during these conditions a small filtercapacitor from the PGFB pin to ground will ensure properoperation. Figure 10 shows several different configura-tions for the LT3434 Power Good circuitry.

LAYOUT CONSIDERATIONS

As with all high frequency switchers, when consideringlayout, care must be taken in order to achieve optimalelectrical, thermal and noise performance. For maximumefficiency switch rise and fall times are typically in thenanosecond range. To prevent noise both radiated andconducted the high speed switching current path, shownin Figure 11, must be kept as short as possible. This isimplemented in the suggested layout of Figure 12. Short-ening this path will also reduce the parasitic trace induc-tance of approximately 25nH/inch. At switch off, thisparasitic inductance produces a flyback spike across the

LT3434

203434fb

APPLICATIO S I FOR ATIO

WU UU

LT3434 switch. When operating at higher currents andinput voltages, with poor layout, this spike can generatevoltages across the LT3434 that may exceed its absolutemaximum rating. A ground plane should always be usedunder the switcher circuitry to prevent interplane couplingand overall noise.

The VC and FB components should be kept as far away aspossible from the switch and boost nodes. The LT3434pinout has been designed to aid in this. The ground forthese components should be separated from the switchcurrent path. Failure to do so will result in poor stability orsubharmonic like oscillation.

Board layout also has a significant effect on thermalresistance. Pin 8 and the exposed die pad, Pin 17, are acontinuous copper plate that runs under the LT3434 die.This is the best thermal path for heat out of the package.Reducing the thermal resistance from Pin 8 and exposedpad onto the board will reduce die temperature and in-crease the power capability of the LT3434. This is achievedby providing as much copper area as possible around theexposed pad. Adding multiple solder filled feedthroughsunder and around this pad to an internal ground plane willalso help. Similar treatment to the catch diode and coilterminations will reduce any additional heating effects.

THERMAL CALCULATIONS

Power dissipation in the LT3434 chip comes from foursources: switch DC loss, switch AC loss, boost circuitcurrent, and input quiescent current. The following formu-las show how to calculate each of these losses. Theseformulas assume continuous mode operation, so theyshould not be used for calculating efficiency at light loadcurrents.

Switch loss:

PR I V

Vt I V fSW

SW OUT OUT

INEFF OUT IN= ( ) ( ) + ( )( )( )( )

2

1 2/

Boost current loss:

PV I

VBOOSTOUT OUT

IN=

( ) ( )2 40/

Quiescent current loss:

PQ = VIN (0.0026) + VOUT (0.001)

RSW = switch resistance (≈0.15 when hot )tEFF = effective switch current/voltage overlap time(tr + tf + tIR + tIF)tr = (VIN/1.2)nstf = (VIN/1.7)nstIR = tIF = (IOUT/0.2)nsf = switch frequency

Figure 12. Suggested Layout

Figure 11. High Speed Switching Path

NC

R2

C2

C5

R1

R3

C4

SW

VIN

VIN

SW

BOOST

CT

GND

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

PGOOD

SHDN

SYNC

PGFB

FB

VC

BIAS

CSS

3434 F12

C3

GND

GND

D1

L1VOUT

C1

C2 D2

MINIMIZED1-C3LOOP

VIN

KELVIN SENSEFEEDBACKTRACE AND

KEEP SEPARATEFROM BIAS TRACE

CONNECT PIN 8 GND TO THEPIN 17 EXPOSED PAD GND

PLACE VIA's UNDER EXPOSEDPAD TO A BOTTOM PLANE TO

ENHANCE THERMALCONDUCTIVITY

LT3434

C2 C1

3434 F11

D1

L1VIN

LT3434VOUT

VIN

SW4 2

HIGHFREQUENCY

CIRCULATIONPATH

+LOAD

LT3434

213434fb

APPLICATIO S I FOR ATIO

WU UU

Example: with VIN = 40V, VOUT = 5V and IOUT = 2A:

P e eSW =( )( ) ( )

+ ( )( )( )( )0 15 2 540

77 9 1 2 2 40 2002.

– / 33

0 08 0 62 0 7

5 2 4040

0 032

( )

+ =

=( ) ( )

=

. . .

/.P

P

BOOST

Q == ( ) + ( ) =40 0 0026 5 0 001 0 109. . .

Total power dissipation is:

PTOT = 0.7 + 0.03 + 0.109 = 0.84

Thermal resistance for the LT3434 package is influencedby the presence of internal or backside planes. With a fullplane under the FE16 package, thermal resistance will beabout 45°C/W. No plane will increase resistance to about150°C/W. To calculate die temperature, use the properthermal resistance number for the desired package andadd in worst-case ambient temperature:

TJ = TA + QJA (PTOT)

With the FE16 package (QJA = 45°C/W) at an ambienttemperature of 70°C:

TJ = 70 + 45(0.84) = 108°C

Input Voltage vs Operating Frequency Considerations

The absolute maximum input supply voltage for the LT3434is specified at 60V. This is based solely on internal semi-conductor junction breakdown effects. Due to internalpower dissipation the actual maximum VIN achievable in aparticular application may be less than this.

A detailed theoretical basis for estimating internal powerloss is given in the section Thermal Considerations. Notethat AC switching loss is proportional to both operatingfrequency and output current. The majority of AC switch-ing loss is also proportional to the square of input voltage.

For example, while the combination of VIN = 40V, VOUT =5V at 2A and fOSC = 200kHz may be easily achievable,simultaneously raising VIN to 60V and fOSC to 700kHz isnot possible. Nevertheless, input voltage transients up to60V can usually be accommodated, assuming the result-

ing increase in internal dissipation is of insufficient timeduration to raise die temperature significantly.

A second consideration is controllability. A potential limi-tation occurs with a high step-down ratio of VIN to VOUT,as this requires a correspondingly narrow minimum switchon time. An approximate expression for this (assumingcontinuous mode operation) is given as follows:

tON(MIN) = VOUT + VF/VIN(fOSC)

where:

VIN = input voltageVOUT = output voltageVF = Schottky diode forward dropfOSC = switching frequency

A potential controllability problem arises if the LT3434 iscalled upon to produce an on time shorter than its typicalvalue of 250ns. Feedback loop action will lower thenreduce the VC control voltage to the point where some sortof cycle-skipping or Burst Mode behavior is exhibited.

In summary:

1. Be aware that the simultaneous requirements of highVIN, high IOUT and high fOSC may not be achievable inpractice due to internal dissipation. The Thermal Con-siderations section offers a basis to estimate internalpower. In questionable cases a prototype supply shouldbe built and exercised to verify acceptable operation.

2. The simultaneous requirements of high VIN, low VOUTand high fOSC can result in an unacceptably shortminimum switch on time. Cycle skipping and/or BurstMode behavior will result although correct output volt-age is usually maintained.

FREQUENCY COMPENSATION

Before starting on the theoretical analysis of frequencyresponse the following should be remembered—the worsethe board layout, the more difficult the circuit will be tostabilize. This is true of almost all high frequency analogcircuits. Read the Layout Considerations section first.Common layout errors that appear as stability problemsare distant placement of input decoupling capacitor and/or

LT3434

223434fb

APPLICATIO S I FOR ATIO

WU UUFigure 14. Overall Loop Response

Figure 13. Model for Loop Response

catch diode and connecting the VC compensation to aground track carrying significant switch current. In addi-tion the theoretical analysis considers only first order non-ideal component behavior. For these reasons, it is importantthat a final stability check is made with production layoutand components.

The LT3434 uses current mode control. This alleviatesmany of the phase shift problems associated with theinductor. The basic regulator loop is shown in Figure 12.The LT3434 can be considered as two gm blocks, the erroramplifier and the power stage.

Figure 13 shows the overall loop response with a 470pF VCcapacitor and a typical 100µF tantalum output capacitor.The response is set by the following terms:

Error amplifier: DC gain is set by gm and RO:

EA Gain = 650µ • 1.5M = 975 Ω

The pole set by CF and RL:

EA Pole = 1/(2π • 1.5M • 470pF) = 226Hz

Unity gain frequency is set by CF and gm:

EA Unity Gain Frequency = 650µF/(2π • 470pF)

= 220kHz

Powerstage: DC gain is set by gm and RL (assume 10Ω):

PS DC Gain = 6 • 10 = 60

Pole set by COUT and RL:

PS Pole = 1/(2π • 100µF • 10) = 159Hz

Unity gain set by COUT and gm:

PS Unity Gain Freq = 6/(2π • 100µF) = 94kHz.

Tantalum output capacitor zero is set by COUT and COUTESR

Output Capacitor Zero = 1/(2π • 100µF • 0.1) = 15.9kHz

The zero produced by the ESR of the tantalum outputcapacitor is very useful in maintaining stability. If the ESRof the output capacitor is low or better transient responseis required, a zero can be added to the loop using a resistor(RC) in series with the compensation capacitor (CC). As

–

+

CURRENT MODEPOWER STAGE

gm = 6Ω

gm = 650µΩ

1.25V

VC

LT3434

ERRORAMP

1.5MRC

R1

FB12

11

SW

SW

2

5

ESR

OUTPUT

R2

COUT

3434 F13

CFB

CF

CC

FREQUENCY (Hz)

0

PHASE (DEG)

120

80

40

160

180

–80

GAIN

(dB)

0

40

–40

80

100

100 1k 10k 100k

3434 F14

1M10

VOUT = 3.3VCOUT = 100µF, 0.1ΩCF = 470pFRC = 10kCC = 4700pFILOAD = 1A

the value of RC is increased, transient response willgenerally improve but two effects limit its value. First, thecombination of output capacitor ESR and a large RC maystop loop gain rolling off altogether. Second, if the loopgain is not rolled off sufficiently at the switching frequencyoutput ripple will perturb the VC pin enough to causeunstable duty cycle switching similar to subharmonicoscillation. This may not be apparent at the output. Small-signal analysis will not show this since a continuous timesystem is assumed.

When checking loop stability the circuit should be oper-ated over the application’s full voltage, current and tem-perature range. Any transient loads should be applied andthe output voltage monitored for a well-damped behavior.

LT3434

233434fb

PACKAGE DESCRIPTIO

U

FE Package16-Lead Plastic TSSOP (4.4mm)(Reference LTC DWG # 05-08-1663)

Exposed Pad Variation BC

FE16 (BC) TSSOP 0204

0.09 – 0.20(.0035 – .0079)

0° – 8°

0.25REF

0.50 – 0.75(.020 – .030)

4.30 – 4.50*(.169 – .177)

1 3 4 5 6 7 8

10 9

4.90 – 5.10*(.193 – .201)

16 1514 13 12 11

1.10(.0433)

MAX

0.05 – 0.15(.002 – .006)

0.65(.0256)

BSC

2.94(.116)

0.195 – 0.30(.0077 – .0118)

TYP

2RECOMMENDED SOLDER PAD LAYOUT

0.45 ±0.05

0.65 BSC

4.50 ±0.10

6.60 ±0.10

1.05 ±0.10

2.94(.116)

3.58(.141)

3.58(.141)

MILLIMETERS(INCHES) *DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.150mm (.006") PER SIDE

NOTE:1. CONTROLLING DIMENSION: MILLIMETERS

2. DIMENSIONS ARE IN

3. DRAWING NOT TO SCALE

SEE NOTE 4

4. RECOMMENDED MINIMUM PCB METAL SIZE FOR EXPOSED PAD ATTACHMENT

6.40(.252)BSC

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

LT3434

243434fb

Linear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 FAX: (408) 434-0507 www.linear.com © LINEAR TECHNOLOGY CORPORATION 2004

LT 0306 REV B PRINTED IN USA

RELATED PARTSPART NUMBER DESCRIPTION COMMENTS

LT1074/LT1074HV 4.4A (IOUT), 100kHz, High Efficiency Step-Down DC/DC Converters VIN: 7.3V to 45V/64V, VOUT(MIN): 2.21V, IQ: 8.5mA,ISD: 10µA, DD5/7, TO220-5/7

LT1076/LT1076HV 1.6A (IOUT), 100kHz, High Efficiency Step-Down DC/DC Converters VIN: 7.3V to 45V/64V, VOUT(MIN): 2.21V, IQ: 8.5mA,ISD: 10µA, DD5/7, TO220-5/7

LT1676 60V, 440mA (IOUT), 100kHz, High Efficiency Step-Down DC/DC VIN: 7.4V to 60V, VOUT(MIN): 1.24V, IQ: 3.2mA, ISD: 2.5µA,Converter S8

LT1765 25V, 2.75A (IOUT), 1.25MHz, High Efficiency Step-Down DC/DC VIN: 3V to 25V, VOUT(MIN): 1.20V, IQ: 1mA, ISD: 15µA,Converter SO-8, TSSOP16E

LT1766 60V, 1.2A (IOUT), 200kHz, High Efficiency Step-Down DC/DC VIN: 5.5V to 60V, VOUT(MIN): 1.20V, IQ: 2.5mA, ISD: 25µA,Converter TSSOP16/E

LT1767 25V, 1.2A (IOUT), 1.25MHz, High Efficiency Step-Down DC/DC VIN: 3V to 25V, VOUT(MIN): 1.20V, IQ: 1mA, ISD: 6µA,Converter MS8/E

LT1776 40V, 550mA (IOUT), 200kHz, High Efficiency Step-Down DC/DC VIN: 7.4V to 40V, VOUT(MIN): 1.24V, IQ: 3.2mA, ISD: 30µA,Converter N8, S8

LTC®1875 1.5A (IOUT), 550kHz, Synchronous Step-Down DC/DC Converter VIN: 2.7V to 6V, VOUT(MIN): 0.8V, IQ: 15µA, ISD: <1µA,TSSOP16

LT1940 Dual 1.2A (IOUT), 1.1MHz, High Efficiency Step-Down DC/DC VIN: 3V to 25V, VOUT(MIN): 1.2V, IQ: 3.8mA, MS10Converter

LT1956 60V, 1.2A (IOUT), 500kHz, High Efficiency Step-Down DC/DC VIN: 5.5V to 60V, VOUT(MIN): 1.20V, IQ: 2.5mA, ISD: 25µA,Converter TSSOP16/E

LT1976 60V, 1.5A (IOUT), 200kHz, Step-Down DC/DC VIN: 3V to 60V, VOUT(MIN): 1.25V, IQ: 100µA, ISD: 4µA,Converter TSSOP16E

LT3010 80V, 50mA, Low Noise Linear Regulator VIN: 1.5V to 80V, VOUT(MIN): 1.28V, IQ: 30µA, ISD: <1µA,MS8E

LTC3407 Dual 600mA (IOUT), 1.5MHz, High Efficiency Step-Down DC/DC VIN: 2.5V to 5.5V, VOUT(MIN): 0.6V, IQ: 40µA MS10Converter

LTC3412 2.5A (IOUT), 4MHz, Synchronous Step-Down DC/DC Converter VIN: 2.5V to 5.5V, VOUT(MIN): 0.8V, IQ: 60µA, ISD: <1µA,TSSOP16E

LTC3414 4A (IOUT), 4MHz, Synchronous Step-Down DC/DC Converter VIN: 2.25V to 5.5V, VOUT(MIN): 0.8V, IQ: 64µA, ISD: <1µA,TSSOP20E

LT3430 60V, 2.5A (IOUT), 200kHz, High Efficiency Step-Down DC/DC VIN: 5.5V to 60V, VOUT(MIN): 1.20V, IQ: 2.5mA, ISD: 30µA,Converter TSSOP16E

LT3431 60V, 2.5A (IOUT), 500kHz, High Efficiency Step-Down DC/DC VIN: 5.5V to 60V, VOUT(MIN): 1.20V, IQ: 2.5mA, ISD: 30µA,Converter TSSOP16E

LT3433 60V, 400mA (IOUT), 200kHz, Buck-Boost DC/DC Converter VIN: 5V to 60V, VOUT: 3.3V to 20V, IQ: 100µA, TSSOP-16E

LTC3727/LTC3727-1 36V, 500kHz, High Efficiency Step-Down DC/DC Controllers VIN: 4V to 36V, VOUT(MIN): 0.8V, IQ: 670µA, ISD: 20µA,QFN-32, SSOP-28