Latch vs Flip Flop

description

Transcript of Latch vs Flip Flop

-

"Latch" Vs "Flip Flop"Welcome to the most popular title on this Blog ;-))))) !!!

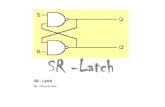

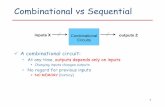

A flip-flop is Edge sensitive: Output only changes on rising (or falling) edge of clock.A latch is Level sensitive: Output changes whenever clock/Enable is high (or low)

A common implementation of a flip-flop is a pair of latches (Master/Slave flop).

Latches are sometimes called transparent latches, because they are transparent (input directly connected to output) when the clock is high.

The clock to a latch is primarily called the enable.

For more information have a look at the picture below.

Deprecated Hardware:

Latches:Use flops, not latches1. Latch-based designs are susceptible to timing problems2. The transparent phase of a latch can let a signal leak through a latch causing the signal to affect the output one clock cycle too early3. Its possible for a latch-based circuit to simulate correctly, but not work in real hardware, because the timing delays on the real hardware dont match thosepredicted in synthesis

4.

Flip-flops:Limit yourself to D-type flip-flops1. Some FPGA and ASIC cell libraries include only D-type flip flops. Others, such as Alteras APEX FPGAs, can be configured as D, T, JK, or SR flip-flops.2.

For every signal in your design, know whether it should be a flip-flop or combinational. Examine the log file e.g. dc shell.log to see if the flip-flops in yourcircuit match your expectations, and to check that you dont have any latches in your design.Do not assign a signal to itself (e.g. a

-

Articles you may have missed:

Comparison of VHDL to Other Hardware Description Languages1. behavioral & RTL2. We are now blog.digitalelectronics.co.in3. Best known modelling practices for gigabit serial design - Live Webcast4. VSIDE - VSDSP Integrated Development Environment5. Driving Flexibility into Automotive Electronics Design6. Data Management for Hardware Design Teams7. "Latch" Vs "Flip Flop"8. Are latches really bad for a design?9. Functionally debug in RTL source using Identify RTL Debugger10. SPARK: A Parallelizing Approach to the High-Level Synthesis of Digital Circuits11. Boosting RTL Verification with High-Level Synthesis12.

Blog this! | Print this post! | Couch mode! | " "Latch" Vs "Flip Flop" " is copyrighted by Murugavel Ganesan using Google @ The Digital Electronics Network . You can follow him on LinkedIn , Twitter ,Facebook or sign-up for email notifications.

"Latch" Vs "Flip Flop" http://blog.digitalelectronics.co.in/2004/12/latch-vs-flip-flop.html

2 of 2 6/9/2015 12:24 PM