L3 instruction-execution-steps

Click here to load reader

-

Upload

rsamurti -

Category

Engineering

-

view

209 -

download

0

Transcript of L3 instruction-execution-steps

General Aspects of Computer Organization(Lecture-3)

R S Ananda Murthy

Associate ProfessorDepartment of Electrical & Electronics Engineering,

Sri Jayachamarajendra College of Engineering,Mysore 570 006

R S Ananda Murthy General Aspects of Computer Organization

Specific Learning Outcomes

After completing this lecture the student should be able to –Describe Von Neumann (Princeton) architecture.Describe Harvard architecture.Describe the function of MAR and MDR in the CPU.Explain steps involved in executing an instruction.Describe features of CISC and RISC computers.

R S Ananda Murthy General Aspects of Computer Organization

Von Neumann (Princeton) Architecture

CPU

ProgramMemory

DataMemory

Address Bus

Control Bus

Data Bus

Program and data memory share the same address space,address and data buses.Speed is limited because simultaneous access of programand data memory by CPU is impossible.Preferred in general purpose microprocessors where CPUand memory are separate chips.

R S Ananda Murthy General Aspects of Computer Organization

Harvard Architecture

CPUData

Memory

Address Bus

Control Bus

Data BusProgramMemory

Address Bus

Data Bus

Control Bus

Program and data memory have different address space,address and data buses.Execution speed is increased because simultaneousaccess of program and data memory by CPU is possible.Preferred in microcontrollers where program memory, datamemory and CPU are in a single chip.

R S Ananda Murthy General Aspects of Computer Organization

MAR and MDR in CPU

MAR

PC

MDR

R0R1R2:

Rn

IR

CUALU

ProgramMemory

DataMemory

Address Bus

Control Bus

Data Bus

Memory Address Register (MAR) stores the address of theoperand to be fetched from memory to execute theinstruction.Memory Data Register (MDR) stores the operand (data)after it is fetched from memory.

R S Ananda Murthy General Aspects of Computer Organization

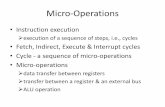

Steps Followed by CPU in Instruction Execution

1 Fetch the instruction from the program memory locationpointed by PC into IR.

2 Determine the type of instruction present in the IR. This isdone by CU.

3 If the instruction uses an operand in memory, determine itsaddress and place it in MAR.

4 Fetch the operand and put it in MDR, and if needed, copy itinto a CPU register.

5 Execute the instruction. This is done by the CU.6 Change the PC to point to the next instruction.7 Go to Step 1 to begin executing the next instruction.

R S Ananda Murthy General Aspects of Computer Organization

An Imaginary Computer

MAR

PC

MDR

R0R1R2

:R7

IR

CUALU

Address Bus

Control Bus

Data Bus

CPU

0x00000x00010x0002

0xFFFF

MEMORY Address in Hex

16 bits

16 bits

8 bits

8 bits8 bits8 bits

8 bits

8 bits16 bits

8 bits

:

Blocks in side CPU are interconnected by internal address,data, and control buses.There are eight internal registers R0 to R7, each of 8 bitswidth.When we want to add two numbers, one number must bepresent in R0 and the other one should be present in anyother register. The sum is placed in R0.Instructions can be 1-byte, 2-bytes, or 3-bytes long.

R S Ananda Murthy General Aspects of Computer Organization

Instructions Recognized by Imaginary Computer

LDR Rn, MemAdr -- A three-byte instruction

1010 0 NNNMemAdr Low ByteMemAdr High Byte

n NNN0 0001 0012 010

3-bit Code forRegisters

3 0114 1005 1016 1107 111

Opcode

Copies the data present at MemAdrto the register Rn

ADD R0,Rn -- A one-byte instruction

11000 NNN

Adds contents of R0 and Rn and placesthe sum in the register R0

Opcode

Operands

R S Ananda Murthy General Aspects of Computer Organization

Instructions Recognized by Imaginary Computer

MVI Rn, NextByte -- A two-byte instruction

1010 1 NNNData Byte

n NNN0 0001 0012 010

3-bit Code forRegisters

3 0114 1005 1016 1107 111

Opcode

Copies the next data byte to the register Rn.

HALT -- A one-byte instruction

00000000

Stops incrementing of program counter.

Opcode

Operand

R S Ananda Murthy General Aspects of Computer Organization

Adding Two Numbers using Imaginary Computer

Memory

C100:

A03010A13110

LDR R0,0x1030

LDR R1,0x1031

ADD R0,R1HALT

Hex Address

CDEF

0x00000x00010x00020x00030x00040x00050x00060x0007

0x1030:

0x1031AugendAddend

Data

How is opcode A0 obtained?

How is opcode A1 obtained?

How is opcode C1 obtained?

How many bytes in program?

Trace through the programusing steps given earlier.

After storing the program and data in the memory asshown above we have to initialize PC with the startingaddress 0x0000 and then give a command to the computerto start execution of the program.

R S Ananda Murthy General Aspects of Computer Organization

Adding Two Numbers Another Way

Memory

A8CDA9EFC100

MVI R0,0xCD

ADD R0,R1HALT

Hex Address

0x00000x00010x00020x00030x00040x0005

How is opcode A8 obtained?

How is opcode C1 obtained?

How many bytes in program?

MVI R1,0xEF How is opcode A9 obtained?

After storing the program and data in the memory asshown above we have to initialize PC with the startingaddress 0x0000 and then give a command to the computerto start execution of the program.Trace through the program using the steps given earlier.

R S Ananda Murthy General Aspects of Computer Organization

CISC and RISC

On the basis of type of instructions and how they areexecuted, computers are roughly classified into two types –Complex Instruction Set Computers (CISC) and ReducedInstruction Set Computers (RISC).CISC and RISC both have their merits and demerits.Present trend is to incorporate the best features of bothCISC and RISC in processor design to get optimumperformance at optimum cost.

R S Ananda Murthy General Aspects of Computer Organization

Features of CISC

Traditionally most of the processors made in 1970s and1980s were CISC adopting Princeton architecture.Variable instruction length. For eg., there may be 1-byte,2-byte, or 3-byte instructions as in case of Intel 8051 MCU.As compared to RISC, CISC processors generally havelesser number of internal registers in the CPU.Variable instruction cycle time. Instruction cycle is the timetaken to execute an instruction. More complex instructionstake longer time to execute.Large number of instructions in the instruction set.Typically there can be more than 200 instructions in theinstruction set.

R S Ananda Murthy General Aspects of Computer Organization

Features of CISC

Generally, in CISC a portion of R/WM is used as stack tostore data while branching to subroutines.Generally, in CISC instructions are available to operate ondata present in the memory directly without bringing it intoa register in side the CPU.For a given task, a program in CISC results in smaller codesize.Typically in CISC instructions are decoded by amicroprogram which is stored in CU. Microprogramimplementation requires more number of transistors to beintegrated on the chip.Decoding of instructions using microprogram in CISCslows down execution.

R S Ananda Murthy General Aspects of Computer Organization

Features of RISC

Traditionally RISC implementation is becoming popularsince 1990s.Fixed instruction size. For eg. in AVR MCU which is aRISC processor, almost all instructions are 2-bytes inlength with only a few 4-byte instructions.Large number of internal registers in the CPU. For eg. AVRMCU has 32 internal registers.Because of large number of internal registers, usage ofstack to store data may not be essential as in CISC.Smaller and simpler instruction set. Typically instructionset may have less than 200 instructions.For a given task, assembly language programming of RISCmachines generally requires more effort as compared toCISC processors.

R S Ananda Murthy General Aspects of Computer Organization

Features of RISC

Due to the reason mentioned above, it is more convenientto program RISC processors using higher level languageslike C or C++.Fixed instruction cycle time for most of the instructions.Many modern RISC processors adopt Harvard architectureto speed up program execution.Generally, in RISC it is not possible to perform arithmeticand logical operations on data present in the memorydirectly without bringing it into a register in side the CPU.In RISC, instruction decoding in CU is done usinghardware and not by using a microprogram to speed upinstruction execution.

R S Ananda Murthy General Aspects of Computer Organization

License

This work is licensed under aCreative Commons Attribution 4.0 International License.

R S Ananda Murthy General Aspects of Computer Organization