jesd51-8

-

Upload

marcio-silva -

Category

Documents

-

view

43 -

download

2

Transcript of jesd51-8

JEDECSTANDARD

Integrated Circuit Thermal TestMethod Environmental Conditions —Junction-to-Board

JESD51-8

OCTOBER 1999

ELECTRONIC INDUSTRIES ALLIANCE

JEDEC Solid State Technology Association

NOTICE

EIA/JEDEC standards and publications contain material that has been prepared, reviewed, andapproved through the JEDEC Board of Directors level and subsequently reviewed and approvedby the EIA General Counsel.

EIA/JEDEC standards and publications are designed to serve the public interest througheliminating misunderstandings between manufacturers and purchasers, facilitatinginterchangeability and improvement of products, and assisting the purchaser in selecting andobtaining with minimum delay the proper product for use by those other than JEDEC members,whether the standard is to be used either domestically or internationally.

EIA/JEDEC standards and publications are adopted without regard to whether or not theiradoption may involve patents or articles, materials, or processes. By such action JEDEC does notassume any liability to any patent owner, nor does it assume any obligation whatever to partiesadopting the EIA/JEDEC standards or publications.

The information included in EIA/JEDEC standards and publications represents a sound approachto product specification and application, principally from the solid state device manufacturerviewpoint. Within the JEDEC organization there are procedures whereby an EIA/JEDECstandard or publication may be further processed and ultimately become an ANSI/EIA standard.

No claims to be in conformance with this standard may be made unless all requirements stated inthe standard are met.

Inquiries, comments, and suggestions relative to the content of this EIA/JEDEC standard orpublication should be addressed to JEDEC Solid State Technology Association, 2500 WilsonBoulevard, Arlington, VA 22201-3834, (703)907-7560/7559 or www.jedec.org

Published by©ELECTRONIC INDUSTRIES ALLIANCE 1999

Engineering Department2500 Wilson Boulevard

Arlington, VA 22201-3834

This document may be downloaded free of charge, however EIA retains thecopyright on this material. By downloading this file the individual agrees not to

charge or resell the resulting material.

PRICE: Please refer to the currentCatalog of JEDEC Engineering Standards and Publications or call Global Engineering

Documents, USA and Canada (1-800-854-7179), International (303-397-7956)

Printed in the U.S.A.All rights reserved

PLEASE!

DON”T VIOLATETHE

LAW!

This document is copyrighted by the Electronic Industries Alliance and may not bereproduced without permission.

Organizations may obtain permission to reproduce a limited number of copiesthrough entering into a license agreement. For information, contact:

JEDEC Solid State Technology Association2500 Wilson Boulevard

Arlington, Virginia 22201-3834or call (703) 907-7559

JEDEC Standard No. 51-8

-i-

INTEGRATED CIRCUIT THERMAL TEST METHODENVIRONMENTAL CONDITIONS – JUNCTION-TO-BOARD

CONTENTS

1 Scope 1

2 Normative references 1

3 Definitions, symbols, and abbreviations 2

4 Specification of environmental conditions 24.1 Thermal test board 24.2 Ring style cold plate 24.2.1 Material 24.2.1 Clamp location 34.2.3 Example designs 34.3 Insulation requirements 34.4 Fluid temperature 44.5 Board temperature measurement 4

5 Measured and calculated parameters 55.1 Junction-to-board thermal resistance 55.2 Temperature sensitive parameter 55.3 Determination using Kfactor 65.4 Calibration equation 6

6 Test procedure 66.1 TSP calibration 66.2 Thermal equilibrium 66.3 Initial readings 66.4 Apply power 66.5 Steady state 66.6 Steady state measurements 7

7 Usage 77.1 Thermal simulation models 77.2 Simulation validation 77.3 ΨJB junction-to-board thermal characterization parameter 7

8 Test conditions to be reported 8

Figures1 Illustration of ring style cold plate 32 Top view with insulation removed 4

Tables1 Thermal measurement test conditions and data parameters 8

Annex A 9

JEDEC Standard No. 51-8

-ii-

JEDEC Standard No. 51-8Page 1

INTEGRATED CIRCUIT THERMAL TEST METHODENVIRONMENTAL CONDITIONS – JUNCTION-TO-BOARD

(From JEDEC Board Ballot JCB-99-09, formulated under the cognizance of the JC15.1 Committee onThermal Characterization.)

1 Scope

This standard specifies the environmental conditions necessary for determining the junction-to-boardthermal resistance, RθJB, and defines this term. The RθJB thermal resistance is a figure of merit forcomparing the thermal performance of surface mount packages mounted on a standard board. Thisspecification should be used in conjunction with the overview document JESD51, "Methodology for theThermal Measurement of Component Packages (Single Semiconductor Device)" [1] and the electricaltest procedures described in EIA/JESD51-1, "Integrated Circuit Thermal Measurement Method (SingleSemiconductor Device)" [2]. The environmental conditions described in this document are specificallydesigned for testing of integrated circuit devices that are mounted on standard test boards with twointernal copper planes [3]. This standard is not applicable to packages that have asymmetric heat flowpaths to the printed circuit board caused by such thermal enhancements as fused leads (leads connectedto the die pad) or power style packages with the exposed heat slug on one side of the package.

2 Normative references

The following standards contain provisions that, through reference in this text, constitute provisions ofthis standard. At the time of publication, the editions indicated were valid. All standards are subject torevision, and parties to agreements based on this standard are encouraged to investigate the possibility ofapplying the most recent editions of the standards indicated below.

[1] JESD51, “Methodology for the Thermal Measurement of Component Packages (SingleSemiconductor Device)”

[2] JESD51-1, “Integrated Circuit Thermal Measurement Method – Electrical Test Method (SingleSemiconductor Device)”

[3] JESD51-7, “High Effective Thermal Conductivity Test for Leaded Surface Mount Packages”

[4] JESD51-6, “Integrated Circuit Thermal Test Method Environmental Conditions - ForcedConvection (Moving Air)”

JEDEC Standard No. 51-8Page 2

3 Definitions, symbols, and abbreviations

For the purposes of this standard, the following definitions apply:

shadow: maximum overall dimensions on the board that would be occupied by the package. For theBGA package, the shadow is the substrate size. For a QFP package, the shadow is the lead tip to tipsize.

RθJB: Junction-to-board thermal resistance as defined in this specification. θJB is an alternatesymbol. When Greek letters are not available, the symbols are typed as RthJB or Theta-JB.

ΨJB: Junction-to-board thermal characterization parameter measured using the method defined inIntegrated Circuit Thermal Test Method Environmental Conditions - Forced Convection (MovingAir) [5]. When Greek letters are not available, the symbol is typed as Psi-JB.

TSP: Temperature-sensitive parameter

Refer to the document JESD51, JESD51-1, and JESD51-2 for a general list of terminology.

4 Specification of environmental conditions

4.1 Thermal test board

The printed circuit board used to mount the devices shall be specified in JESD51-7 "High EffectiveThermal Conductivity Test for Leaded Surface Mount Packages" [3]. This specification can be extendedto testing other surface mount integrated circuit packages with the appropriate test board specificationwith two internal planes.

4.2 Ring style cold plate

The ring style cold plate is a fluid cooled cold plate that clamps both sides of the test board such that theheat flows from the package radially in the plane of the test board.

4.2.1 Material

The cold plate is machined from copper or copper alloy (conductivity greater than 300 W/m•K such asC14500 or C14700) and then nickel plated. The ring style cold plate is illustrated in figures 1 and 2.There is a square hole in the cold plate to accommodate the package.

JEDEC Standard No. 51-8Page 3

4.2 Ring style cold plate (cont’d)

4.2.2 Clamp location

The cold plate is clamped onto the solder mask covered traces on the board at a minimum of 5 mm fromthe package (the shadow of the package). The package shall be centered +/- 10% of the distance from thepackage shadow to the clamp. The cold plate clamp area must be a minimum of 4 mm wide. The testboard design must have the vias for hand soldered jumper wires close enough to the edge of the boardthat the vias will not interfere with clamping of the cold plate. Clamping force should be evenly appliedand be sufficient that the board will not move with respect to the ring if a 200 gram force is applied to theboard. The measurement results are not sensitive to clamping force. Thermal grease does not have to beused.

4.2.3 Example designs

Examples of the ring cold plate design are included as figures A1 and A2 in annex A.

4.3 Insulation requirements

The package opening in the top and bottom of the cold plate are insulated. The insulation material with aconductivity less than 0.1 W/m•K is faced with a low emissivity aluminized plastic film. There shouldbe a 1 to 5 mm air gap between the package and the insulation and between the bottom of the test boardand the insulation on the bottom of the fixture. If solder mask over the traces on the board do not providesufficient electrical insulation, tape not exceeding 0.075 mm in thickness may be used to electricallyinsulate the board traces such that the package can be tested.

Figure 1 — Illustration of the ring style cold plate RθJB test fixture in cross section

Junction TemperatureBoard Temperature Thermocouple Soldered to Middle Lead

Insulate with tape if necessary

5 mm Minimum

1 to 5 mm Gap Insulation to Board or Insulation to Package

Insulation Water Channel

JEDEC Standard No. 51-8Page 4

4.3 Insulation requirements (cont’d)

Figure 2 — Top View with the insulation removed(To simplify the illustration, the traces on the test board are not shown. The thermocouple is attached to a

board trace at the edge of the package in the location shown.)

4.4 Fluid temperature

The incoming cooling fluid should be controlled at the ambient room temperature in a range of +2 °Cto -5 °C such that it does not change temperature more than 0.2 °C during the test. In addition, the blocktemperature where it contacts the board shall be uniform within 0.4 °C. Variations in block temperatureare more likely a problem when using low specific heat dielectric fluids.

4.5 Board temperature measurement

The board temperature for this measurement shall be determined by a 40 gauge thermocouple which issoldered in place. Since type T thermocouples are easily soldered, type T is preferred. Type J or K maybe also be used. Contact to the board trace or package lead foot should be verified by electricalconductivity. To reduce temperature gradients in the wire approaching the thermocouple junction, asmall amount of thermally conductive epoxy is placed over the thermocouple junction and about one mmof wire extending from the thermocouple junction. The epoxy dot shall be no larger than 3 mm indiameter. The thermocouple meter must electrically float the thermocouple to avoid electricalinteractions with any voltages applied to the package during test.

Thermocouple Soldered to Test Board Trace

PBGA Package

Ring Cold Plate Shown Without Insulation Over Package

JEDEC Standard No. 51-8Page 5

4.5 Board temperature measurement (cont’d)

For a leaded package, the thermocouple is attached to the foot of a package lead halfway along the sideof the package. For a rectangular package, the lead is on one of the longer sides. The thermocouple isattached to the lead foot where the lead is joined to the test board. For an area array surface mountpackage, the thermocouple is attached to a test board trace halfway along one side of the package. Thesolder mask should be removed to allow attaching the thermocouple directly to the trace. The traceshould be a trace to which the package is soldered. The thermocouple junction must be within 1 mm ofthe package body.

Although the measurement is not applicable to packages with asymmetric heat flow paths to the printedcircuit board, caused by such thermal enhancements as fused leads (leads connected to the die pad) orpower style packages with exposed heat slug on one side of the package, there are cases where the fusedleads cause a relative minor asymmetry in the heat flow. For those cases, if that center lead is stamped oretched from the same piece of material as the die pad in a “thermal lead” or “fused lead” configuration,the lead adjacent to the “fused lead” is used for the measurement.

5 Measured and calculated parameters

5.1 Junction-to-board thermal resistance

The junction-to-board thermal resistance is determined from equation (1):

RθJB = (TJ - TB)/PH (1)

where

RθJB = thermal resistance (°C/W) from junction-to-board as described by this specificationTJ = junction temperature (°C) when the device has achieved a steady-state after application of PH

TB = board temperature (°C) at steady statePH = power dissipation (W) which produced the change in junction temperature

5.2 Temperature-sensitive parameter

As described in the reference [2], a temperature-sensitive parameter (TSP) is used to sense the change intemperature of the junction operating area due to the application of electrical power to the device. Inequation terms,

∆TJ = (∆TSP × Kfactor) (2)

where

∆TSP = change in the TSP caused by the application of PH

Kfactor = is the quotient of the junction temperature change to the temperature sensitive parameterchange in the linear region of the temperature-sensitive parameter temperature relationship, typicallyspecified in units of °C/mV; usually applicable to semiconductor devices using a forward biasedtemperature sensitive parameter.

JEDEC Standard No. 51-8Page 6

5.3 Determination using Kfactor

The junction-to-board thermal resistance can then be determined by equation (3):

RθJB = (TB0 + [∆TSP × Kfactor] - TBSS)/PH (3)

where

TB0 = Initial board temperature before heating power is appliedTBSS = Final board temperature when steady state has been reached.

5.4 Calibration equation

A calibration equation may also be used to determine the junction temperature as specified in reference[2].

6 Test Procedure

6.1 TSP calibration

Prior to making actual thermal measurements, the temperature-sensitive parameter shall be empiricallycalibrated using the procedure in section 3.3 of the reference [2].

6.2 Thermal equilibrium

Place the package and test board in the ring cold plate. Prior to recording the initial conditions of thethermal test, verify that the device has reached a state of equilibrium with the ambient temperature. Toverify that stabilization has occurred, wait an initial 5 minutes minimum, then record the TSP, wait anadditional 5 minutes and record a second TSP. If ∆TJ as determined by the TSP measurement is lessthan or equal to 0.2 °C, then equilibrium has been achieved. If equilibrium has not occurred, thencontinue for additional 5 minute intervals.

6.3 Initial readings

After equilibrium has been reached, record the values for the TSP and the initial board temperature TB0.

6.4 Apply power

The power levels shall be chosen such that the junction temperature rise during testing is between 15 °Cand 30 °C. Apply the heating voltage (VH) and the heating current (IH) to the device.

6.5 Steady state

For a test measurement to be completed, verification that thermal steady state has been reached shall bedone before the final readings can be taken. Steady-state shall be determined as required in section 3.6 ofreference [2].

JEDEC Standard No. 51-8Page 7

6.6 Steady state measurements

After a steady-state has been reached, record the values for the TSP, the heater voltage (VH), the heatercurrent (IH), the time required to reach steady state (tHss), and the final board temperature at the end ofthe test (TBss).

7 Usage

7.1 Thermal simulation models

The junction-to-board thermal resistance, RθJB, will find use as an indicator of thermal performance forincorporation into board level thermal simulation models. How the information is used in a board levelsimulation and the resulting accuracy will depend on the simulation software. Since RθJB is primarily afigure of merit, the resulting accuracy of the board level simulations will be less than could be obtainedwith a more detailed model.

7.2 Simulation validation

Another use of RθJB will be the validation of package simulation models by providing defined boundaryconditions for simulation. Since the thermal test board can contribute up to 50% of the thermalresistance measured in this test, it is required that the test board be accurately modeled. Actual physicalmeasurements of the test board are needed for accurate models. The junction-to-board determined bythis specification must not be confused with similar measurements obtained with the “double cold plate”apparatus.

7.3 ΨJB junction-to-board thermal characterization parameter

Junction-to-board thermal resistance, RθJB, must not be confused with a junction-to-board thermalcharacterization parameter, ΨJB, determined using the methods specified in “Integrated Circuit ThermalTest Method Environmental Conditions - Forced Convection (Moving Air)”. Frequently, the junction-to-board thermal resistance will be larger than junction-to-board thermal characterization parameter.

JEDEC Standard No. 51-8Page 8

8 Test conditions to be reported

The values listed in table 1, which are needed to describe this test and the results, must be reported whenpublishing.

Table 1 — Thermal measurement test conditions and data parametersMeasurement Area Condition Parameters Data Parameters and ResultsDevice Identification Device Identification DateEnvironmental Cold Plate Drawing number

Test Board Specification (and drawing number)Thermocouple Type and gaugeThermocouple attachment location

Measurements TB0 (°C)TBSS (°C)VH (V)IH (mA)tHss (s)Im (mA)Kfactor (°C/mV)

Vf (V)∆TJ (°C)PH (W)RθJB (°C/W)

JEDEC Standard No. 51-8Page 9

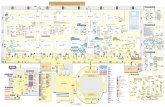

Annex A – Ring cold plate design example

33.0

87.0

0.0

6.0

12.016.0

BLIND HOLE THROUGH HOLE0.0

Figure A1a - Drawing of bottom piece of ring cold plate fixture designed for packages with footprint less than 30 mm in longest dimension.Fabricated from copper and then nickel plated. All dimensions are basic. If 8-32 screws are used instead of M4 to center the test board,threaded holes should be moved 0.1 mm further from the center line of the fixture. Only the externally visible drilled holes are shown in side views.

0.0

6.0

21.0

27.025.0

45.0

63.065.069.0

85.5

98.2

104.0

DRILL AND TAP 12 PLM4

PLUG

PLUG

PLUG

PLUGPLUG

THREADED HOLESFOR ALIGNMENT POST5 PL FOR EACH BOARD SIZE

THREADED HOLES FORCLAMP, 2 PL

INLET

OUTLET

PLUG

PLUG

PLUG

0.0

6.8

19.5

36.0

40.0

60.0

80.0

84.0

100.

5

113.

2

120.

0

R3

0.0

18.0

36.0

54.0

72.0

0.0

6.0

DRILL 6 mmBLIND HOLETAP

DRILL 6 mmTAP, 8 PL

0.025

DRILL 4.5 mm 12 PL

0.0

6.0

21.0

27.025.0

45.0

63.065.069.0

85.5

98.2

104.0PLUG

PLUG

PLUG

PLUG PLUG

CLEARANCE HOLESFOR ALIGNMENT POST 5 PL FOR EACH BOARD SIZE

CLEARANCE HOLESFOR CLAMP, 2 PL

INLET

OUTLET

PLUG

PLUG

PLUG

DRILL 6mmBLIND HOLETAP

0.0

6.0

12.016.0

BLIND HOLETHROUGH HOLE

0.0

33.0

87.0

Figure A1b - Drawing of top piece of the ring cold plate fixture designed for packages with footprint less than 30 mm in longest dimension. Toppiece is shown upside down for easy of documenting dimensions. Refer to figure 1 to illustrate assembly. Fabricated from copper and thennickel plated. All dimensions are basic. Only externally visible drilled holes are shown in side views.

0.0

18.0

36.0

54.0

72.0

0.0

6.0

DRILL 6 mmTAP, 8 PL

0.025

0.0

6.8

19.5

40.0

36.0

60.0

80.0

84.0

100.

5

113.

2

120.

0

R3

JEDEC Standard No. 51-8Page 10

Annex A – Ring cold plate design example

Figure A2a - Drawing of bottom piece of ring cold plate fixture designed for packages on 101.6 mm test board. Fabricated from copper andthen nickel plated. All dimensions are basic. Only the externally visible drilled holes are shown in the side views.

DRILL AND TAP 7 PLM4

PLUG

PLUG

PLUG

PLUG

THREADED HOLESFOR ALIGNMENT POST 5 PL

THREADED HOLES FORCLAMP, 2 PL

PLUG

0.0

12.016.018.0

47.0

78.082.0

94.0

100.2

106.00

0.0

6.8

25.0

29.0

60.0

91.0

95.0

113.

2

120.

0PLUG

PLUG

PLUG

INLET

OUTLET

DRILL 6 mmBLIND HOLETAP

DRILL 6 mmTAP, 8 PL

0.025

0.0

6.0

0.0

9.0

38.0

56.0

85.0

BLIND HOLE THROUGH HOLE

0.0

6.0

12.016.0

0.0

22.0

98.0

Figure A2b - Drawing of top piece of ring cold plate fixture designed for packages on 101.6 mm test board. Fabricated from copper and thennickel plated. All dimensions are basic. Only externally visible drilled holes are shown in the side views.

DRILL 6 mmBLIND HOLETAP

DRILL 6 mmTAP, 8 PL

0.025

0.0

9.0

38.0

56.0

85.0

BLIND HOLETHROUGH HOLE

0.0

6.0

12.016.0

0.0

22.0

98.0

DRILL 4.5 mm 7 PL

PLUG

PLUG

PLUG

PLUG

CLEARANCE HOLESFOR ALIGNMENT POST 5 PL

CLEARANCE HOLESFOR CLAMP, 2 PL

PLUG

PLUG

PLUG

PLUG

Inlet

Outlet

0.0

12.016.018.0

47.0

78.082.0

94.0

100.2

106.0

0.0

6.8

25.0

29.0

60.0

91.0

95.0

113.

2

120.

0

0.0

6.0

![[XLS] · Web view8 6212.5 8 19478.2 8 8015 8 8597.35 8 4585 8 15861.9 8 4797.5 8 8597.35 8 15235 8 5153 8 8257.5 8 5592.2 8 19565.7 8 15861.9 8 7575 8 19947.5 8 10215 8 2970 8 15861.9](https://static.fdocuments.in/doc/165x107/5bc48cb809d3f274118c1b96/xls-web-view8-62125-8-194782-8-8015-8-859735-8-4585-8-158619-8-47975.jpg)

![[XLS] · Web view8 5573 8 5038.5 8 12250 8 8229.5499999999993 8 8662.33 7 5265.5 8 8103 8 8647.35 8 4093 7 5914 8 6425.5 8 10706.5 8 10000 8 10000 7 13325.27 8 6148 8 5453.5 8 7750](https://static.fdocuments.in/doc/165x107/5bd6d1de09d3f2e17c8bfdea/xls-web-view8-5573-8-50385-8-12250-8-82295499999999993-8-866233-7-52655.jpg)

![University of HawaiiTranslate this page of Hawaii System ... ÐÏ à¡± á> þÿ rŽ8 8 ‹8 8 8 8 8 8 8 8 8 8 8!8"8#8$8%8&8'8(8)8*8+8,8-8.8/808182838485868788898:8;88=8>8?8@8A8B8C8D8E8F8G8H8I8J8K8L8M8N8O8P8Q8R8S8T8U8V8W8X8Y8Z8[8\8]8^8_8](https://static.fdocuments.in/doc/165x107/5aabfa6d7f8b9a9c2e8c9b24/university-of-hawaiitranslate-this-of-hawaii-system-rz8-8-8-8-8-8-8-8-8.jpg)