Institute of Microelectronics, PKU SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006...

-

Upload

krystal-bream -

Category

Documents

-

view

212 -

download

0

Transcript of Institute of Microelectronics, PKU SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006...

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability Degradation Characteristics of

Ultra-thin Gate Dielectrics

for Nano-CMOS ApplicationJ.F. Kang

Institute of Microelectronics Peking University Beijing 100871, China

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

N. Sa, B.G. Yan, H. Yang, J.F. Yang, Z.L. Xia (IME, PKU)

X.Y. Liu, R.Q. Han, Y.Y. Wang (IME, PKU)

D.-L. Kwong (ECE, UT Austin)

H.Y. Yu (IMEC)

C. Ren, M-F. Li, D.S.H. Chan (SNDL, NUS)

Acknowledgment:

C. C. Liao, Z. H. Gan, M. Liao, J. P. Wang, and W.

Wong (SMIC)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction Reliability characteristics of ultra

thin gate dielectricsHfO2 gate stackHigh temperature annealing effectTDDB, PBTI, and NBTI

SiON in pMOS Dynamic NBTI S/D bias effect on NBTI

Summary

Outline

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction Leading-edge production technology of

CMOS has scaled down to sub 90nm

nodes.

SiON gate dielectrics are used in 90nm

and 65nm nodes technology.

High-K/metal gate stacks will be

required in sub 45nm nodes technology.

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction (SiON)NBTI in p-MOS is a critical reliability

issue for CMOS with SiON gate dielectric

NBTI is in general attributed to reaction-diffusion (R-D) model involving interfacial bond breaking followed by a diffusion process of hydrogen species (S. Mahapatra et al, IEDM2004, p.105)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

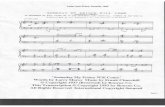

R-D model (S. Mahapatra et al, IEDM2004, p.105; S. Ogawa and N. Shiono, PRB 51, 4218, 1995)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction (SiON) Mechanisms of NBTI under various

operation modes is not clear Release of hydrogen from Si-H bonds followed by the lateral motion of protons along the interface (X.J. Zhou et al, APL 84, p.4394, 2004)

Re-passivation effect of interface trap during the post stress phase (T. Yang et al, EDL 26, p.758, 2005)

Hot carrier effect on NBTI (D. Saha et al, EDL 27, p.188, 2006)

Hole energy effect on NBTI due to broken Si-H and Si-O bonds (D. Varghese et al, EDL 26, p.527, 2005)

……

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction (SiON) The characteristics of NBTI under

various operation modes need to be identified

Dynamic NBTI has been demonstrated the significant difference with static NBTI (G. Chen et al, IRPS 2003, p.196; M. Ershov et al, APL 83, p.1647, 2003) There is few report on NBTI characteristics in S/D bias mode (N.K. Jha et al, IPRS 2005, p.524)We will address the S/D bias effect on NBTI

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction (HfO2 gate stack) Severe reliability problems exist in high

K/metal gate stacks due to high pre-existing charge trapping in the stacks (A. Shanware et al, IRPS 2003; C. Shen et al, IEDM 2004)

High temperature RTA ( >900oC) is effective to reduce the preexisting charge trapping in high K gate stack (G.D. Wilk , VLSI 2002 )

However, high temperature RTA usually causes significant EOT increase (C.S. Kang, VLSI 2002 )

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

We have demonstrated the

HfN/HfO2 gate stack is

robust thermally stable

(H. Yu et al, IEDM’03)

EOT increase is negligible

after a high temperature

annealing on the stack

(PGA)

We could expect the

excellent reliability and

sub-1 nm EOT to be

achieved simultaneously

Introduction (HfO2 gate stack)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

In this talk, I will address :

HfO2 gate stack

High temperature annealing effect on EOT and reliability

Intrinsic characteristics of TDDB, PBTI,

and NBTI in HfN/HfO2 gate stack

fabricated by high temperature process

SiONDNBT characteristics and nitrogen effect

S/D bias effect on NBTI

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

High K gate stack devices were fabricated by

using a high temperature process (a gate first

process ):

DHF-last pre-gate cleaning process

Deposition of HfO2 gate dielectrics using a MOCVD

cluster tool (deposited at 400oC followed by a 700oC PDA

in N2 for 1 min)

Deposition of TaN/HfN metal gate stack by PVD

Gate patterning by using RIE

(Followed by S/D implantations for MOSFET devices)

RTA in N2 at 950oC or 1000oC for 30s

Experiments (HfO2 gate stack)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

P+ poly-Si MOSFETs were fabricated using a 90nm CMOS technology.

SiON gate dielectrics: RTO+ Plasma Nitridation+PDA

Static and Dynamic stresses were performed @ RT and 125oC

S/D bias=0

Various S/D biases

Experiment (SiON)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction Reliability characteristics of ultra

thin gate dielectricsHfO2 gate stackHigh temperature annealing effectTDDB, PBTI, and NBTI

SiON in pMOS Dynamic NBTI S/D bias effect on NBTI

Summary

Outline

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

High temperature annealing effect

High temperature process causes the significant reduction of bulk charge trapping in HfN/HfO2 gate stack (J.F. Kang et al, ESL 8 :

G311-G313 2005) After a high temperature

(>900oC) process :

Hysteresis-

Significant reduction

Extra inversion capacitance-

Disappearance

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Scalability of HfN/HfO2 gate stack (MOSC)

(J.F. Kang et al, ESL 8 ; H. Yu et al, IEDM’03)

0.75 nm EOT (W/ SN) and 0.91 nm EOT (W/O SN) were achieved in MOSC undergoing a 1000oC PGA process

High temperature annealing effect

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Scalability of HfN/HfO2 gate stack

(MOSC)

HfN

HfO2~2.2nm

IL~0.7 nm

FGA 1000oCRTA

IL~0.9 nm

HfO2~2.0nm

HfN

The robust thermal stability could be attributed to barrier effect of HfN layer against oxygen diffusion into HfO2/Si interface, which effectively suppresses the growth of IL during high temperature RTA

FGA 1000oC RTA

High temperature annealing effect

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

0.95 nm EOT and low gate leakage (9.7X10-5A/cm2 @VFB+1V and 1.3X10-3A/cm2 @VFB-1V ) are achieved in HfN/HfO2 gated nMOSFET

Scalability of HfN/HfO2 gate stack (MOSFET)

(J.F. Kang et al, EDL 26 ,2005;)

IL ~0.8 nm

High temperature annealing effect

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Well-behaved device performances are achieved in the

0.95 nm EOT nMOSFET (J.F. Kang et al, EDL 26, p.237,

2005)

High temperature annealing effect

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of HfN/HfO2 gate stack

TDDB• Polarity dependent TDDB had been reported

in devices with high-k dielectrics (*,**,***)

• Two mechanisms were proposed for TDDB Interfacial layer initiated breakdown

Bulk layer initiated breakdown

• E-field dependent TDDB will be shown

*R. Degraeve, et all; IRPS 2003.

** Wei Yip Loh, et all; IEDM 2003.

*** Y. H. Kim, et all; Device Research Conference,

2003.

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of HfN/HfO2 gate stack

Intrinsic TDDB characteristics (J.F. Kang et al, submitted to T-ED)

Nearly constant slopes for different areas are the indication of the intrinsic TDDB (A. S. Oates, IEDM, p.923, 2003 )

Observed TDDB in the HfO2 gate stack

fabricated by a high temperature process is intrinsic

101 102 103

-3

-2

-1

0

1 CVS (Gate Injection)Vg=-3.1V

50x50m2

2.15

Ln(-

Ln(1

-F))

Time[s]

2.11

100x100m2

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of HfN/HfO2 gate stack

E-field dependent TDDB (J.F. Kang et al, submitted to T-ED)

Under low E-fields, constant weibull slope indicates IL initiated breakdown

Under high electric field, the E-field dependent weibull slope indicates bulk initiated breakdown

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of HfN/HfO2 gate stack

E-field dependent TDDB (J.F. Kang et al, submitted to T-ED)

Under high E-fields, hole trapping behavior was observed

Under low E-fields, electron trapping behavior was observed

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of HfN/HfO2 gate stack

E-field dependent TDDB (J.F. Kang et al, submitted to T-ED)

High energetic holes or

electrons trapping dominate

the dielectric breakdown (K.

Torii et al, in IEDM p.129-132,

2004 )

Under a high CVS, hole

trapping in HfO2 bulk is

dominant

Under a low CVS, electron

trapping in IL layer is

dominant due to the higher E-

field in IL layer based on

Gauss law εILEIL=εBulkEBulk

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of HfN/HfO2 gate stack

BTI (J.F. Kang et al, submitted to T-ED)

Under positive

stressing,

negligible Vt shifts

were observed both

in nMOS and pMOS

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of HfN/HfO2 gate stack

BTI (J.F. Kang et al, submitted to T-ED)

Under negative

stressing, significant

Vt shifts were

observed both in

nMOS and pMOS

devices

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Vt shifts is bias polarity dependent for

nMOSFET

Reliability of HfN/HfO2 gate stack

BTI (J.F. Kang et al, submitted to T-ED)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Vt shifts is bias polarity dependent for

pMOSFET

Reliability of HfN/HfO2 gate stack

BTI (J.F. Kang et al, submitted to T-ED)

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

•DCIV indicates increasing interfacial traps under NBT;•Increasing hysteresis indicates the generation of new bulk traps during NBT stressing

Reliability of HfN/HfO2 gate stack

NBTI in pMOS

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

NBTI well fitted by R-D model was observed (S. Zafar et al, VLSI’04 p.208)

Intrinsic NBTI similar to SiO2-devices could be attributed to the

breaking of Si-H bonds followed by the H species diffusion

IL HfO2 HfN

H

H

Si—H

Si+—

Si+—

Si-H h Si H 2 2

H HN t D N xd d d d

Reliability of HfN/HfO2 gate stack

NBTI in p-MOS

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

At room temperature, a “turn-around” phenomenon was observed. (left)Negative Vt shifts was observed and shows strong dependence on temperature and electrical field. (right)

Reliability of HfN/HfO2 gate stack

PBTI in n-MOS (N. Sa et al, EDL 26, p.610, 2005 )

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

The increased S with stressing time indicates the increased interfacial trap density PBTI fitted by R-D model was observed and the slop was ~0.6 corresponding to the process of the charged species diffusion

Reliability of HfN/HfO2 gate stack

PBTI in n-MOS (N. Sa et al, EDL 26, p.610, 2005 )

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Intrinsic PBTI fitted by R-D model is observed PBTI can be explained by the breaking mechanism

of Si-O bonds in IL induced by the injected electrons

Reliability of HfN/HfO2 gate stack

PBTI in n-MOS (N. Sa et al, EDL 26, p.610, 2005 )

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

The breaking mechanism of Si-O bonds induced by the injected electrons was confirmed by the measurement on activation energy

Reliability of HfN/HfO2 gate stack

PBTI in n-MOS (N. Sa et al, EDL 26, p.610, 2005 )

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Introduction Reliability characteristics of ultra

thin gate dielectricsHfO2 gate stackHigh temperature annealing effectTDDB, PBTI, and NBTI

SiON in pMOS Dynamic NBTI S/D bias effect on NBTI

Summary

Outline

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

•Frequency dependent NBTI @ AC stressing

Reliability of SiON gate dielectric

DNBTI characteristics

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

•Frequency dependent NBTI is related to the generation of interface traps

Reliability of SiON gate dielectric

DNBTI characteristics

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Process of Nit

generation and passivation associated with Si-H bonds meets the R-D model in DC and AC modes

Reliability of SiON gate dielectric

DNBTI characteristics

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Plasma SiON

HSi—Si—H

Si—H

(a)

Si—Si—HSi—

N

N

N

N

N

(b)

NH

H N

Diffusion front

H

Si/SiON

Distance into oxide

Increasing time

SiON/poly

N

N poly

Origin of frequency dependent DNBTI could be attributed to the nitrogen trapping effect on diffused H species

The trapped H species will not be responsible for the re-passivation of Si-H bonds during recover phase

Reliability of SiON gate dielectric

DNBTI characteristics

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of SiON gate dielectricS/D bias effect on NBTI

In low Vds region, NBTI is consistent with one predicted by R-D model (S. Mahapatra et al, EDL 51, p.1371, 2004)

Anomalous E-field dependent NBTI was observed in high Vds region

More severe NBTI with S/D bias was observed in the short channel devices

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Reliability of SiON gate dielectricS/D bias effect on NBTI

Time evolution of △Vth

obeys a power law depicted by generalized reaction-diffusion (R-D) model

The mechanism involving the release of hydrogen from Si-H bonds followed by H species diffusion is responsible for the NBTI» We guess that the energetic holes are

responsible for the anomalous E-field dependence of NBTI

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

•S/D bias causes the formation of energetic holes in the channel inversion layer;

• Energetic holes are captured by Si-H bonds causing weakened Si-H bond;

•Additional energies of the captured holes causes Si-H bond breaking

Mechanism of S/D bias enhanced NBTI

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Summary (1)

High temperature process could

effectively reduce the pre-existing

charge trapping in HfO2 gate stacks

For HfN/HfO2 gate stack, sub-1 nm

EOT could be achieved even after a

high temperature process

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Summary (2)Intrinsic characteristics of TDDB, NBTI

and PBTI could be observed in the

HfN/HfO2 with low pre-existing charge

trapping

The combination of high temperature

process and HfN/HfO2 gate stack is a

potential solution for the application in

sub-45 nm nodes technology

SINANO Workshop, Montreux, Switzerland Sept. 12~16, 2006

Institute of Microelectronics, PKU

Summary (3)

Nitrogen trapping effect on the

diffused H species is critical for DNBTI

S/D bias effect on NBTI is significant,

especially in the short channel devices

New models on reliability evaluation,

including nitrogen effect and S/D bias

effect, is required