Implementing Fast Image Processing Pipelines in a Codesign Environment Accelerate image processing...

-

Upload

britton-jordan -

Category

Documents

-

view

217 -

download

0

description

Transcript of Implementing Fast Image Processing Pipelines in a Codesign Environment Accelerate image processing...

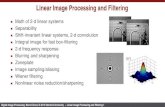

Implementing Fast Image Processing Pipelines in a Codesign Environment

Accelerate image processing tasks through efficient use of FPGAs. Combine already designed components at runtime to implement series of transformations

Heather Quinn, Dr. Miriam Leeser Dr. Laurie Smith KingNortheastern University College of the Holy Cross

Start App HW Init Send Data Median Repgm Edge Det Get Data Display

300ms

.00105 ms per pixel

.00105 ms per pixel

70ms

Median Filter&

Edge Detection

Possible Implementations

1a) swswimplementation

1b) swhwimplementation

1c) hwswimplementation

1d) hwhwimplementation

MedianFilter

EdgeDetect

SW

SW

MedianFilter

EdgeDetect

PadImage

RemovePadding

SW

SW

HW

MedianFilter

EdgeDetect

PadImage

RemovePadding

SW

SW

HW

MedianFilter

EdgeDetect

RPRG

PadImage

FixPadding

RemovePadding

SW

SW

HW

Inputs: a profiled library of image processing components, a pipeline, and an image

Output: an assignment of each component to a hardware or software implementation

Median FilterEdge Detection Profiles

Median to Edge Running Time (with Initialization Time)

0

200

400

600

800

1000

1200

1400

1600

1800

2000

0 1000 2000 3000 4000 5000 6000 7000 8000

Total Pixels

Mill

isec

ond

sw/sw total

hw/hw total

hw/sw total

sw/hw total

The fastest implementation changes with image size If only one component in hardware, choose Edge Detector Different algorithms used at runtime to determine best

implementation. See poster for details.