familia de micro controladores de atmega

description

Transcript of familia de micro controladores de atmega

ELABORACION DE PROGRAMAS

[email protected] DE MICROCONTOLADORES ATMEL AVR DE 8 BITSElaborado por: Ing. Jaime E. VelardeSISTEMASMICROPROCESADOS

[email protected] AVRSon una familia de microcontroladores RISC fabricados por Atmel. La arquitectura fue concebida por dos estudiantes en el Norwegian Institute of Technology; posteriormente refinada en Atmel Norway, la empresa subsidiaria de Atmel fundada por los dos arquitectos del chip.

[email protected] DE 8 BITSLos AVR son CPUs con arquitectura Harvard. Tiene 32 registros de propsito general de 8 bits. Estos registros, los registros de entrada - salida y la memoria de datos forman un solo espacio de localidades, que se acceden mediante operaciones de carga y de almacenamiento.

[email protected] DE LOS AVR

[email protected] PIPELINELos microcontroladores AVR tienen una caera o pipeline con dos etapas (traer y ejecutar), que les permite utilizar un ciclo de reloj en la mayora de instrucciones, lo que los hace relativamente rpidos entre los microcontroladores de 8 bits. El conjunto de instrucciones es ms regular que la de la mayora de los microcontroladores de 8 bits. Sin embargo, no es completamente ortogonal.

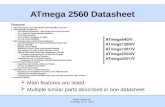

[email protected] DE MICROCONTROLADORESLas instrucciones son utilizadas por diferentes modelos que comparten el mismo ncleo, pero que tienen distintos perifricos y cantidades de RAM y ROM: van desde la serie Tiny, como el ATtiny11 de 1KB de memoria flash, sin RAM y 8 pines, hasta la serie Xmega, como el ATxmega256A3 con 256KB de memoria flash, 16KB de memoria SRAM, 4KB de memoria EEPROM, conversor anlogo digital de 12 bits y 16 canales, comparador analgico, temporizadores, etc. La compatibilidad entre los distintos modelos es de un grado [email protected] (1)

[email protected] ATmega164

[email protected] DE POLARIZACINVoltajes de funcionamiento2.7 - 5.5V (ATmega164P)1.8 - 5.5V (ATmega164PV)200 mA es la corriente mxima en los terminales VCC y GND

[email protected] PARA EL RESETReset en el encendido y externoPara que se active cuando se polarizaO en cualquier instante

[email protected] PARA EL CRISTALRangos de velocidad0 20 MHz (ATmega164P)0 10 MHz (ATmega164PV)

[email protected] DE ENTRADA Y SALIDA PARALELAI/O32 lneas de E/S programablesPrtico A (8 bits)Prtico B (8 bits)Prtico C (8 bits)Prtico D (8 bits)

[email protected] DE ANALGICO A DIGITALADC de 10 bits 8 canales8 canales de un solo terminal2 canales diferenciales con ganancia programable de x1, x10 y x2007 canales diferenciales slo en el encapsulado TQFP

[email protected] ANALGICOIncorporado en el mismo chipLa entrada positiva es AIN0La negativa es AIN1Se puede reemplazar AIN1 por las entradas analgicas ADC0 .. ADC7

[email protected] JTAG PARA SISTEMA DE DEPURACINJTAG (IEEE std1149.1)En la depuracin se tiene acceso a todos perifricosProgramacin de la Flash, EEPROM, Fusibles y Bits de seguridadDepuracin soportada por el AVR Studio

[email protected] A PERIFRICOS SERIALESSPIFull duplexTres lneas para comunicaciones sincrnicasOperacin maestro / esclavoSiete velocidades programablesBandera de fin de la transmisin

[email protected] EXTERNASINT0, INT1 e INT2Pueden activarse por flanco de subida o de bajada, o por nivel de cero lgicoTambin se puede generar por software, si son configurados los terminales como salidas

[email protected] / CONTADORESTimer0 y Timer2 de 8 bits Timer1 de 16 bitsDispone de unidades comparadorasSirven como Generadores de FrecuenciasPoseen relojes pre escalables de 10 bitsPermiten implementar Moduladores por Ancho del Pulso

[email protected] SERIAL CON DOS LNEASTWIOperacin maestro / esclavoPuede trabajar como transmisor o como receptorVelocidad de transferencia hasta 400 KHzLongitud de la direccin de 7 bits para 127 esclavos

[email protected] / TRANSMISORES UNIVERSALES SINCRNICOS Y ASINCRNICOSUSART0 y USART1Full duplexVelocidad de alta resolucinTramas de 5, 6, 7, 8 o 9 bits, con 1 o 2 bits de paradaDetector de errores de velocidad y en la tramaOperacin de maestro o esclavo en comunicaciones sincrnicas

[email protected] DEL RELOJCLOCKHabilitacin de la seal programando el fusibleIncluye como fuente al oscilador interno RCSe puede utilizar el sistema pre escalable para realizar la divisin del reloj

[email protected] POR CAMBIO DE ESTADO INTERRUPCIONES EXTERNAS ADICIONALESCambios entre PCINT0 y PCINT7 se registra en PCI0Cambios entre PCINT8 y PCINT15 se registra en PCI1Cambios entre PCINT16 y PCINT23 se registra en PCI2Cambios entre PCINT24 y PCINT31 se registra en PCI3

[email protected] DE BLOQUES