Erlend Bolle 1,Michael Rissi 1, Michelle Böck 1, Jo Inge Buskenes 1, Kim-Eigard Hines 1, Ole...

-

Upload

stephen-briggs -

Category

Documents

-

view

212 -

download

0

Transcript of Erlend Bolle 1,Michael Rissi 1, Michelle Böck 1, Jo Inge Buskenes 1, Kim-Eigard Hines 1, Ole...

Erlend Bolle1,Michael Rissi1, Michelle Böck1, Jo Inge Buskenes1, Kim-Eigard Hines1, Ole Dorholt1, Ole Røhne1, Steinar Stapnes1,2,

Jan G. Bjaalie3, Arne Skretting4

1Universitet i Oslo, Norway2CERN, Geneva, Switzerland

3Department of Anatomy & CMBN, Oslo, Norway4Rikshospitalet-Radiumhospitalet Medical Center, Oslo, Norway

COMPET Electronics and Readout

Detector characteristics

• Number of channels:– 600 LYSO crystals– 400 WLS elements

• Light-yield:– LYSO speed: 40 ns– LYSO+MPPC: 1300 p.e./511 keV– WLS+MPPC: less than 10%

• MPPC gain: ~1E6 (0.16 pC/p.e.)• Event rate: 10 Mcps• Expected multiplicity: 20 hits/event

Performance considerations• Detector granularity

– Usability floor: e+ flight and γ-pair accolinearity • Energy resolution

– Determines WLS-coordinate resolution– Important for handling Comptons

• Time resolution– Disentangle close-in-time events

• Maximize useful data throughput– Kinematic studies– Suppress singles, pileup events

• Gain stability– Monitor rate and spectrum, slow control HV

• Mechanical precision, stability– Not to be taken for granted…

Project constraints

• Affordability– Exclude high-speed ADC modules– Exclude custom ASIC development– Use standard “office grade” components if possible– Design, build in-house electronics if necessary

• Maintainability– Modular design– Interchangeable parts– Automatic calibration

• Scalability: prototype tests to a few kChannels

System overview

Analog preamplifier

Discriminator Virtex 5Readout FPGA

LVDS

Virtex 5Trigger FPGAEmbedded system

Analog preamplifier

Discriminator Virtex 5Readout FPGA

LVDS

serial link

serial link

UDP/IP

UDP/IP

1Gbp

s Sw

itch

Com

pute

r Far

m

HV supplyTCP/IP

clk

clk

UDP/IP

data

data

slow control

6

Data Acquisition

AnalogElectronics FPGAsDigital

Electronics

010010..

011110..

AnalogElectronics FPGAsDigital

Electronics

Coincidence Unit (FPGA)

Vthr

7

Front-end electronicsClassic Approach• Standard shaping

– Fast channel (trigger)– Slow channel (energy)

• ADC for conversion

Time Over Threshold• Use Time Over Threshold (TOT)

information• No ADC needed!• Fast digitization using FPGA• Timestamping• No trigger needed

Vthr VthrD

iscr

imin

ator

ADC

Time-over-threshold front-end

• Folded cascode topology

• Constant current reset• Bias current budget:

15mA/channel• All-discrete parts!

Readout system: FPGA

Fast Digitizer Parameterization Filter Event Builder Ethernet

• 1Gs sampling rate• Continuously

sampling• No external

trigger needed!

• Extract time and amplitude information

• TDC/QDC

• Incremented with each global coincidence

• All events tagged with global event number

• 1Gb/s link• UDP data

packets

SS

Data Flow

FPGAFPGA

FPGAFPGA

FPGA

Trigger

Rate: 10 McpsEvent: 4 LYSO hits,

4*4 WLS hitsSize: 4 byte/hit-> 1GBps

Trigger suppression: 40%-> 400MBps

PCPC

PCPC

PCPC

Per PC: 50 MBps(after event building andZlib compression)

1GbpsUDP

SSD: up to >500 MBpsMagnetic: 80 MBps(more than x10 in price…)

Imaging 2010, Stockholm 12

HV supply

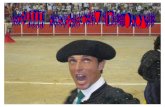

• 400 HV channels• 1mV precision• Mounted in a 3-unit rack• Picture of cards and rack

• Output to 100V• Setting to 1mV precision• 400 Channels• 3U rack mount• Ethernet control

13

Test Setup• 1 LYSO (3×3×100mm3)• 5 WLS (1×30×80mm3)• 6 MPPC (3×3mm2)• Ga-68 source for

coincidence measurement

• Tagger with LYSO(2×2×10mm3) readout by MPPC

• COMPET readout

14

Proof of Concept

• Acquired with the full COMPET readout chain• Coincidence part of readout• Non-optimal light collection (poor optical contact)

15

Calibration/linearity

0 100 200 300 400 500 600 7000

100

200

300

400

500

600

700

800

900

Series1

Ba-133Cs-137

Status and outlook

• System design:– Highly scalable– Cost effective

• Analog front-end:– Single channels tested– 16-channel board assembled, ready for tests

• FPGA/Ethernet DAQ– Single FPGA system tested (self-triggered mode)– Trigger- and interface being specified

• HV system implemented