Endcap Trigger Emulation

description

Transcript of Endcap Trigger Emulation

Endcap Trigger Emulation

Xin Wang

2

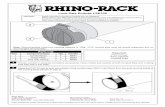

FEE

DSM0

DSM1

DSM2

720 towers

90 trigger patches

12 ‘half’ jet patches

0.3x1 or 0.6x1

2 endcap halves

Raw ADC from DAQ file

To last DSM board

Processing of ADC to L0 trigger decision

6 channels from BARREL, each with 5-bit Esum

3

1

4

5

8

9

12

2

3

6

7

10

11

Endcap structure: towers -> trigger patches ->half jet patches ->endcap halves

4

FEE

HT 6-bit

Emulated from ADC

Real trigger data

Emu-Real difference 3% mismatch

5

FEE

TP 6-bit

Emu-Real difference

Emulated from ADC

Real trigger data

mismatch

6

BARREL ENDCAP

Etotal (B+E)

Barrel

Endcap

Etot (E+B)

Etot energy in DSM channels Etot energy in DSM channels

Etot energy in DSM channels

mismatch~80%

~7%

Etot ENERGY calculation from ADC & trig data

Trig dataADC emul

Trig dataADC emul

Trig dataADC emul

7

Emulated Real data

Emu-Real difference

Etot BIT calculation from ADC & trig data

8

Conclusion

•All L0-bits for ENDCAP can be emulated for M-C

•Code verified against real events for DSM0,1,2

•More QA histos developed ported to online (PPlot)

•Limitation: works for predefined time stamp (range)

9

BACKUP

10

DSM0

11

DSM1

1 2

12

FEE

DSM0

DSM1

DSM2

720 towers, each with 12-bit raw ADC from DAQ file

90 trigger patches, each with 12-bit ADC( 6-bit TP + 6-bit HT)

12 DSM0 channels, each with 16-bit ( 9 or 10-bit TPsum, 2-bit HT, 2-bit TP, 2-bit HTTP)

2 DSM1 channels, each with 16-bit ( 5-bit Esum, 1-bit HTTPthr, 1-bit TPthr, 2-bit JP, 2-bit HT)

6 channels from BARREL, each with 5-bit Esum

![current status of LHC , ATLAS - University of Tokyo · 2004-07-29 · current status of LHC , ATLAS • LHC & ATLAS overview [ by M. Ishino ICEPP ] • LVL1 Endcap-Muon Trigger Electronics](https://static.fdocuments.in/doc/165x107/5e88af42d64a9439b26f0327/current-status-of-lhc-atlas-university-of-tokyo-2004-07-29-current-status.jpg)